MOS器件物理基礎——基本概念

PART01

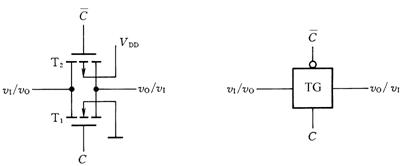

MOSFET 開關

在研究MOSFET的實際工作原理前我們來考慮這種器件的一個簡化模型,以便對晶體管有一個感性認識:我們預期它有什么樣的特性以及特性的哪些方面是重要的。

圖1是一個n型MOSFET的符號,圖中表示了三個端口:柵(G)、源(S)和漏(D)。這種器件是對稱的,因而源和漏可以互換。作為開關工作時,如果柵電壓VG是高電平,晶體管把源和漏連接在一起;如果柵電壓為低電平,則源和漏是斷開的。

即使對于這樣簡單的描述,我們還是必須回答幾個問題。VG取多大值時器件導通?換句話說,閥值電壓是多少?當器件導通(或斷開)時,源和漏之間的電阻有多大?這個電阻與端電壓的關系是怎樣的?總是可以用簡單的線性電阻來模擬源和漏之間的通道嗎?是什么因素限制了器件的速度?

雖然所有這些問題都是在電路級產生的,但是僅通過分析晶體管的結構和物理特性就可以對其作出回答。

圖1

PART02

MOSFET的結構

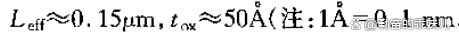

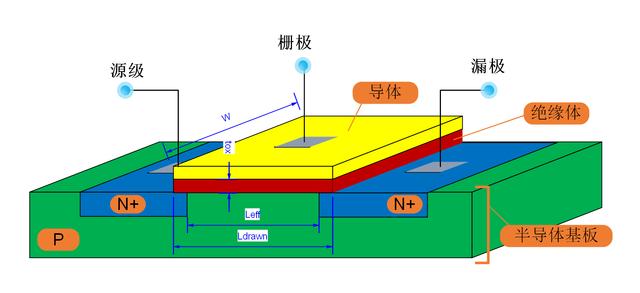

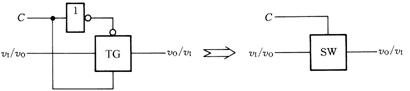

n型MOS(NMOS)器件的簡化結構如圖2所示。器件制作在p型襯底上(襯底也稱作bulk或者body),兩個重摻雜n區形成源端和漏端,重摻雜的(導電的)多晶硅區(通常簡稱poly)作為柵,一層薄SiO2使柵與襯底隔離。器件的有效作用就發生在柵氧下的襯底區。注意,這種結構中的源和漏是對稱的。

圖2

源漏方向的柵的尺寸叫柵長L,與之垂直方向的柵的尺寸叫做柵寬W。由于在制造過程中,源/漏結的橫向擴散,源漏之間實際的距離略小于L。為了避免混淆,我們定義Leff=Ldrawn-2L eff,式中Leff稱為有效溝道長度,Ldrawn是溝道總長度,而LD是橫向擴散的長度。正如在以后我們將會看到的那樣,Leff和氧化層厚度tox對MOS 電路的性能起著非常重要的作用。因此,MOS 技術發展中的主要推動力就是不使器件的其它參數退化而一代一代地減小這兩個尺寸。后續文章這兩個尺寸的典型值為

。后續文章以后將用 L 來表示有效長度。

。后續文章以后將用 L 來表示有效長度。

既然MOS結構是對稱的那么為什么還要將一個n區稱為源而另一個n區稱為漏呢?如果將源定義為提供載流子(NMOS器件中為電子)的終端而漏定義為收集載流子的終端這一點就很清楚了.因此,當器件三個端子的電壓變化時,源和漏的作用可以互換。在本章后面的習題中給出了這些概念的練習。

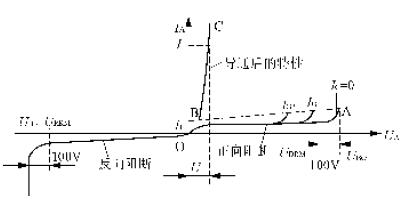

到目前為止,我們還沒有考慮器件的襯底。實際上,襯底的電位對器件特性有很大的影響。也就是說,MOSFET 是一個四端器件。由于在典型的 MOS 工作中,源/漏結二極管都必須反偏,所以我們認為 NMOS 晶體管的襯底被連接到系統的最低電壓上。例如,如果一個電路在03V工作,則 Vsub.NMOS =0。實際的連接如圖3 所示通常通過一個p+歐姆區來實現。

圖3

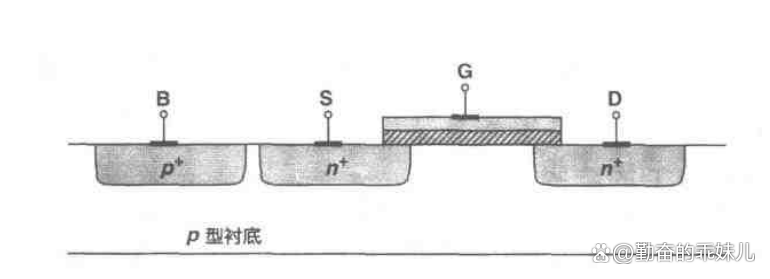

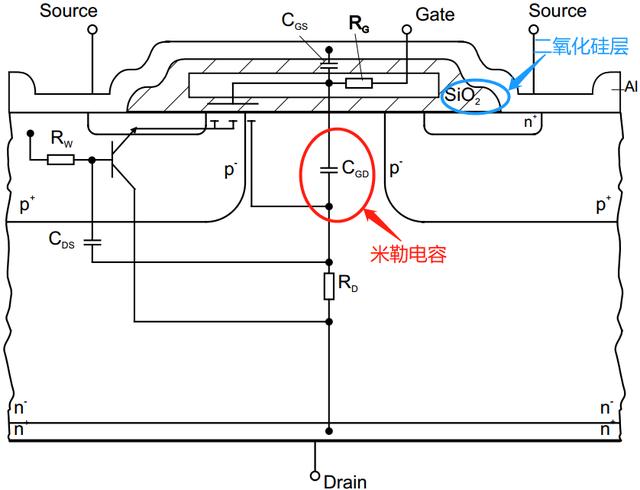

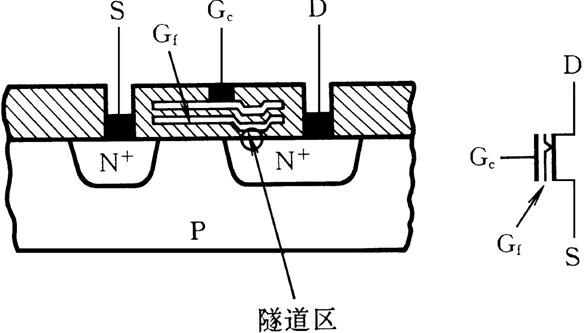

在互補MOS(CMOS)技術中同時用到NMOS和PMOS。從簡單的角度來看,PMOS器件可通過將所有摻雜類型取反(包括村底)來實現,如圖4(a)所示。但實際生產中NMOS和PMOS器件必須做在同一晶片上,也就是說做在相同的村底上。由于這一原因,其中某一種類型的器件要做在一個“局部襯底”上,通常稱為“阱”。現在大多數 CMOS工藝中PMOS器件做在n阱中(圖4b))。注意n阱必須接一定的電位,以便 PMOS管的源/漏結二極管在任何情況下都保持反偏。在大多數電路中,n阱與最正的電源供給相連接。為了簡化,有時分別稱NMOS和PMOS器件為“NFETs”和“PFETs”。

圖4(b)指出了NMOS和PMOS 晶體管一個有意義的區別每個PFETs可以處于各自獨立的n阱中而所有 NFETs則共享同一襯底。PFETs的這種靈活性在一些模擬電路中被應用。

圖4

PART03

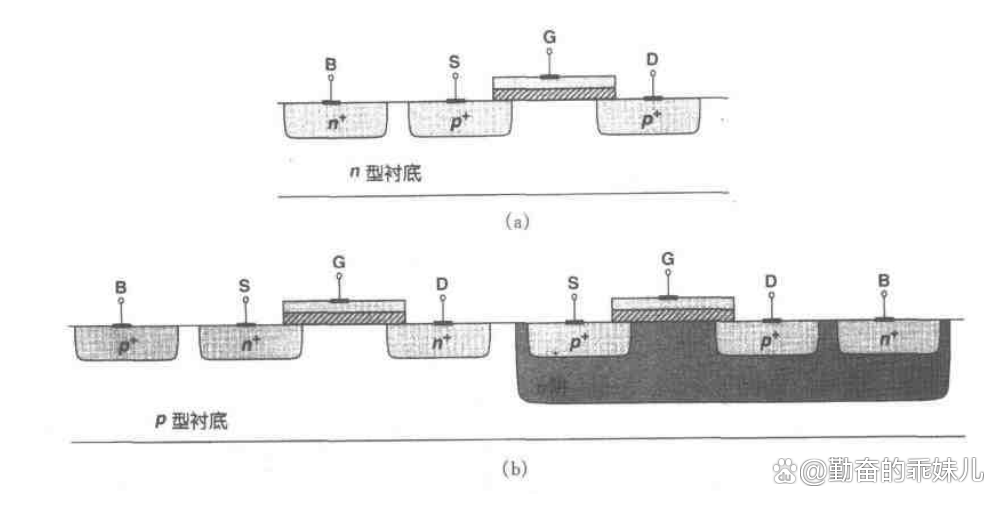

MOS符號

用來表示NMOS和PMOS 晶體管的電路符號如圖5所示。圖5(a)中的符號包括晶體管的所有四個端子,其中襯底用 B(bulk)而不是用S來表示,以免與源極相混淆。PMOS 器件的源極放在頂端,這是為了直觀起見,因為源極比柵極的電壓高。由于在大多數電路中,NMOS和PMOS器件的村底端子分別接地和 VDD ,所以我們畫圖時通常省略這一連接圖5(b)在數字電路中慣上用圖 5(C)所示的開關符號來表示兩種 MOS管。但是我們更喜歡圖5(b)的表示,因為明確區分源和漏對于理解電路的工作被證明是很有幫助的。

圖5

-

MOSFET

+關注

關注

144文章

7088瀏覽量

212729 -

NMOS

+關注

關注

3文章

290瀏覽量

34295 -

晶體管

+關注

關注

77文章

9635瀏覽量

137852 -

PMOS

+關注

關注

4文章

244瀏覽量

29494 -

MOS器件

+關注

關注

0文章

9瀏覽量

6428

發布評論請先 登錄

相關推薦

MOSFET的結構、電學符號和電學特性

MOSFET的基本結構與工作原理

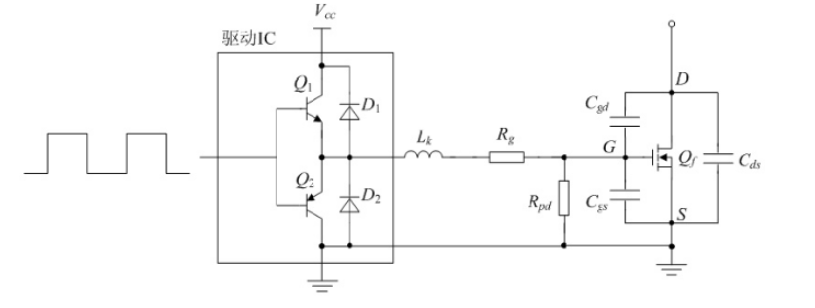

基于MOSFET內部結構設計優化的驅動電路

單向晶閘管的結構、符號

基于圖元結構的電氣早圖符號識別

MOSFET結構和符號及教程摘要

MOSFET的結構和電路符號

MOSFET的結構和電路符號

評論