MOS器件物理基礎(chǔ)——MOS的I/V特性

分析MOSFETs 中電荷的產(chǎn)生和傳輸建立它們與各端電壓之間的函數(shù)關(guān)系。推導(dǎo)出I/V特性方程。這樣就能夠?qū)⒊橄蠹墑e從器件物理級提升到電路級。

PART01

閥值電壓

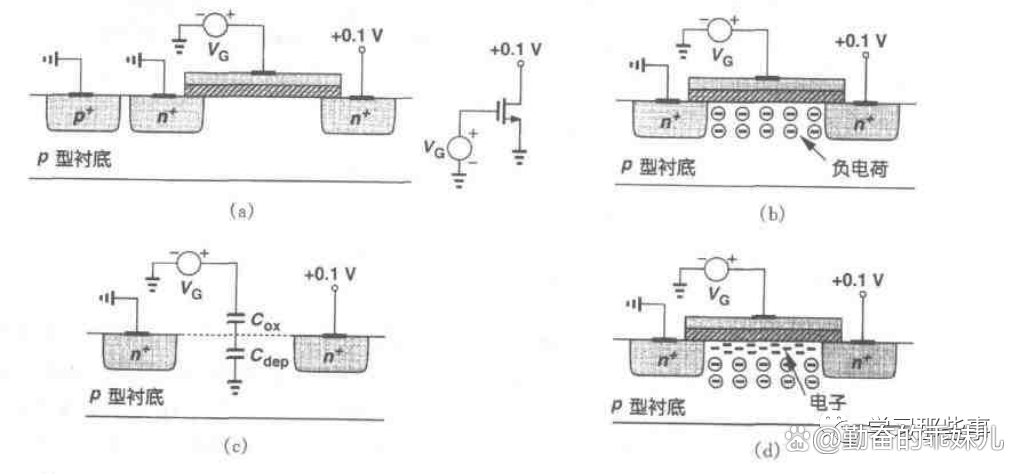

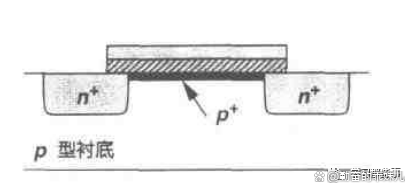

考慮如圖1(a)所示的NFET。當(dāng)柵壓VG從0V上升時(shí)會發(fā)生什么情況?由于柵和襯底形成一個(gè)電容器,所以當(dāng) VG逐漸升高時(shí),p襯底中的空穴被趕離柵區(qū)而留下負(fù)離子以鏡像柵上的電荷。換句話說,就是形成了一個(gè)耗盡層圖1(b)。在這種情況下由于沒有載流子而無電流流動。

圖1(a)由柵壓控制的MOSFET;(b)耗盡區(qū)的形成;

(c)反型的開始 (d)反型層的形成

隨著VG的增加,耗盡層寬度和氧化物與硅界而處的電勢也增加。從某種意義上講,這樣的結(jié)構(gòu)類似兩個(gè)電容的串聯(lián):柵氧化層電容和耗盡區(qū)電容(圖1(c))。當(dāng)界面電勢達(dá)到足夠高時(shí),電子便從源流向界而并最終流到漏端。這時(shí),源和漏之間的柵氧下就形成了載流子“溝道”,同時(shí)晶體管“導(dǎo)通”。我們也稱之為界面“反型”。形成溝道所對應(yīng)的VG稱為“閥值電壓”,VTH。如果 Vc進(jìn)一步升高,則耗盡區(qū)的電荷保持相對定恒定,而溝道電荷密度繼續(xù)增加,導(dǎo)致源漏電流增加。

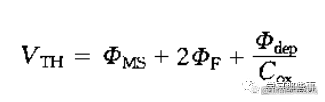

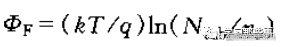

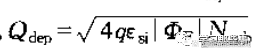

實(shí)際上,導(dǎo)通現(xiàn)象是柵電壓的增函數(shù),這就使得明確地定義VTH變得比較困難。在半導(dǎo)本物理學(xué)中,NFET的VTH通常定義為界而的電子濃度等于p型襯底的多子濃度時(shí)的柵壓可以證明:

式中 是多晶硅柵和硅襯底的功函數(shù)之差,

是多晶硅柵和硅襯底的功函數(shù)之差, ,q是電子電荷,Nsub是襯底的摻雜濃度,Qdep是耗盡區(qū)的電荷,Cox是單位面積的柵氧化層電容.由pn結(jié)理論可知,

,q是電子電荷,Nsub是襯底的摻雜濃度,Qdep是耗盡區(qū)的電荷,Cox是單位面積的柵氧化層電容.由pn結(jié)理論可知, ,其中表示硅的介電常數(shù)。由于Cox在器件和電路計(jì)算中經(jīng)常出現(xiàn),所以記住它的值是有幫助的:這樣,對于其它的氧化層厚度,Cox的值可以依比例確定。

,其中表示硅的介電常數(shù)。由于Cox在器件和電路計(jì)算中經(jīng)常出現(xiàn),所以記住它的值是有幫助的:這樣,對于其它的氧化層厚度,Cox的值可以依比例確定。

在實(shí)際中,由上式得到的“本征”闕值電壓可能不適用于電路設(shè)計(jì),舉例來說VTH=0因而VG≥0時(shí)器件不會大斷。因此,在器件制造過程中通常通過向溝道區(qū)注入雜質(zhì)來調(diào)整闕值電壓,其實(shí)質(zhì)是改變氧化層界面附近襯底的摻雜濃度。例如,如圖2所示如果形成了p+薄層,那么就需要增加?xùn)艍菏勾藚^(qū)域耗盡。

圖2 用來改變閥值電壓的 p +摻雜劑的注人

以上的定義不能直接適用于 VTH的測量。在圖1(a)中,只有漏極電流可以表示器件的通或斷,因此不能揭示 VGS為何值時(shí)界面的電子濃度等于p型襯底的多子濃度。結(jié)果,給借助 I/V 測量來計(jì)算VTH帶來一些不確定性。后面的部分會講到這一點(diǎn),不過在基礎(chǔ)分析中假定當(dāng) V GS ≥VTH時(shí)器件會突然導(dǎo)通。

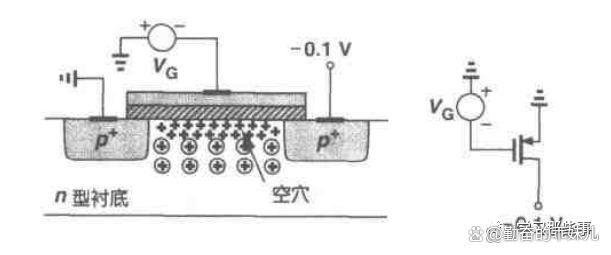

PMOS器件的導(dǎo)通現(xiàn)象類似于NFETs,但是其所有的極性都是相反的。如圖3 中所示,如果柵-源電壓足夠“負(fù)”在氧化層-硅界面就會形成一個(gè)由空穴組成的反型層,從而為源和漏之間提供了一個(gè)導(dǎo)電通道。

圖3 PPET反型層的形成

-

電容器

+關(guān)注

關(guān)注

63文章

6101瀏覽量

98449 -

MOSFET

+關(guān)注

關(guān)注

142文章

6936瀏覽量

211744 -

MOS

+關(guān)注

關(guān)注

31文章

1199瀏覽量

92906 -

電荷

+關(guān)注

關(guān)注

1文章

576瀏覽量

36026 -

MOS器件

+關(guān)注

關(guān)注

0文章

9瀏覽量

6419

發(fā)布評論請先 登錄

相關(guān)推薦

MOS管的種類、結(jié)構(gòu)及導(dǎo)通特性詳解

詳解MOS管驅(qū)動電路

詳解MOS管驅(qū)動電路

挖掘MOS管電路應(yīng)用的特性

偏微分方程式數(shù)值解之計(jì)算機(jī)Fortran算法詳解附圖(續(xù)i)

MOS管的特性是什么

利用Van der Pol方程分析MOS LC差分振蕩器

MOS管參數(shù)詳解及驅(qū)動電阻選擇

含受控源電路例題網(wǎng)孔分析詳解(方程和矩陣)

詳解MOS的I/V特性方程

詳解MOS的I/V特性方程

評論