在為 5G 應(yīng)用設(shè)計(jì)電源系統(tǒng)時(shí),設(shè)計(jì)人員必須考慮此類應(yīng)用固有的寬頻率范圍,從穩(wěn)壓器中的中頻到 FPGA

內(nèi)核中的高時(shí)鐘頻率。這種端到端的全雙工設(shè)計(jì)對(duì)于優(yōu)化電源、電源轉(zhuǎn)換和配電過(guò)程的性能至關(guān)重要。

本文重點(diǎn)介紹如何實(shí)現(xiàn)高效的供電網(wǎng)絡(luò) (PDN) 設(shè)計(jì)。PDN 由連接到電壓軌和接地軌的所有組件組成,包括電源和接地層布局、無(wú)源元件、IC

以及連接或耦合到主電源軌的任何其他銅質(zhì)元件。在設(shè)計(jì)過(guò)程中,必須考慮 PDN 中組件的寄生行為,因?yàn)檫@會(huì)影響整個(gè)系統(tǒng)行為。

旁路和去耦電容是 PDN 中必不可少的元件。因此,PDN 設(shè)計(jì)中的電容器選擇和放置需要特別考慮,因?yàn)殡娙莶蛔銜?huì)導(dǎo)致系統(tǒng)不穩(wěn)定和性能問(wèn)題。

d耦合和bypass電容器的重要性

旁路電容器用于穩(wěn)壓器模塊(VRM),通過(guò)濾除輸入紋波電流為轉(zhuǎn)換器提供低阻抗電壓源。它們還可以補(bǔ)償電源耦合到 IC

接地連接產(chǎn)生的開(kāi)關(guān)噪聲產(chǎn)生的潛在接地反彈電壓。

在降壓穩(wěn)壓器的輸出端,去耦電容的主要目的是保證輸出電壓(V外) 通過(guò)降低輸出電壓紋波 (?V

保持恒定外).因此,選擇電容以限制?V外到負(fù)載輸入規(guī)格設(shè)定的幅度,同時(shí)還考慮與轉(zhuǎn)換器負(fù)載突然變化引起的電壓變化相關(guān)的限制。

bypass電容器的放置策略

旁路電容器是確保降壓轉(zhuǎn)換器可靠運(yùn)行的最重要元件。放置IC后,旁路電容器是布局中放置的第一個(gè)元件,必須在IC放置后立即布線。由于不正確的布線而導(dǎo)致的額外寄生電感與轉(zhuǎn)換器的開(kāi)關(guān)相結(jié)合,會(huì)產(chǎn)生過(guò)大的電壓尖峰,這可能導(dǎo)致IC故障。

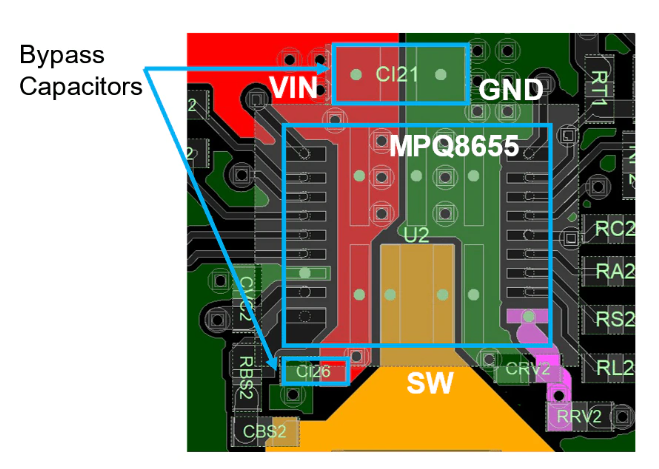

圖1顯示了負(fù)載點(diǎn)(PoL)轉(zhuǎn)換器旁路電容(CI21和CI26)的最佳放置。

旁路電容器環(huán)路中產(chǎn)生的寄生電感可分為兩部分:電容器的寄生電感和電感和IC之間的電流路徑布局產(chǎn)生的電感。由于PCB布局幾何形狀產(chǎn)生的電感相對(duì)于總電感比固有電容器電感更重要,因此設(shè)計(jì)工作應(yīng)重點(diǎn)關(guān)注。

為了最小化環(huán)路電感,旁路電容應(yīng)盡可能靠近IC放置。還應(yīng)使用過(guò)孔將電容器的焊盤(pán)直接連接到電源 (PWR) 和接地 (GND) 網(wǎng)絡(luò),盡可能靠近 IC 引腳,從而最大限度地減少電流路徑。

選擇d耦合****電容器

所需的去耦電容類型和數(shù)量取決于電容在頻域中的行為。去耦電容設(shè)計(jì)用于最大限度地降低VRM的?V外這是由轉(zhuǎn)換器的開(kāi)關(guān)操作產(chǎn)生的,以及以高頻向FPGA/ASIC提供瞬時(shí)電流,直到電源可以響應(yīng)。因此,必須考慮整個(gè)工作頻譜。

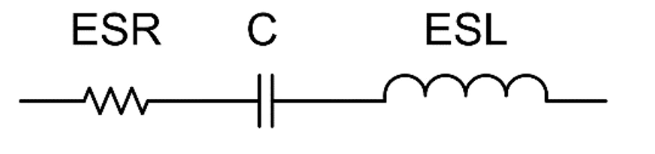

基本電容模型包括三個(gè)關(guān)鍵要素:電容 (C)、等效串聯(lián)電阻 (ESR) 和等效串聯(lián)電感 (ESL),如圖 2 所示。

圖2這就是電容器等效電路模型的樣子。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

ESR由元件中導(dǎo)電元件的阻抗引起,并決定了諧振頻率處的最小阻抗。ESL由流過(guò)電容器的電流的影響產(chǎn)生,并決定諧振頻率。諧振頻率是電容器阻抗曲線中元件開(kāi)始表現(xiàn)得像電感器的點(diǎn),阻抗與頻率成比例地增加。

在低頻(高達(dá)50 kHz)下,降壓轉(zhuǎn)換器具有低阻抗。然而,降壓轉(zhuǎn)換器在高頻下的阻抗主要是感性的。添加到PCB中的每個(gè)電容器都會(huì)降低給定頻率下的PDN阻抗,這意味著精確的放置和選擇可以實(shí)現(xiàn)設(shè)定的目標(biāo)阻抗曲線。因此,通過(guò)從檢測(cè)點(diǎn)進(jìn)行測(cè)量,可以在給定頻率下滿足目標(biāo)阻抗。

目標(biāo)阻抗(Z 目標(biāo) ) 可以用公式 1 計(jì)算:

Z 目標(biāo) = ?V 噪聲 /我 TRANSIENT_MAX (1)

其中 ?V噪聲是最大允許紋波電壓和ITRANSIENT_MAX是轉(zhuǎn)換器必須提供的最大負(fù)載步長(zhǎng)。還可以計(jì)算所需的輸入和輸出電容。

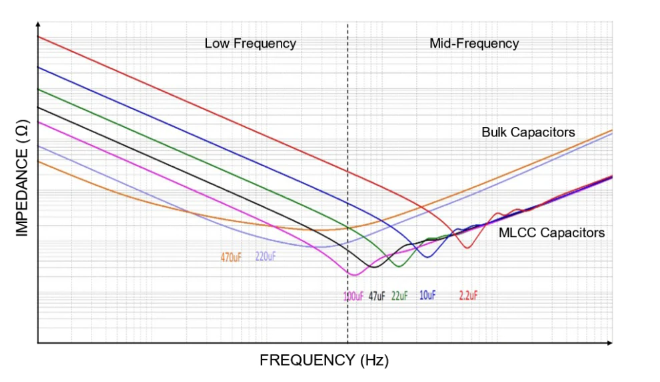

為了將阻抗保持在目標(biāo)水平以下,必須約束設(shè)計(jì)并降低寄生電感。大容量電容器在高達(dá) 10 MHz 的頻率范圍內(nèi)降低阻抗,而 MLCC 電容器在中高頻范圍內(nèi)降低阻抗。

圖3顯示了大容量電容器和MLCC電容器的阻抗頻率特性。

圖3圖中顯示了典型大容量電容器和MLCC電容器的阻抗頻率特性。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

d耦合電容器的布局****策略

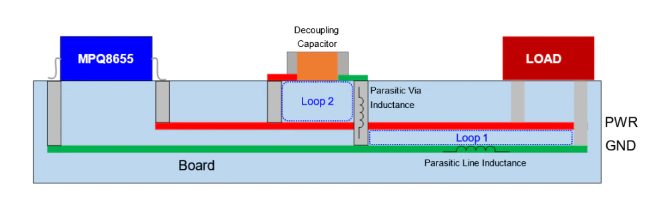

一旦計(jì)算和分析了電容,去耦電容在PCB中的最佳位置就很重要。布局幾何形狀、通孔布局和距離主要影響電源層環(huán)路電感,從而影響PDN響應(yīng)。圖4顯示了轉(zhuǎn)換器、去耦電容和負(fù)載產(chǎn)生的電流環(huán)路。由于這些回路是結(jié)構(gòu)固有的并且不可避免,因此盡可能減少這些回路至關(guān)重要。

圖4電流環(huán)路由轉(zhuǎn)換器、去耦電容和負(fù)載產(chǎn)生。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

環(huán)路1是水平環(huán)路分量,由轉(zhuǎn)換器和去耦電容之間的距離決定。環(huán)路 2 是垂直環(huán)路組件,由將電容器連接到電源層的通孔高度決定。電源層通常放置在PCB的最內(nèi)層。

該測(cè)試板在雙相操作中使用兩個(gè)PoL轉(zhuǎn)換器,V外0.9 V 和最大輸出電流 (I OUT_MAX ) 的 50 A,這是 ASIC/FPGA 電源軌的通用值。可以使用測(cè)試板進(jìn)行不同場(chǎng)景的仿真,以確定電容器的最佳放置。

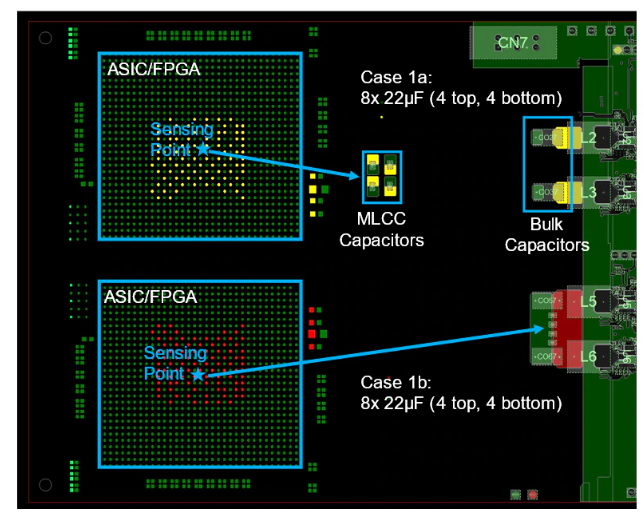

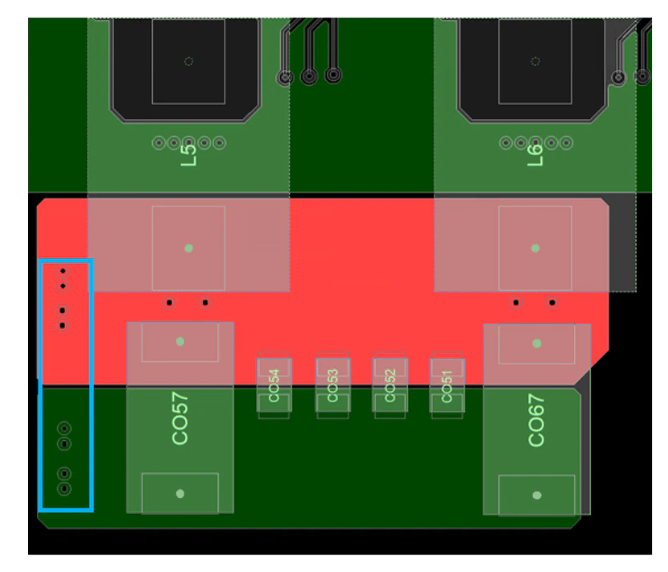

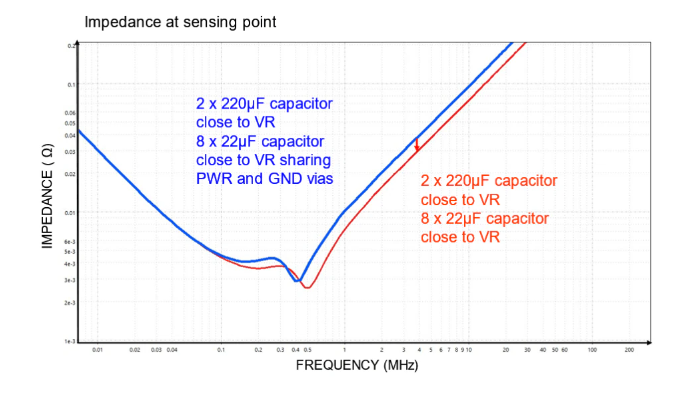

為了評(píng)估最佳電容布局,在ASIC/FPGA中心的板級(jí)檢測(cè)點(diǎn)測(cè)量阻抗。使用公式1的分析,可以使用8 x 22 μF MLCC電容和2 x 220 μF大容量電容實(shí)現(xiàn)VRM阻抗曲線。為了保持穩(wěn)壓器的穩(wěn)定性,大容量電容器緊跟在輸出電感器之后。測(cè)試板考慮了22 μF MLCC電容在外殼1a和案例1b下的不同位置(見(jiàn) 圖5 )。

圖5測(cè)試板說(shuō)明了去耦電容的放置。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

在情況1a中,MLCC電容器放置在ASIC/FPGA之前,從而減小了環(huán)路1的尺寸。在案例1b中,MLCC電容器放置在大容量電容器旁邊,因此MLCC電容器與傳感點(diǎn)之間的距離是案例1a的兩倍。

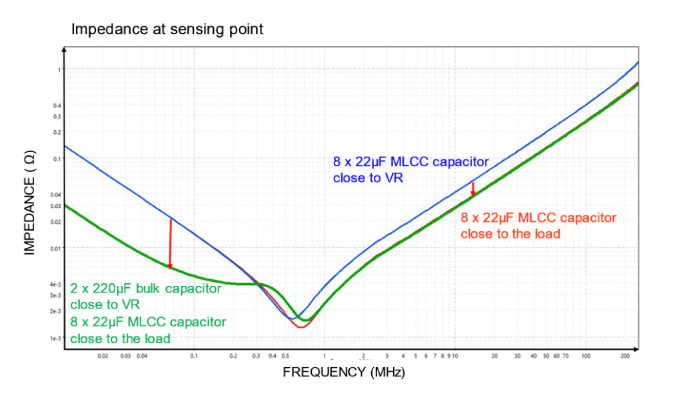

圖6顯示了將大容量電容放置在降壓轉(zhuǎn)換器附近時(shí)的仿真結(jié)果,這導(dǎo)致低頻范圍內(nèi)的阻抗降低(綠色跡線)。將MLCC電容器放置在靠近負(fù)載的位置(紅色跡線)可降低高頻范圍內(nèi)的阻抗,從而使電容器能夠更有效地提供FPGA/ASIC負(fù)載所需的瞬時(shí)電流階躍。

圖6顯示了回路 1 大小變化的測(cè)試結(jié)果。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

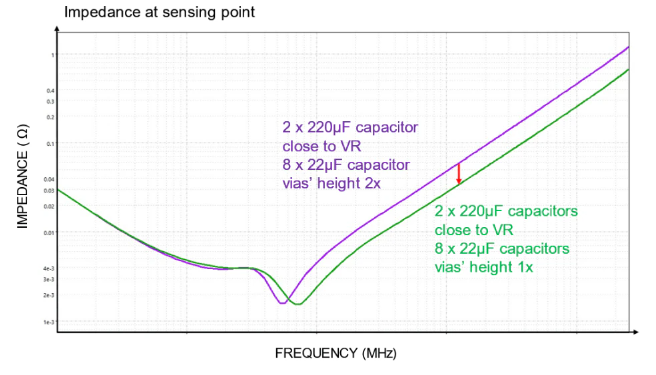

傳統(tǒng)設(shè)計(jì)指南建議將去耦電容放置在PCB的底部,以減小電路板空間,從而提高功率密度。然而,將電容器放置在電路板底部需要更長(zhǎng)的過(guò)孔才能到達(dá)ASIC/FPGA所在的另一側(cè)。這增加了垂直路徑的大小,如圖 4 所示,如環(huán)路 2 所示。

通過(guò)將過(guò)孔高度加倍進(jìn)行了額外的測(cè)試,以分析增加環(huán)路 2 尺寸的效果。圖7顯示了環(huán)路2尺寸變化的測(cè)試結(jié)果,其中觀察到類似的趨勢(shì),通孔高度增加導(dǎo)致中高頻范圍內(nèi)的阻抗增加。

圖7顯示了環(huán)路 2 大小變化的測(cè)試結(jié)果。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

最小化去耦電容中的環(huán)路電感與電容數(shù)量同樣重要。有兩種方法可以實(shí)現(xiàn)降低環(huán)路電感。第一種方法是減小IC和電容器之間的水平距離。第二種方法是通過(guò)將電源層和接地層放置在上層來(lái)降低通孔高度。

在小范圍內(nèi)放置多個(gè)元件以減少電路板空間通常會(huì)導(dǎo)致電容共享過(guò)孔。當(dāng)電容器共享過(guò)孔時(shí),如果不考慮通孔定位和數(shù)量,正確選擇和定位的整體改進(jìn)可能會(huì)顯著降低甚至可以忽略不計(jì)。因此,通孔布局設(shè)計(jì)也是降低環(huán)路阻抗的關(guān)鍵。

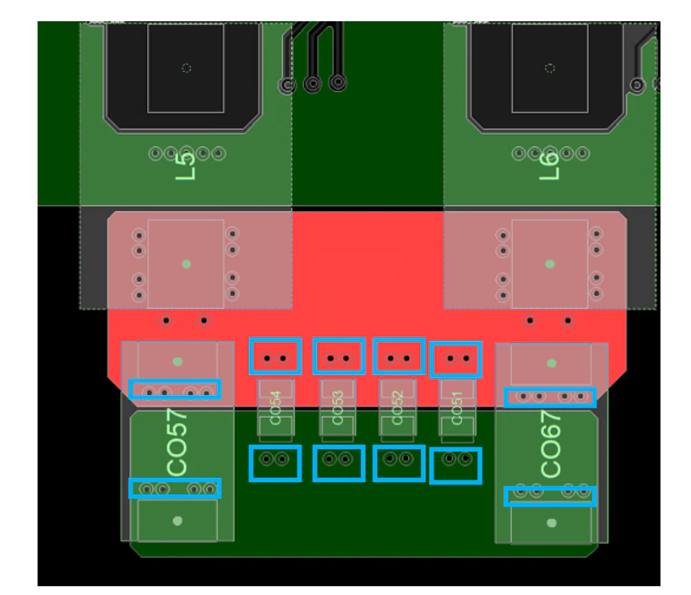

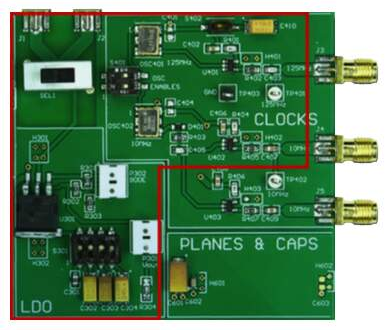

為了分析過(guò)孔定位和數(shù)量的影響,使用電路板進(jìn)行了第二次測(cè)試,通過(guò)放置兩個(gè)通用設(shè)計(jì)建議。在第一個(gè)設(shè)置中,每個(gè)電容都有自己的一組通孔連接到電源和接地層(見(jiàn) 圖8 )。

圖8每個(gè)電容器都有自己的一組電源和接地層過(guò)孔。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

在第二種設(shè)置中,所有電容共用一組位于平面一側(cè)的過(guò)孔(見(jiàn) 圖9 )。

圖9所有電容器共用一組位于平面一側(cè)的過(guò)孔。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

圖10顯示了通孔放置變化的測(cè)試結(jié)果。將過(guò)孔放置在遠(yuǎn)離電容的位置會(huì)增加環(huán)路1的尺寸,從而增加環(huán)路電感。因此,過(guò)孔共享增加了高頻阻抗。

圖10顯示過(guò)孔放置變化的測(cè)試結(jié)果。來(lái)源:?jiǎn)纹娫聪到y(tǒng)

根據(jù)后續(xù)測(cè)試,建議在0805和0603封裝中,大容量電容器至少使用4個(gè)電源通孔和4個(gè)接地過(guò)孔,MLCC電容器至少使用2個(gè)電源過(guò)孔和2個(gè)接地過(guò)孔。過(guò)孔應(yīng)盡可能靠近電容器放置。

整個(gè) PDN

在設(shè)計(jì) FPGA/ASIC 系統(tǒng)或任何需要高電流和快速負(fù)載瞬變的電路時(shí),必須全面考慮 PDN,以優(yōu)化系統(tǒng)性能。快速負(fù)載階躍,例如在FPGA中觀察到的階躍,會(huì)在整個(gè)電路中產(chǎn)生強(qiáng)大的高頻電流。在如此高的頻率下,PDN 中通常可以忽略的寄生元件可能會(huì)突然導(dǎo)致設(shè)備故障。設(shè)計(jì)人員必須注意確保 PDN 的寄生元件最小化。

本文重點(diǎn)介紹如何使用PoL轉(zhuǎn)換器降低VRM去耦電容中的電流路徑引起的寄生阻抗。為了獲得最佳性能,垂直軸和水平軸上的電流環(huán)路應(yīng)盡可能短。將電流環(huán)路放置在盡可能靠近負(fù)載的位置,并將電源走線保持在外層,可有效減少通孔長(zhǎng)度。

適當(dāng)?shù)倪^(guò)孔放置也是降低寄生電感的關(guān)鍵。因此,建議在盡可能靠近每個(gè)電容器焊盤(pán)的位置放置多個(gè)過(guò)孔,以減少過(guò)孔的總寄生電感以及流過(guò)每個(gè)過(guò)孔的電流。

-

電源

+關(guān)注

關(guān)注

184文章

17605瀏覽量

249562 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8639瀏覽量

146895 -

電壓

+關(guān)注

關(guān)注

45文章

5567瀏覽量

115605 -

PDN

+關(guān)注

關(guān)注

0文章

83瀏覽量

22688 -

供電網(wǎng)絡(luò)

+關(guān)注

關(guān)注

0文章

15瀏覽量

7474

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于探頭的快速識(shí)別PDN在線敏感度解決方案

DC–DC 轉(zhuǎn)換器為 GSPS ADC 提供高效輸電網(wǎng)絡(luò)

DC–DC轉(zhuǎn)換器為GSPS ADC提供高效輸電網(wǎng)絡(luò)

GSPS ADC搭配DC-DC轉(zhuǎn)換器,提高輸電網(wǎng)絡(luò)效能

通過(guò)輸電網(wǎng)絡(luò)合探討GSPS ADC性能

怎么基于RFID實(shí)現(xiàn)電能電網(wǎng)?

如何實(shí)現(xiàn)智能電網(wǎng)自動(dòng)化?

如何利用Cyclone FPGA實(shí)現(xiàn)智能電網(wǎng)自動(dòng)化?

如何優(yōu)化供電網(wǎng)絡(luò)?

智能電網(wǎng)如何實(shí)現(xiàn)

電源系統(tǒng)優(yōu)化——深入解讀優(yōu)化高速數(shù)據(jù)轉(zhuǎn)換器的配電網(wǎng)絡(luò)

利用Spice實(shí)現(xiàn)供電網(wǎng)絡(luò)版圖設(shè)計(jì)

震旦ad330pdn

如何實(shí)現(xiàn)高效的供電網(wǎng)絡(luò) (PDN) 設(shè)計(jì)

如何實(shí)現(xiàn)高效的供電網(wǎng)絡(luò) (PDN) 設(shè)計(jì)

評(píng)論