關(guān)于高速串行信號隔直電容的PCB設(shè)計注意點

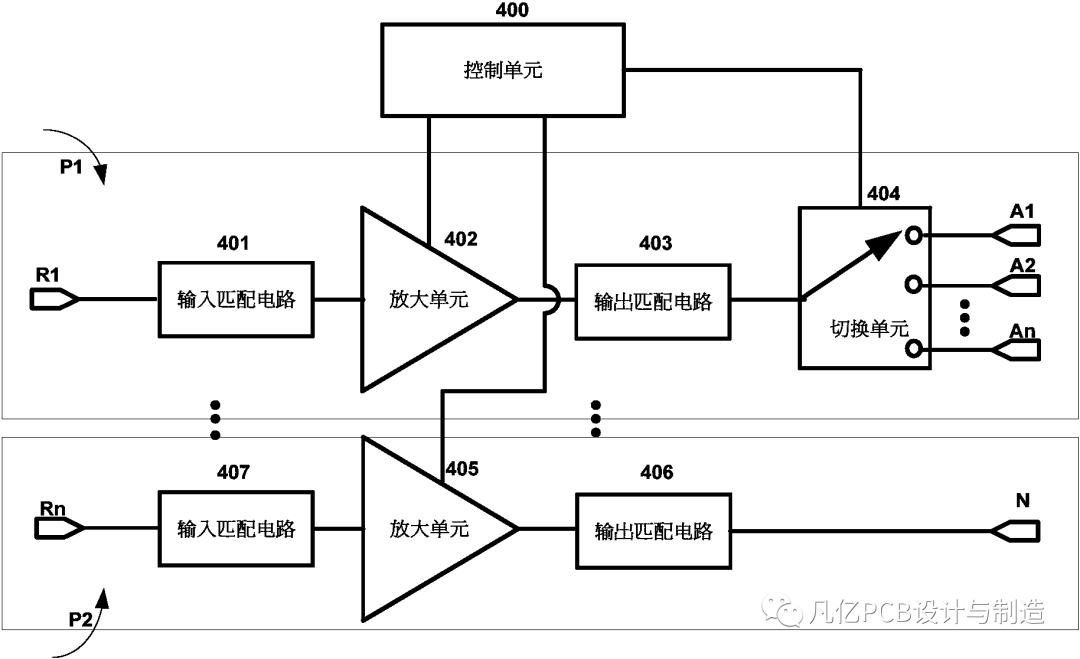

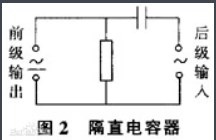

在高速串行信號傳輸中,隔直電容是一種常見的解決信號干擾問題的方法。由于高速信號傳輸時會產(chǎn)生電磁干擾和相鄰信號交叉干擾,隔直電容可以將交流信號通路隔離開來,從而達到保護信號完整性的目的。下面將詳細介紹高速串行信號隔直電容的PCB設(shè)計注意事項。

1. 布局原則

在進行高速串行信號隔直電容的PCB布局時,需要遵循以下原則:

(1)將高速信號線和低速信號線分開布局,且盡可能避開高功率和高噪聲的元器件,如DC/DC轉(zhuǎn)換器、開關(guān)電源等。

(2)串行線兩側(cè)應(yīng)盡量布滿電源層或地層,防止層間耦合干擾。

(3)直線信號線應(yīng)盡可能直線,減少拐彎和仿真。

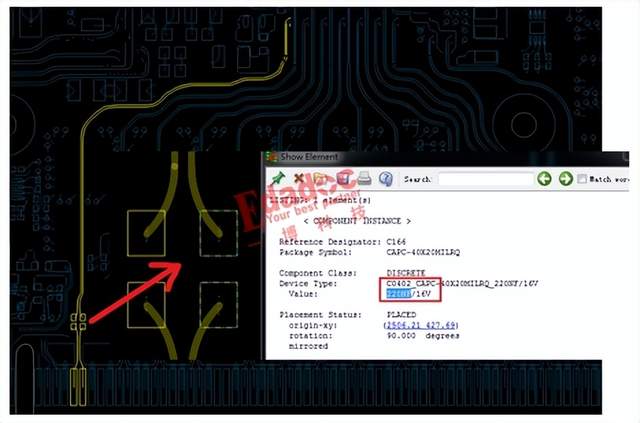

(4)保持隔直電容盡量靠近發(fā)送器和接收器,線路長度盡可能短。

(5)隔直電容應(yīng)固定于信號線的兩端,不要讓它們穿過板上的孔。

2. 隔直電容的選擇

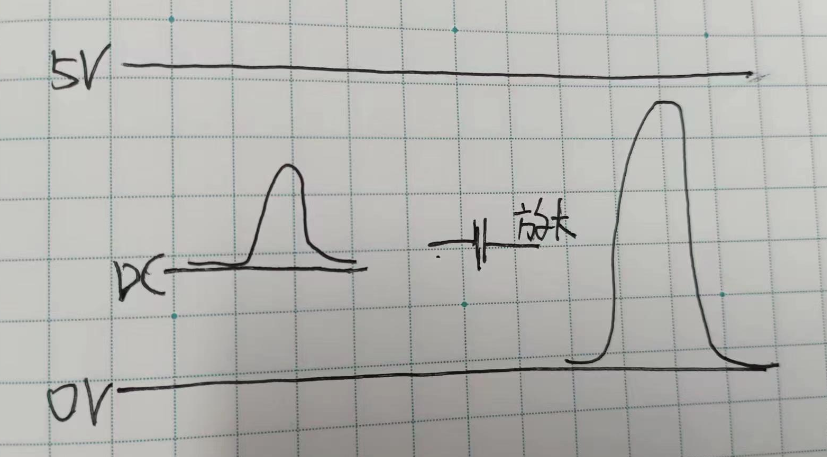

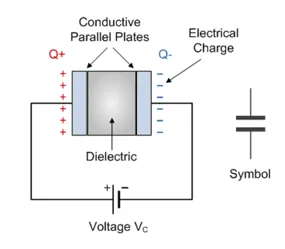

隔直電容是高速傳輸中必需的元器件,它們可以起到過濾掉直流分量的噪聲或使信號通路中的電壓保持穩(wěn)定的作用。因此選擇合適的隔直電容也非常重要。

(1)選用小尺寸電容器,以減小帶寬影響。

(2)選用低ESR、低ESL、高Q值電容器,以減小損耗和降低諧振頻率。

(3)選用高頻響應(yīng)快的電容器,以減小串擾。

(4)了解信號的特性和噪聲源,選擇合適的電容值和數(shù)量。

3. 隔直電容布局

在隔直電容的布局時,需要注意以下幾點:

(1)隔直電容應(yīng)該盡量布在信號線的兩端,保持與信號線平行,避免出現(xiàn)拐彎后造成的系列電感或電容。

(2)為減小隔離電容和相鄰電容的串擾,應(yīng)保持一定距離,并保證相鄰電容的參考地點一致。

(3)為避免鏡像地線模式干擾,在單面布線時,兩個隔直電容不應(yīng)該放在同一條直線上。

4. 線寬和距離

對于高速串行信號線,線寬和距離對信號的傳輸質(zhì)量和芯片的發(fā)熱都有重要影響。以下是應(yīng)注意的線寬和距離:

(1)為了減小串擾和衰減,線寬應(yīng)根據(jù)高速信號的數(shù)據(jù)速率、驅(qū)動電流和板上的損耗,選擇合適的線寬。對于高速信號,線寬應(yīng)該越寬越好,以減小線路阻抗。

(2)高速平面內(nèi)信號線之間的距離對于減小串擾和衰減很重要。在線路設(shè)計時應(yīng)保證不同電路層之間都有合適的間隔。

5. 避免反射

在信號線兩端應(yīng)該盡可能避免反射。因為反射信號會相加或相消,造成信號和噪聲的干擾。反射信號的強度取決于信號線長度、速度以及阻抗匹配程度,因此,為減少信號反射,應(yīng)注意以下幾個方面:

(1)線路長度應(yīng)控制在一定范圍內(nèi)。

(2)對于不同信號線,阻抗應(yīng)匹配,避免出現(xiàn)阻抗不匹配的情況。

(3)針對高速信號,可以使用末端阻抗匹配電路和電源引出電阻來減少反射。

綜上所述,高速串行信號隔直電容的PCB設(shè)計需要綜合考慮信號線的布局、隔直電容的選擇及布局、線寬和距離以及如何避免反射等因素。通過合理的PCB設(shè)計,可以保證高速串行信號傳輸中的穩(wěn)定性和可靠性。

-

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4648瀏覽量

84525 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2227瀏覽量

105132 -

隔直電容

+關(guān)注

關(guān)注

0文章

15瀏覽量

4095

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計的EMC有哪些注意事項

高速串行信號測試時注意事項有哪些

高速PCB設(shè)計中的射頻分析與處理方法

什么是隔直電容,它們?yōu)楹沃匾浚ㄉ希?/a>

什么是隔直電容,它們?yōu)楹沃匾浚ㄏ拢?/a>

PCB設(shè)計時處理去耦電容和旁路電容的注意事項

高速信號pcb設(shè)計中的布局

用隔直電容時候需要注意什么呢?

有想過嗎,高速信號隔直電容為什么是幾百NF量級的?

有想過嗎,高速信號隔直電容為什么是幾百NF量級的?

關(guān)于高速串行信號隔直電容的PCB設(shè)計注意點

關(guān)于高速串行信號隔直電容的PCB設(shè)計注意點

評論