寫在前面

訪問MIPI Allliance官方網站時,發現早在2013年MIPI聯盟就已建立了“MIPI I3C Working Group”,后來在2018年10月發布了I3C規范v1.0版,目前已經更新到了2021年6月的v1.1.1版。作者本人雖然在實際項目上并無I3C的應用,但出于對新事物的好奇,決定寫下本篇文章。本文內容多源于MIPI Allliance官方網站、論壇、博客等,因此,它僅作為碎片化知識的整理、記錄,重點分享下I3C的主要特點以及與I2C的關系。

I3C簡介

I3C,全稱Improved Inter-Integrated Circuit,顧名思義,它是I2C(Inter-Integrated Circuit)的橫向升級版,可向下兼容。

眾所周知,I2C在上世紀80年代由Philips公司推出,當初是為了簡化計算機各芯片之間的數據通信方式而產生,經過數十年的發展,速度從最初的100Kbps提升到3.4Mbps(超高速模式5Mbps不常用)。I2C的應用在控制系統中已經非常廣泛了,作為1種同步串行總線,相比板上其它設備間通信接口,它具有總線結構簡單(2線,OD輸出,SCL/SDA)、一主多從、低功耗、高可靠性等特點。

推出I3C,并非為了替代I2C總線,而是一脈相承,它主要解決了I2C現存的問題,在低成本的產品中,I2C依然是高性價比的選擇。

在I2C中,這些局限性包括每個從設備擁有一個7位的固定地址,在掛載多設備時可能存在 I2C總線設備地址沖突,I2C還有不帶內中斷或目標設備復位(需要額外的導線/引腳)、較低的數據速率等缺陷。在SPI中,一些主要局限包括每個器件有一個芯片選擇引腳但需要四條通信線路,以及由于缺少明確定義的標準(如數據位寬)而存在許多不同的實現方式(如CPOL/ CPHA四種工作模式)。

借用NXP網站的描述:I3C“在標準CMOS I/O上,它支持10Mbps的最低數據速率,具有更高性能的高數據速率(HDR)模式的選項,與現有選項相比,性能和功耗效率大幅提升。它還提供多主機支持、動態尋址、命令代碼兼容性和高級電源管理功能(如睡眠模式)的統一方法。”總結成一句話:它非常適合應用于高速、多主機、多從機(傳感器)等應用場景。I3C總線的速度提高了,功耗降低了,效率提升了,在需要更精簡、高性能、高速度、可擴展和具有成本效益的通信應用中,I3C應運而生。

應用場景

物聯網(IoT)行業、移動設備、汽車系統、服務器、工業設備等。

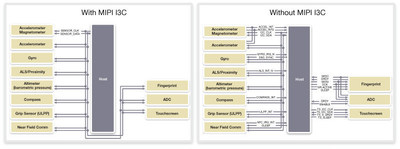

面向傳感器應用:用于需要精簡連接和多傳感器管理的場景,統一碎片化的傳感器接口。

希望提高通信速度和效率、同時需要簡化總線接口的應用場景。

I3C主要特性

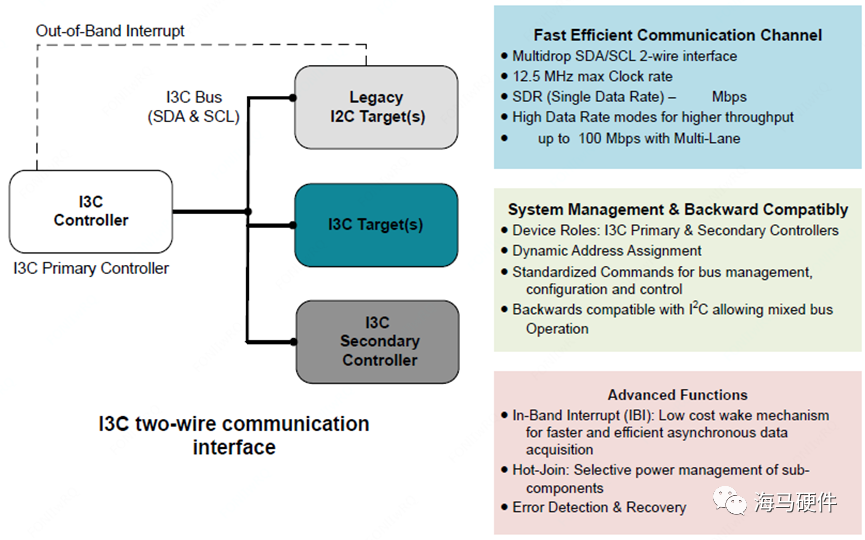

I3C接口特性如下:

1.速度:SDR模式(單邊沿采樣)基礎速率12.5Mbps(最低10Mbps),HDR模式(雙邊沿采樣)理論最大速率39.5Mbps(實際有效傳輸速率在33.3Mbps左右)。

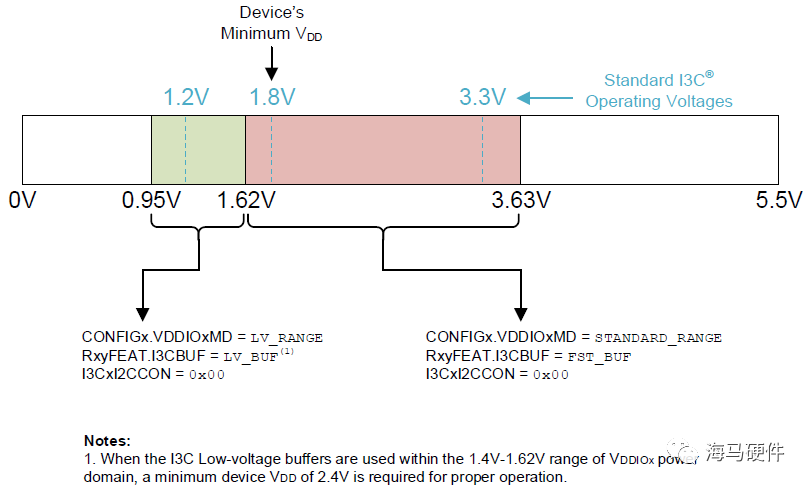

2.功耗:最低支持1.2V電平(支持1.8V/3.3V,不支持5V)。在同樣的電平標準下,整體功耗遠小于I2C。

3.總線結構:兩線(SDA/SCL)串行接口,開漏/推挽可靈活切換,支持多主多點功能(Multi-Controller and Multi-drop capabilities)。

4.熱加入機制(Hot-Join):I3C協議支持熱加入機制,以允許從設備在已配置后加入I3C總線。

5.動態地址(transaction):支持,從設備地址由當前的主控制器(Active Controller)初始化后分配,通常在上電后完成。

6.中斷機制(In-Band Interrupt):支持內中斷,從設備通過I3C總線產生中斷并通知主控制器,節省1根INT線。

7.向下兼容I2C:在基礎模式中兼容I2C總線。

?I3C特性介紹

1.傳輸速率

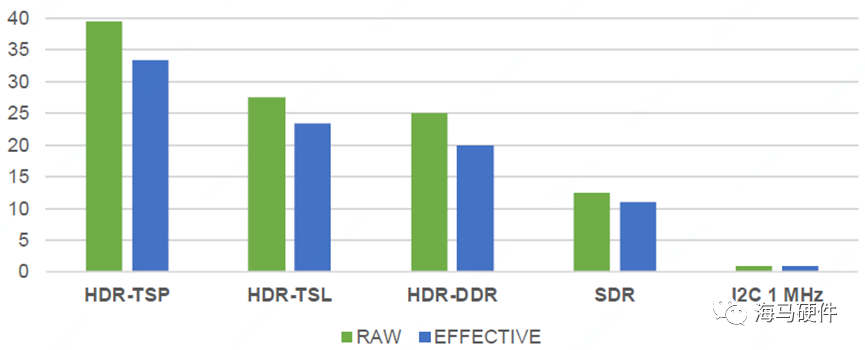

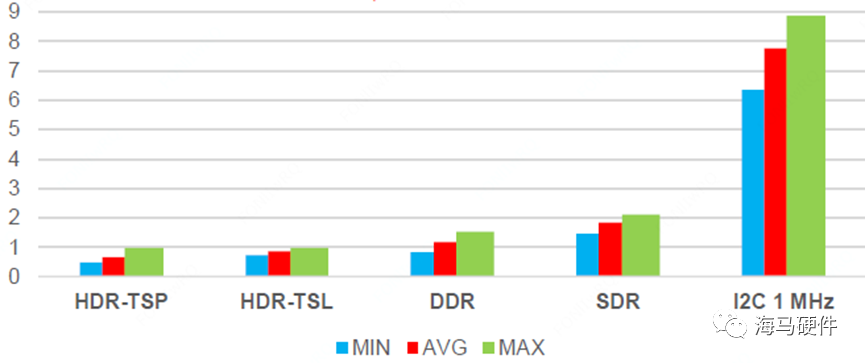

I3C的理論傳輸速率相較I2C提升了12.5 倍至 125 倍。如下圖所示,I3C支持多種速率的工作模式,其中,

SDR 模式:12.5Mbit/s,Single Data Rate Mode,I3C的默認模式。

HDR-DDR模式:25Mbit/s,High Data Rate Mode,Dual Data Rate Mode。

HDR-TSL模式:30 Mbit/s,Ternary Symbol Legacy-inclusive-Bus。

HDR-TSP模式:39.5 Mbit/s,Ternary Symbol for Pure Bus (no I2CDevices)。

值得說明的是,MIPI聯盟定義了I3C復雜的協議規范,但HDR-TSP模式和HDR-TSL模式并不被包含在I3C的基礎結構(I3C Basic),作者的理解是,若要實現這兩種HDR模式,需要專門的IP,而且對主從設備工況的要求也更嚴苛。因此作者將I3C HDR和I3C Basic理解為兩個概念,它們擁有不同的總線架構、時序、協議規范。相比完善、高靈活度和高效的I3C接口,I3C Basic是一個降低了性能、低復雜度的版本,適用于板內設備連接應用,比如傳感器和內存接口。I3C Basic滿足開發者和普通用戶組織的設計與應用。個人理解,從普通應用層面來說,I3C最大僅支持25Mbps速率(HDR-DDR模式)。

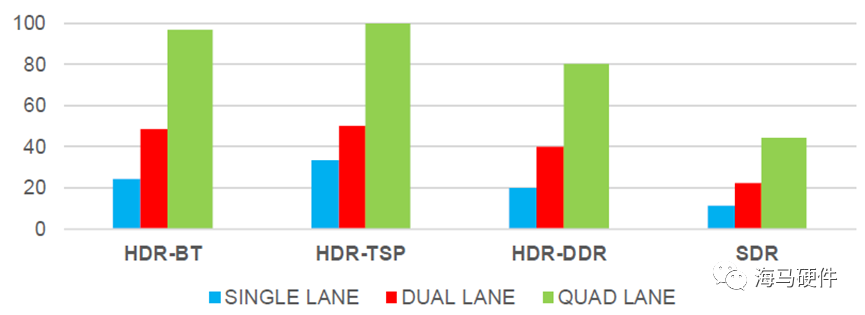

另外,上面提到的I3C速率指的是單通道模式下的理論和實際速率,如下圖所示,I3C還有多通道模式(Multi-Lane,HDR-BT)。多通道指的是使用多根SDA數據線,如雙通道(HDR-BT DUAL)、四通道模式(HDR-BT QUAD)。在HDR-BT(HDR Bulk Transport)四通道模式中,最高速率可以達到100Mbps(實際速率約97Mbps,即12MB/s),它是SDR模式的8倍。HDR-BT支持SDR、HDR-DDR、HDR-TSP。同樣地,多通道HDR-TSP和SDR并不被包含在I3C Basic版本中。

實現I3C高性能/高效率通信(HDR模式),需滿足以下條件:

在布局上,從設備(Targets)靠近主設備(Controller),且走線無延遲;

每根線上的最大漏電流:4μA;

驅動端(主/從)的內部等效電阻:90Ω;

總線的主時鐘頻率:12.5MHz;

總線工作在1.8V電平;

總線上拉電阻取值:2833Ω;

高低電平寬度保持一致(Equal probability for 1 and 0 on data transmission,猜測是要求在保證可靠的建立保持時間基礎上,提高傳輸效率)。

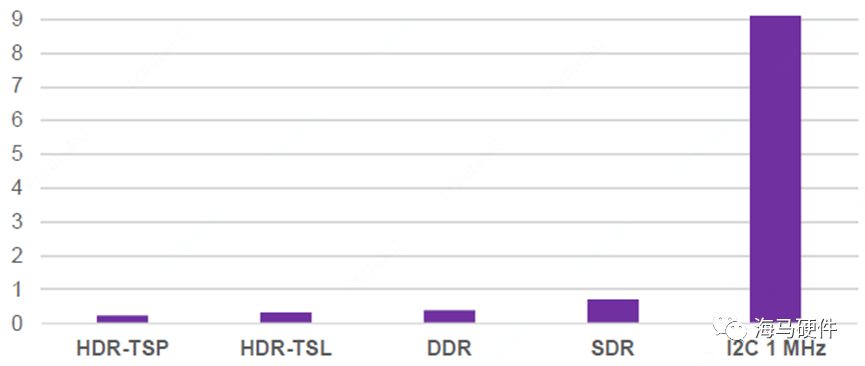

在傳輸效率上,同樣傳輸1kB的數據量,I3C消耗的時間(ms)遠小于I2C。

2.功耗

1)功耗對比

在SDR模式下,同樣傳輸1kB的數據量,單通道I3C的功耗要小于單通道I2C約6mJ,降低約70%(從柱狀圖來看)。I3C也有睡眠模式(暫未詳細了解)。

2)DC特性

這里主要介紹下I3C支持的電平標準。

I3C支持1.2V、1.8V和3.3V電平標準(CMOS,閾值30%/70%),它甚至支持更低電平(如1.0V)。I3C在5V的CMOS電平標準上表現并不突出,但如果有足夠的驅動強度,且/或降低傳輸速度的情況下,可擴展支持5V(直譯過來很繞)。

當工作在推挽(Push-Pull/Totem-Pole)模式時,SDA信號可以達到更高的速度,此時總線電容須不大于50pF。在1.0V的標稱工作電壓支持100pF容性負載,以用于新用途,如DDR5中的串行狀態檢測(SPD),由于速度提升,可擴展從設備的數量,提高了系統的啟動速度。

有關DC詳細參數見Specificationfor I3C Basic.pdf 中的“I3C Electrical Specifications”章節。

3. 總線結構

I3C有2種總線結構,分別是開漏和推挽。保留開漏結構是為了兼容I2C的低速應用,而I3C在SDR/HDR高速模式中使用了推挽方式,它的驅動能力更強,但需要控制器針對性的設置。

I3C有個很重要的特點,即規范上定義了I3C兩種工作模式,分別是同步時序控制模式和異步時序控制模式(AsyncMode 0-3)(這里作者還不理解,后續再研究),異步時序控制模式指的是主機和從機工作的時鐘源、時鐘頻率、時鐘精度不同。

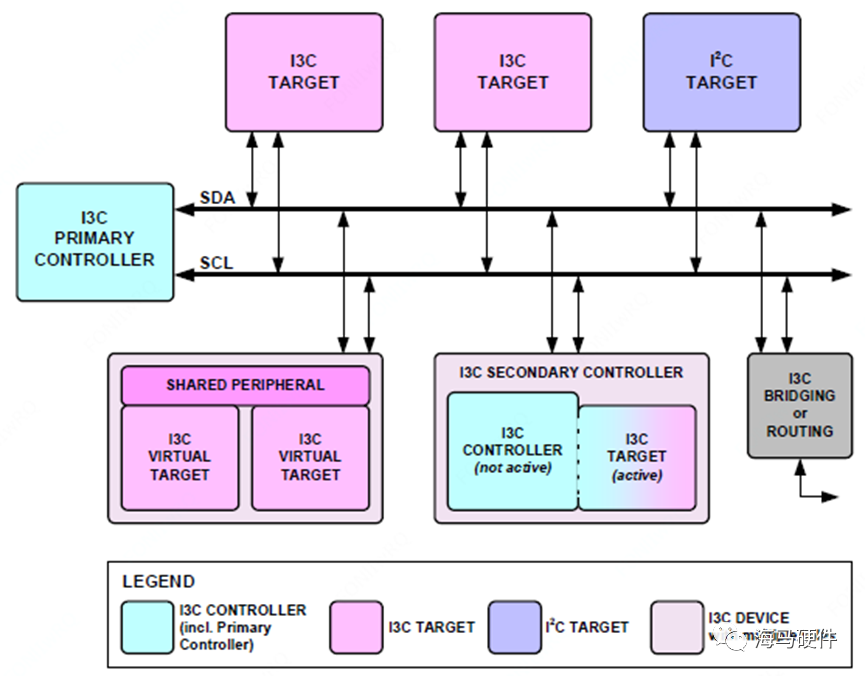

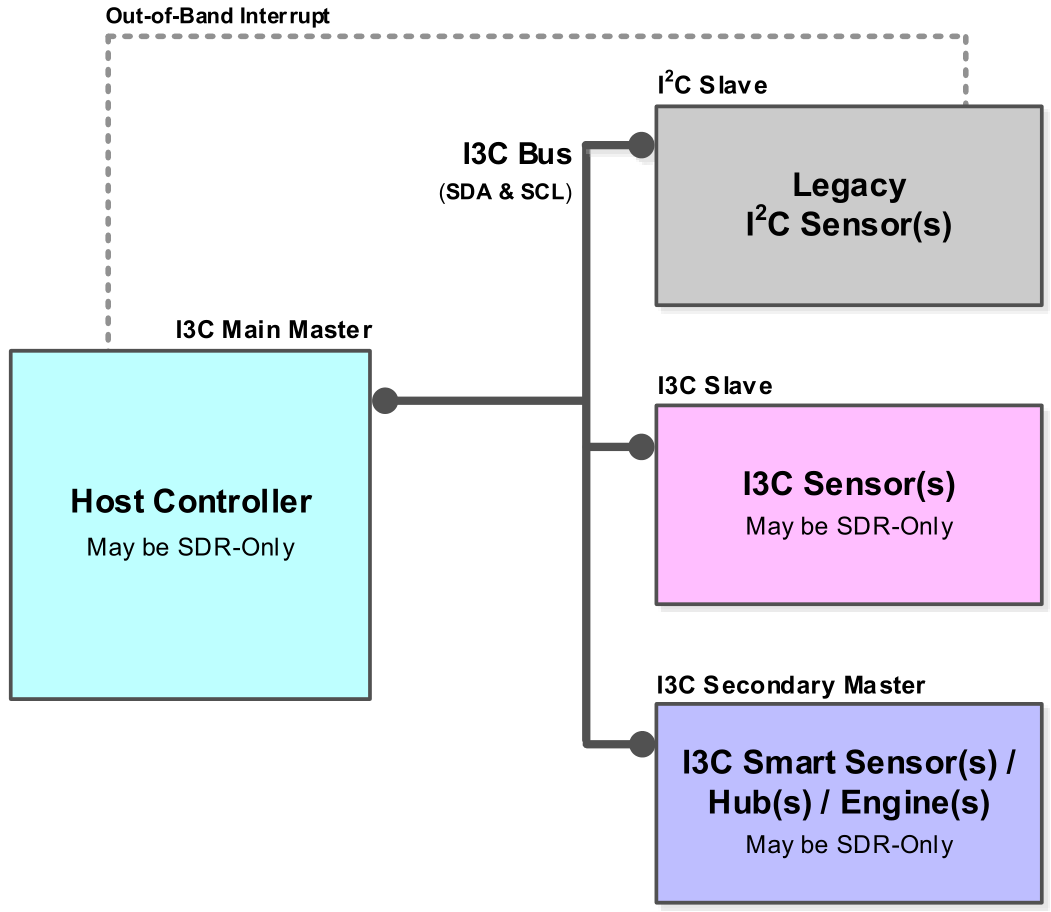

總線上掛載的各個設備連接關系如下圖所示。這里先來個名詞解釋:

I3C PrimaryController:主控制器,可以支持或不支持HDR模式。

I3C SecondaryController:輔控制器(第2控制器),可以支持或不支持HDR模式,可以作為主機。

I3C Target:I3C從設備(目標設備),可以支持或不支持HDR模式。

I2C Target:不支持HDR模式,指的是傳統的I2C低速設備。

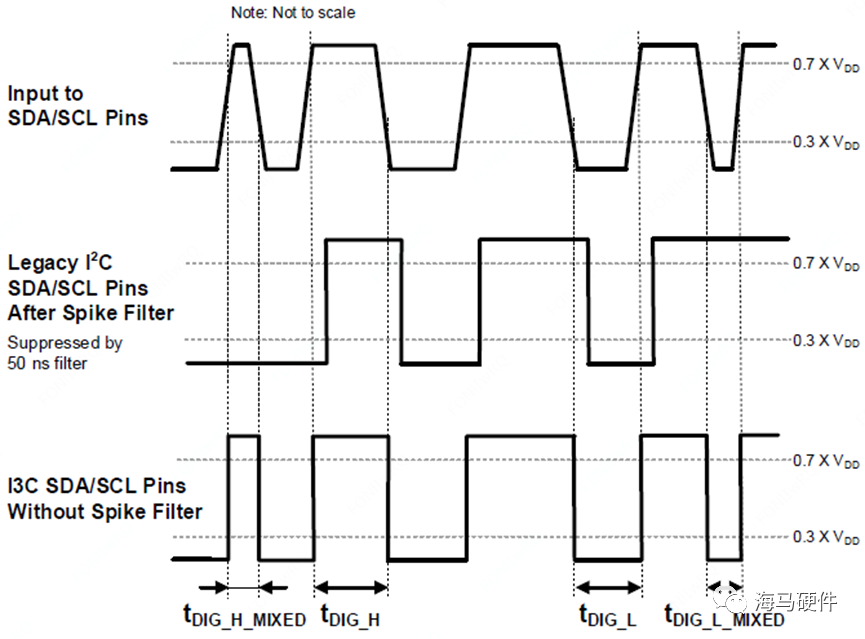

當所有設備共同掛載到1個I3C總線時,總線被命名為“混合快速總線(Mixed Fast Bus)”,若僅有I3C設備時,被成為“純總線(Mixed Bus)”;還有1個“混合低速/受限總線(MixedSlow/Limited Bus)”。混合快速總線和混合低速/受限總線的主要區別就在于I2C設備是否存在50ns的尖峰濾波器(下文會提到)。

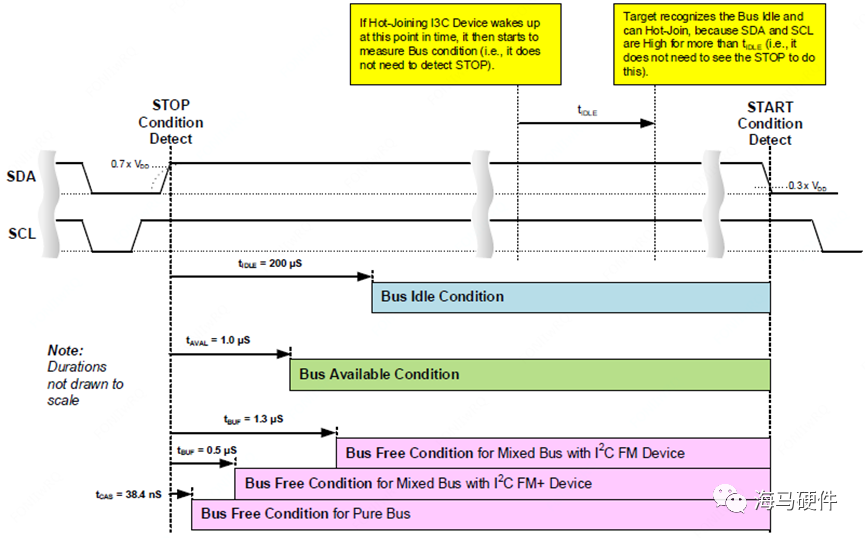

4.熱加入機制(Hot-Join)

在I3C 中,目標設備被允許加入已配置的總線,并由 I3C 控制器分配一個動態地址。憑借I3C 中的這種熱加入功能,可以在運行期間開啟和關閉總線上的某些器件,從而實現“分段式供電”設計,僅在需要時才使相關單元保持活動狀態。在一些應用中,如果不希望或不可能讓系統斷電(例如在服務器或無線基站中),或必須正確設計熱插拔功能(在背板或外部卡中)時,此特性將非常重要。

5.動態地址

I3C有著一整套通用命令字的集合,可以通過這些命令字實現動態地址分配、檢查當前總線狀態、時間控制、IO擴展等等功能。I3C從設備地址由主設備仲裁,但并不是所有設備地址都可用,部分地址是I3C標準所保留的,用于后期拓展或者錯誤仲裁。

6.中斷機制

I3C無需增加外部中斷線即可實現中斷響應。

I3C帶內中斷,有地址仲裁特性(In-Band Interrupt,IBI),當從機產生中斷,IBI向主機發送中斷信息、地址和其它信息。若有多個從機中斷,較低的地址具有較高的優先級(具有較低值地址和較高優先級、帶內中斷的從機對控制器的處理請求要比具有較高值地址和較低優先級的從站更快<直譯過來很繞>,原文:Targets with lower valueAddresses and higher Priority Levels have their In-Band Interrupts andController Role Requests processed sooner than Targets with higher valueAddresses and lower Priority Levels)。地址仲裁特性對熱插拔、動態地址分配以及多主機申請同樣有效。

7.向下兼容I2C

I3C與I2C總線數量(2根,SDA/SCL)相同,在同一組I3C總線上可以同時掛載I2C設備(工作速率不同);

I3C 總線支持傳統 的I2C 通訊,I3C通信使用推挽結構,I2C通信使用開漏結構;

I3C支持動態地址分配,也同時支持傳統 I2C 設備的靜態尋址;

如下圖所示,I3C總線可以將時鐘速度更改為允許速度范圍內的任何頻率。相比之下,當傳統I2C設備掛載到混合快速總線中,為了不引起傳統I2C器件參與到總線進來,I2C需要擁有50ns Spike Filters,也就是說,必須確保總線上的SCL高電平周期比Spike濾波器短(SCL時鐘頻率大于12.5MHz),每個傳統I2C 從機的SCL線需要配有 50ns 尖峰濾波器,目的是忽略掉下圖的“DIG_H_MIXED”高電平段(脈寬范圍32~45ns),以防止Legacy I2C器件受到干擾(作者的理解是,這一段是I3C SDR/HDR模式的最小脈寬,芯片內部增加濾波電路將其濾掉)。

I3C基本時序(SDR)

1.I3C通信流程概括

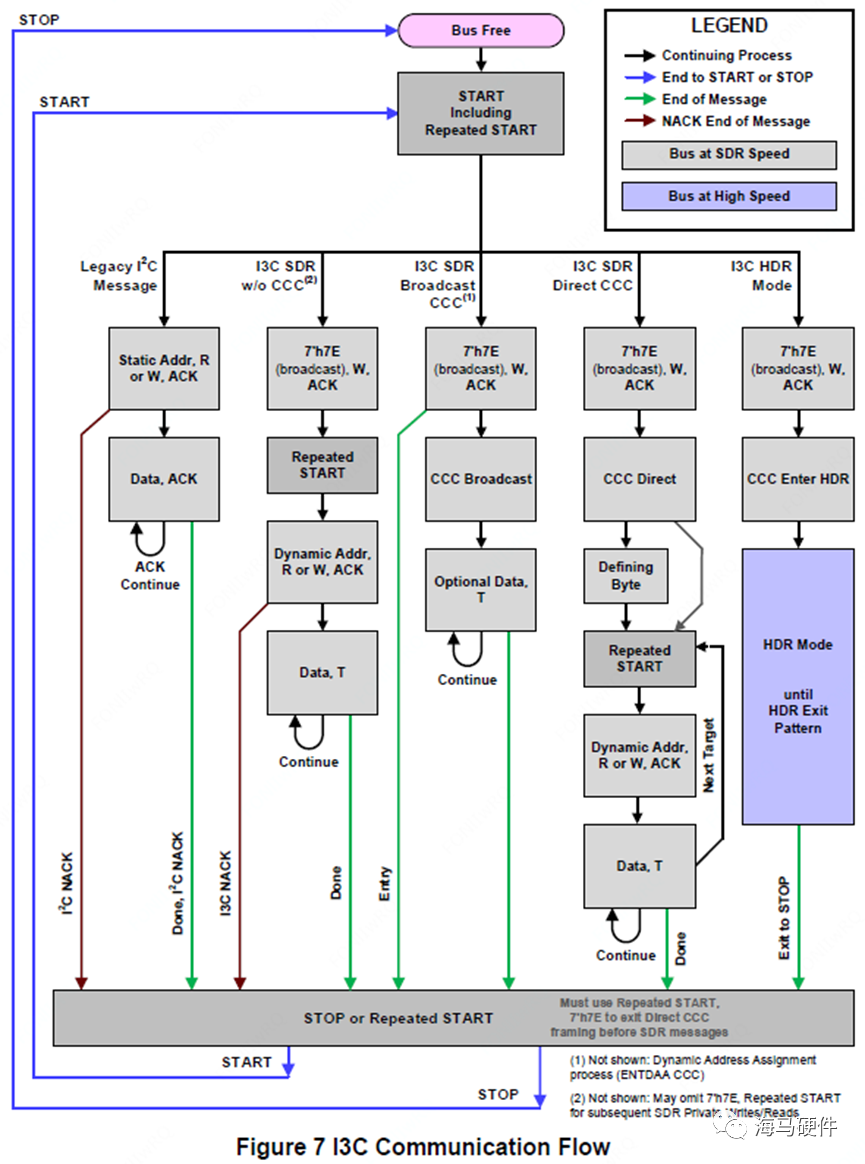

I3C支持多種通訊方式,先貼一張I3C通信總體流程圖(4.1 I3C FundamentalPrinciples 章節):

由于還沒去詳細的研究時序,這里先簡要的說明下:

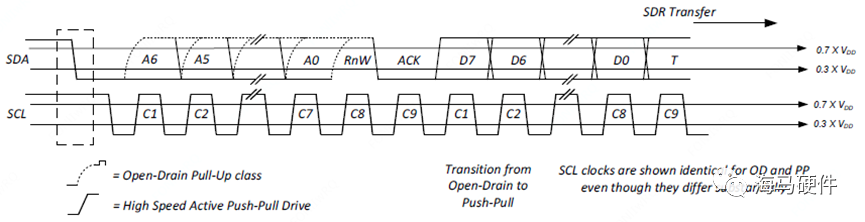

首先,I3C完整的幀包含START、Header、Data、STOP,這個與I2C和其它總線接口都大同小異。在START之后,主機利用Header來尋址從機設備(靜態地址、動態地址、廣播地址、熱加入地址)。Header允許總線仲裁,從機設備也可以將Header仲裁用于多種目的:內中斷,熱加入和輔助主設備功能(I3C總線只能有1個主控制器控制總線,總線上輔助主設備可通過某種機制使用來替代主控制器,也就是多主機機制)。

上圖中的CCC(CommonCommand Code,通用命令代碼)是全局支持的命令,可以直接傳輸到特定的I3C從設備,也可以同時傳輸到多個I3C從設備,它可以在同一條總線上執行多個命令。它是主從設備之間的一種通信機制(網上有人把CCC比喻成Linux的Shell指令),通常由主設備發給從設備,用于獲取和設置從設備的功能、配置信息,它提高了主設備對從設備的管理能力。CCC也支持雙向通信,用于確認主從雙方的指令。CCC不適用于傳統I2C接口。

在啟動或重復啟動之后,CCC的地址始終為7’h7E,而讀寫Rn/W位應始終為W。一旦分配了I3C從機,所有I3C從機都將識別7’h7E廣播地址和它們自己的動態地址。 在分配I3C動態地址之前和之后,I3C主機均應發出CCC命令。CCC命令分為廣播(Broadcast)寫、直接(Direct)讀/寫、直接寫、直接讀取四類(具體有點復雜,詳細了解CCC,需要再熟讀5.1.9章節),廣播命令碼有255個,范圍0x00 - 0x7F,上圖中7’h7E是廣播地址,直接命令碼范圍是0x80 - 0xFE。

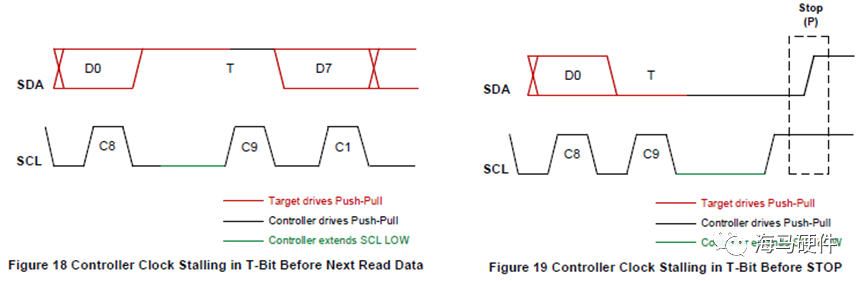

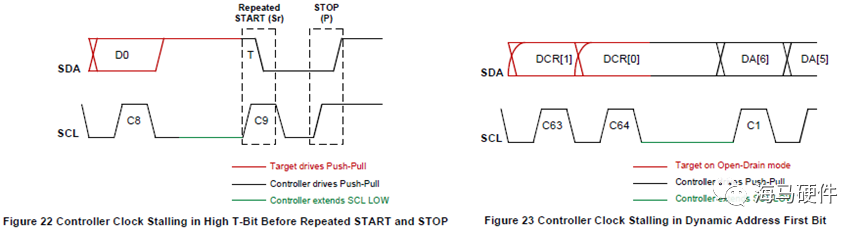

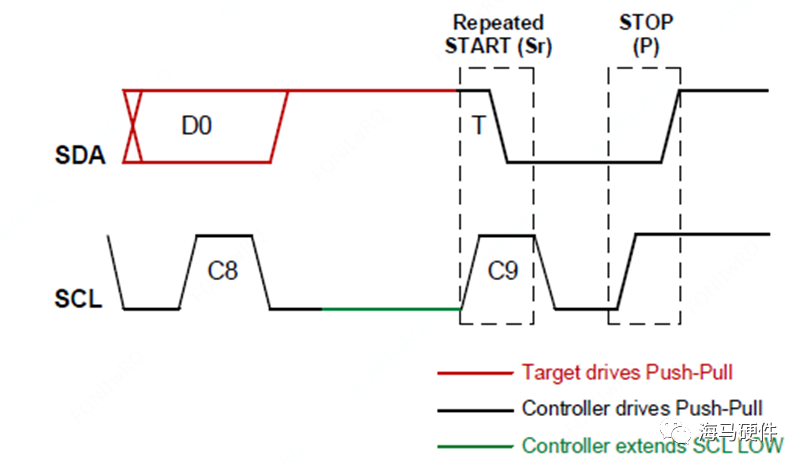

后面是數據的傳輸,數據按照SCL上升沿邊沿(HDR模式是雙邊沿采樣)進行采樣。上圖中,傳統I2C是在數據傳輸完成后由接收方發送ACK或NACK(即框圖中的DATA.ACK),而與傳統I2C不同,在I3C SDR模式中提到了“Data. T”字樣,即T Bit,它是Transition Bit(過渡位)的簡稱,作為ACK/NACK機制的替代方式而推出。值得說明的是,T Bit是第9位數據,它是作為奇偶校驗存在的,即使I3C SDR沒有ACK機制,但總線協議中有一些錯誤事項的標志位可以用來替代NACK事件的發生(此處存疑,待研究),CCC命令也定義了數據讀寫的最大長度,會提前通知目標設備(從機)。

當主機(Controller)從從機(Target)中讀取返回的數據,產生的T-Bit是最后1個數據位,不像I2C,從機無法控制其發送數據的數量,I3C的從機通過返回T-Bit來控制發送數據的數量,它還允許主機在必要時中止讀取。

如下圖所示,當從機返回T-Bit為0時,意味著要結束發送,反之返回T-Bit為1,意味著繼續發送,并監控SDA線。如果SDA在下一個SCL的下降沿保持高電平,則繼續發送下一組數據;如果SDA在下一個下降沿的邊沿(重啟)為低電平,則主機中止數據傳輸,且從機不繼續發送,可以使用RSCIF標志位來監視這種情況(I3C有很多標志位用于檢測總線狀態,比如大家熟知的用于檢測起始位的SCIF、結束中斷標志PCIF、應答接收中斷標志I2CACKIF、地址匹配標志SADRIF、動態地址匹配中斷標志DADIF等)。

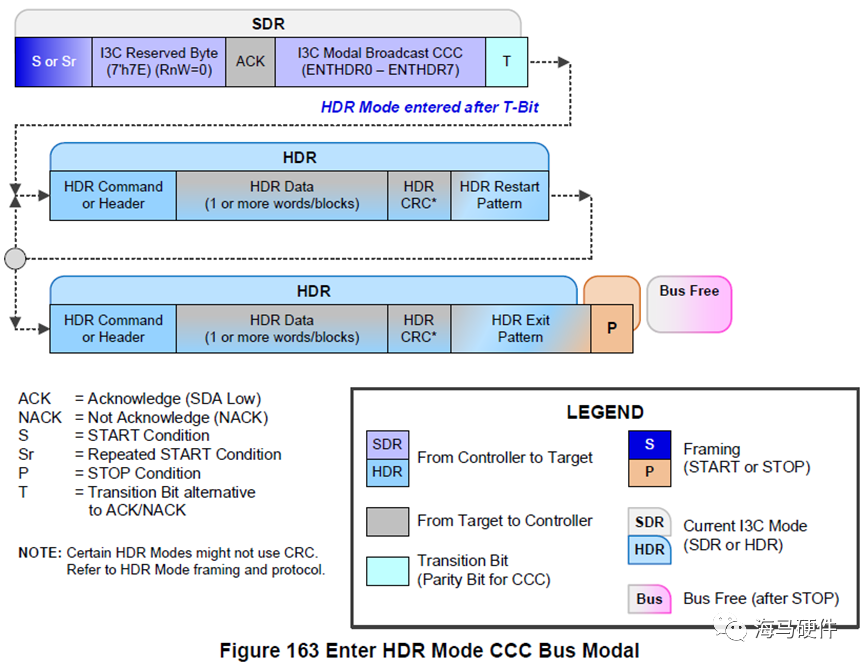

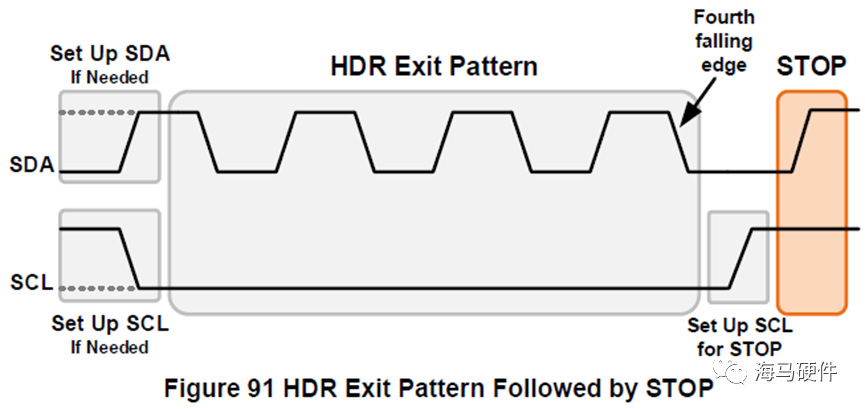

順便提一下,HDR的機制很特殊,它的時序與傳統I2C和SDR模式顯著不同,比如若要從SDR進入或退出HDR模式,需要發送特定的序列。

最后,當一個序列的數據發完,會發出停止位,總線進入IDLE狀態,隨后,重啟START,進入下一個周期。

2.I3C SDR基本時序

這里簡要說明下I3C在SDR模式下的時序(HDR稍顯復雜,比如HDR-DDR是雙邊沿采樣、帶CRC)。

I3C SDR模式的時序與I2C總體上一致,二者的區別主要體現在時鐘速率上,相比I2C,I3C對SCL/SDA的建立保持時間更加嚴格,I3C可降速支持I2C。

1、起始位與停止位:

I3C的START、STOP機制與I2C一致,即,在時鐘邊沿翻轉為低電平之前和時鐘邊沿翻轉為高電平之后,數據線分別產生下降沿和上升沿的跳變。

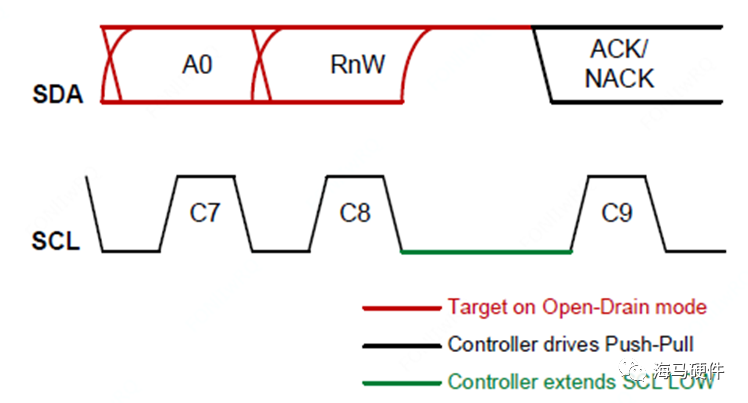

2、地址/讀寫/數據位(Legacy I2C/SDR):

3、應答位:與I2C類似,在第9位產生ACK/NACK或T Bit。

不同速率模式/總線結構(OD或Push-Pull)下的建立保持時間指標可參考文檔Specification forI3C Basic.pdf中的“6.2 TimingSpecification”章節。

不同板載通信總線的對比

| 通信接口 | UART | I2C | SPI/QSPI | I3C |

| 通信機制 | 異步 | 同步 | 同步 | 同步 |

| 總線結構 | 2線,半雙工 | 2線,半雙工 | 4線,全雙工 | 2線,半雙工 |

|

理論最大 通信速率 |

10Mbps | 3.4Mbps | 60Mbps | 39.5Mbps |

| 主設備 | 單一 | 單一 | 單一 | 支持多個 |

| 從設備 | 點對點 | 多個 | 多個 | 多個 |

| 軟中斷 | 不支持 | 不支持 | 不支持 | 支持 |

| 熱加入 | 不支持 | 不支持 | 不支持 | 支持 |

| 從設備地址 | 不支持 | 靜態地址 | 靜態地址 | 靜態和動態地址 |

審核編輯:湯梓紅

-

傳感器

+關注

關注

2541文章

49945瀏覽量

747442 -

總線

+關注

關注

10文章

2817瀏覽量

87697 -

總線接口

+關注

關注

0文章

82瀏覽量

30682 -

I2C

+關注

關注

28文章

1452瀏覽量

122238 -

MIPI

+關注

關注

10文章

303瀏覽量

48372

原文標題:MIPI-I3C總線接口簡述(一)

文章出處:【微信號:海馬硬件,微信公眾號:海馬硬件】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用Verilog HDL實現I2C總線功能

I2C總線接口模塊設計

PCA9564 并行總線轉I2C總線接口芯片簡介

用Verilog HDL實現I2C總線功能

基于CPLD的I2C總線接口設計

基于MIPI I3C規范從I2C無縫連接I3C的關鍵優點

MIPI聯盟公開其傳感器接口規范MIPI I3C

關于MIPI I3C Sensor接口標準制定的介紹和應用

符合最新MIPI I3C規范的DesignWare IP提供高帶寬和可擴展性

基于MCS-51單片機I2C總線接口電路的設計

MIPI I3C主機控制器接口加速傳感器集成

I3C Introduction是什么意思

MIPI-I3C總線接口簡述

MIPI-I3C總線接口簡述

評論