目前集成電路的封裝內部最常見的方式有「打線封裝(Wire bonding)」與「覆晶封裝(FCP:Flip Chip Package)」兩種,如果芯片的正面朝上,也就是含有黏著墊的那一面朝上,通常使用「打線封裝(Wafer bonding)

1.Wire bond原理: 對金屬絲和壓焊點同時加熱和超聲波,接觸面便產生塑性變形,并破壞了界面的氧化膜,使其活性化,通過接觸面兩金屬之間的相互擴散,形成金屬化合物而完成連接。

2.常用線材: 金線,Ag合金線,鈀銅線,純銅線。 基于0.8mil,20um各種線材特性比較如下: 金線的主要優點: 硬度低,應力小,不容易產生彈坑。 抗氧化性好,在高溫高濕下環境下的長期可靠性好。 缺點:成本較高,金屬遷移率高,相比其他線材易產生Kirkendall Void。

銀合金線的主要優點: 硬度低,應力小,不容易產生彈坑,成本低。 缺點:相比其他線材斷裂載荷偏小。

銅線的主要優點: 成本低,電阻率小,金屬遷移速率低,高溫不易產生Kirkendall Void。 缺點:硬度大,容易產生彈坑,高溫高濕下易腐蝕。

銅線和鈀銅線優缺點比較:1)鈀銅線具有更好的耐腐蝕性 2)鈀銅線開封后可以存儲7天,純銅線只能存儲3天。3)鈀銅焊接時在純氮氣環境下,純銅線需要在氮氫混合氣體中。

打線封裝的制作流程

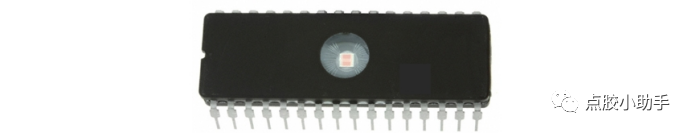

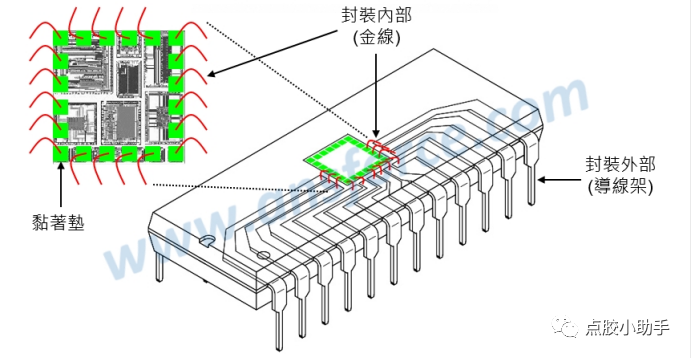

打線封裝一般都使用「導線架」與「金線」,而且必須將黏著墊(Bond pad)制作在芯片的四周圍,導線架的金屬接腳(蜈蚣腳)也必須制作在集成電路封裝外殼的四周圍,如<圖一>所示,因此打線封裝的接腳數目不能太多。打線封裝的步驟為:在靠近芯片的一側,以機械鋼嘴將金線加壓加熱打在芯片四周圍的「黏著墊」上;在靠近導線架的一側,以機械鋼嘴將金線加壓加熱打在「導線架」上,打完第一根金線,再打第二根,依此類推。

圖一打線封裝技術。

打線封裝最大的缺點是打線的動作必須「一根一根地」完成,非常費時;而且芯片上的黏著墊與導線架的金屬接腳只能制作在四周圍,所以當芯片上的CMOS數目愈多,傳送的電訊號愈多,需要的金線也愈多,但是芯片的四周圍空間有限,只能容納固定數量的「黏著墊」,封裝外殼的四周圍空間也有限,只能容納固定數量的「金屬接腳」,因此打線封裝接腳數目不能太多。然后將芯片放到lead frame上,并且用銀漿固化,其實就是將芯片和lead frame的底部粘住啦。lead frame可以理解為引線框架,是一種陣列結構,

打線封裝的應用

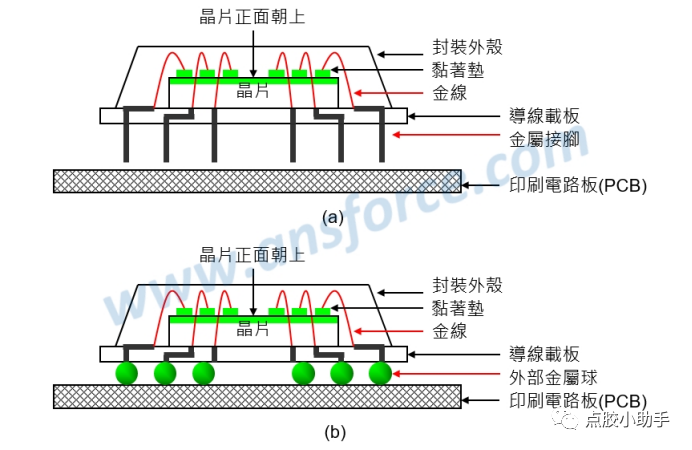

打線封裝除了可以使用「導線架」之外,也可以使用「導線載板leadframe」,如<圖二>所示,配合封裝外部使用針格陣列(PGA)或球格陣列(BGA)如下:

內部打線封裝,外部針格陣列(PGA):如<圖二(a)>所示,是以前英特爾(Intel)的中央處理器(CPU)常用的封裝方式,目前內部大都已經改用覆晶封裝了。

內部打線封裝,外部球格陣列(BGA):如<圖二(b)>所示,是以前個人計算機的北橋芯片與南橋芯片經常使用的封裝方式,目前內部大都已經改用覆晶封裝了。

圖二打線封裝的應用。

打線封裝的優缺點

優點:適合中小型芯片,大型芯片也有使用,技術較成熟。

缺點:每支接腳必須打線封裝速度較慢,封裝體積較大。

審核編輯:湯梓紅

-

芯片

+關注

關注

453文章

50410瀏覽量

421849 -

集成電路

+關注

關注

5381文章

11386瀏覽量

360877 -

封裝

+關注

關注

126文章

7784瀏覽量

142725

原文標題:了解打線封裝嗎?(Wire bonding)

文章出處:【微信號:半導體封裝工程師之家,微信公眾號:半導體封裝工程師之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯片封裝與芯片打線

封裝打線強度測試

封裝打線強度試驗 (Wire Bond Test)

怎樣進行芯片封裝打線強度試驗?

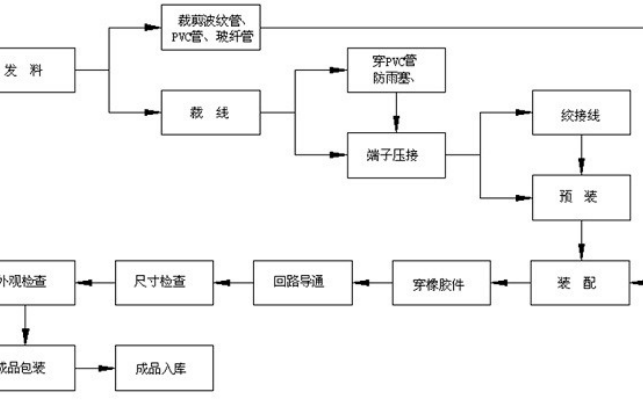

汽車線束的制作工程流程

Cadence PCB封裝制作流程

打線封裝的制作流程和應用

打線封裝的制作流程和應用

評論