隨著系統的復雜度不斷提高,如何確保走線信號質量越來越成為廣大工程師要面臨的一大難題。對于系統走線,可以粗略劃分為高速低速信號。

對于高速信號,如DDRMIPIPCIE等信號,雖然其信號速率高,SPEC要求也更加嚴苛,但由于其優先級較高,在layout階段,大都會著重去預留時間空間去優化。故在整個系統仿真優化過程中,工程師花費的時間及精力相對不多。

但對于低速信號,如SPMICLKRFMIPI,甚至于I2C等信號,由于其layout的優先級較低,往往在項目后期才開始走線,優化的空間相對有限。且低速信號的拓撲結構往往相對復雜,經常出現一拖多的復雜拓撲。這就導致在后期,工程師需要花費大量的時間精力來對低速信號進行多輪的仿真優化。

HyperLynx作為一款功能強大的仿真工具,不僅支持各種高速信號的仿真,對于復雜拓撲的低速信號的仿真優化同樣極具優勢。本文章主要介紹如何利用HyperLynx SI來對復雜拓撲信號,尤其是低速信號來進行快速的仿真測量,提高項目整體的仿真效率。

HyperLynx SI Pre-Sim for Complex topological signals

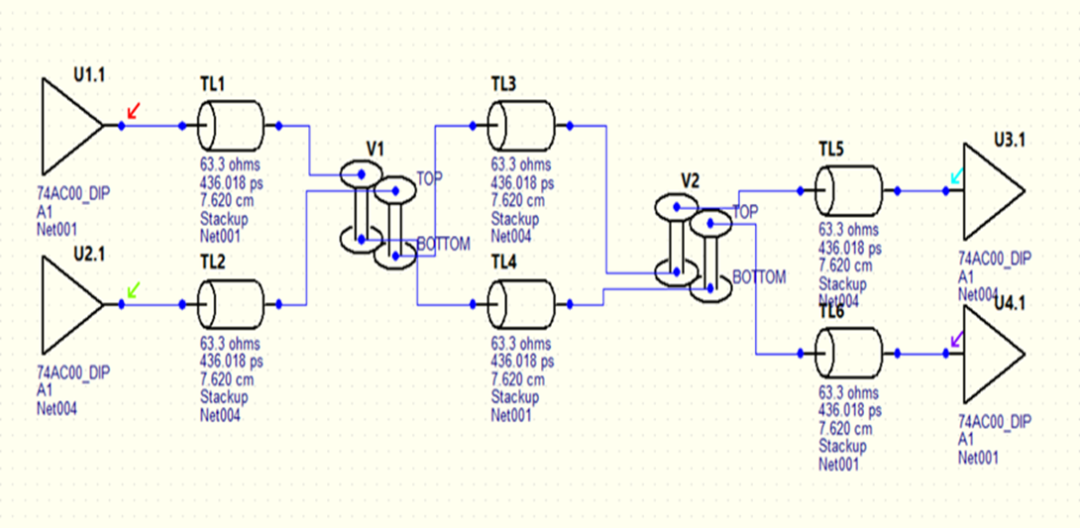

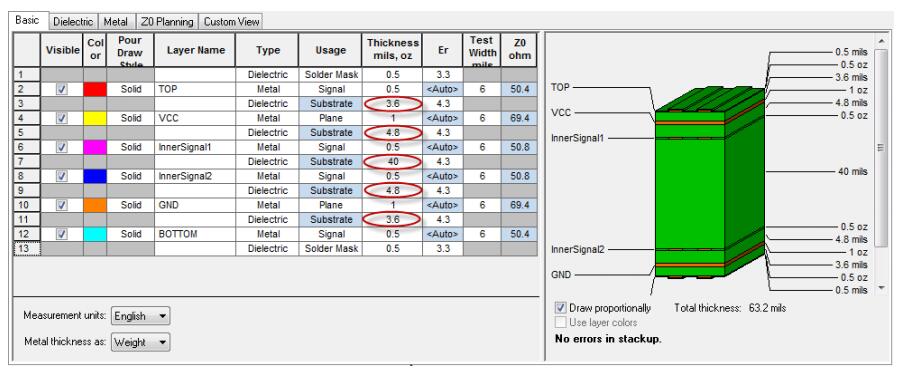

在項目初期階段,此時信號走線還沒有完成,我們可以通過HyperLynx LineSim搭建一個仿真電路來進行Pre-Sim(前仿真,PCB Layout前的仿真)。

HyperLynx LineSim提供功能強大的各種控件供用戶進行選擇使用,用戶可以在此基礎上輕松評估各種可能對走線質量造成影響的設計因素,如疊層、表面粗糙度、過孔反焊盤設置、背鉆、串擾耦合等,在項目初期實現高效仿真評估。

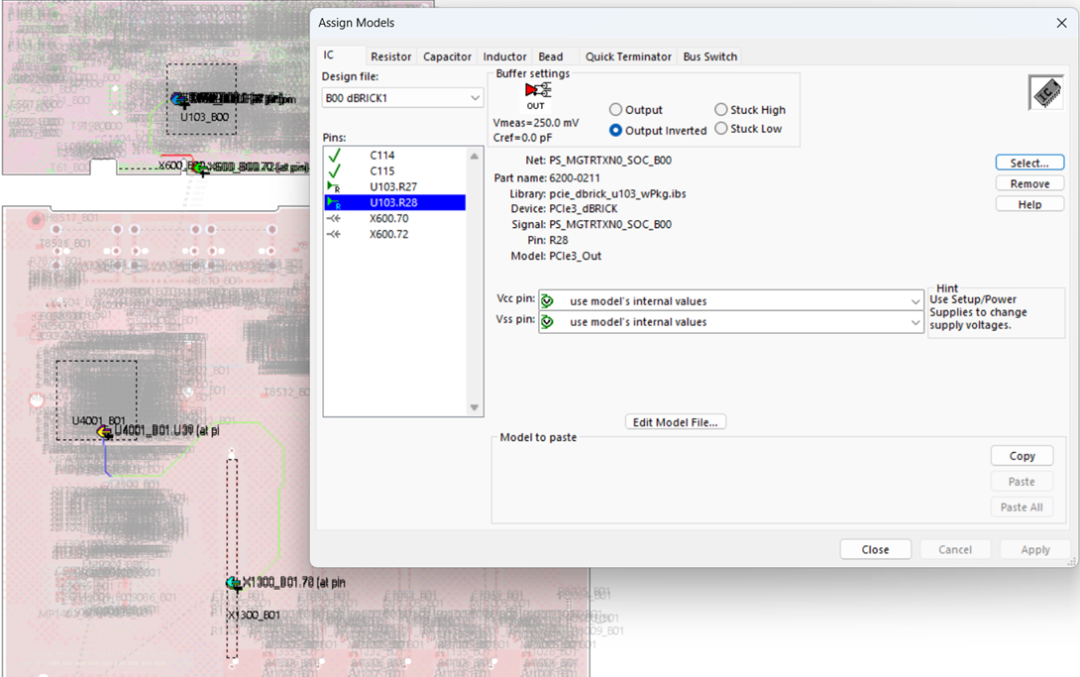

HyperLynx SI Post-Sim for Complex topological signals 這一部分我們將介紹如何通過HypeLynx BoardSim來進行Post-Sim(后仿真,PCB Layout之后的仿真)。

在這一階段,項目已經初步完成了走線,用戶需要仿真驗證走線是否能夠滿足相關的設計指標。HyperLynx SI提供一種高效的、可視化的方案供用戶在這一階段進行仿真驗證。

HyperLynx BoardSim基于用戶提供的Layout文件(.tgz.cce.brd等),可以輕松對走線進行全程可視化的高效仿真。用戶不需要再額外對走線進行單獨的S參數提取,所有的仿真都在一個工具界面上完成。

BoardSim還支持一個板子上不同的區域有不同的疊層及跨板聯合仿真等仿真場景,可以輕松駕馭不同的走線設計情況。

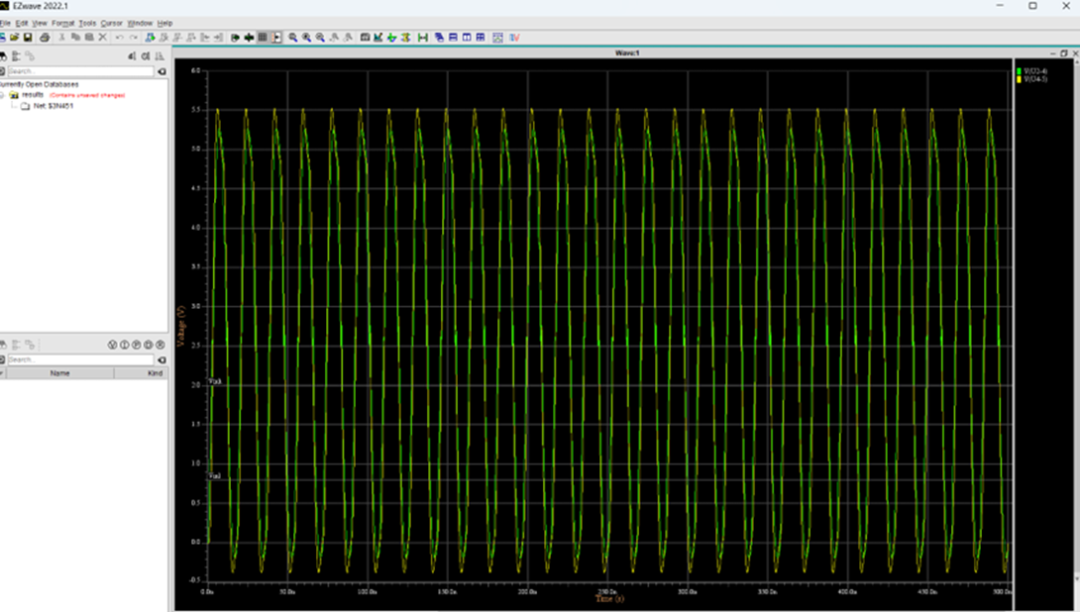

HyperLynx SI仿真測量 不管是前仿真還是后仿真,最后都會到同一個環節:仿真。在這個環節里面,用戶需要對仿真結果做一系列的量測并與設計指標做比較,以判定信號質量是否能夠滿足設計要求。

HyperLynx SI提供一個非常完整強大的仿真工具:EZwave,可以滿足用戶的多樣化設計需求。用戶可以自定義每一根走線的input signal,可以進行SIPI聯合仿真,甚至可以調用HSPICE仿真求解器(需HSPICE License支持)。

EZwave的測量工具提供了多種類型的測量手段,如常見的時域上升/下降時間測量,頻域的相位余量,信號完整性領域的串擾測量等。用戶不需要輸入繁瑣的計算公式,只需輕松點擊幾下按鈕,就可以輕松得到測量結果。

此外,EZwave還提供了一個功能強大的波形處理工具:Waveform Calculator,用戶可以通過這個工具,利用各種內置的函數算法,來對信號波形做各種快速轉換。例如求解信號的相位噪聲、對信號進行傅里葉變換等。

審核編輯:劉清

-

仿真器

+關注

關注

14文章

1016瀏覽量

83632 -

SPEC

+關注

關注

0文章

31瀏覽量

15783 -

信號仿真

+關注

關注

0文章

11瀏覽量

8576

原文標題:利用HyperLynx SI對復雜拓撲信號進行高效仿真測量

文章出處:【微信號:gh_a47ef5dbc902,微信公眾號:西門子PCB及IC封裝設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請問利用SPICE模型能不能進行PCB的SI仿真?

PCB SI介紹

HyperLynx仿真與PCB設計!高速PCB熱仿真

HyperLynx DRC功能和優勢

【轉載】Allegro SI 高速信號完整性仿真連載之三(附詳細流程)

求助,請發送在Hyperlynx軟件中進行SI分析所需的IBIS模型

利用SPICE模型能不能進行PCB的SI仿真?

利用Cadence Allegro PCB SI進行SI仿真分析

AN4803 在STM32微控制器上使用IBIS高速SI仿真和使用HyperLynx-SI進行板級仿真

如何利用HyperLynx SI對復雜拓撲信號進行高效仿真測量?

如何利用HyperLynx SI對復雜拓撲信號進行高效仿真測量?

評論