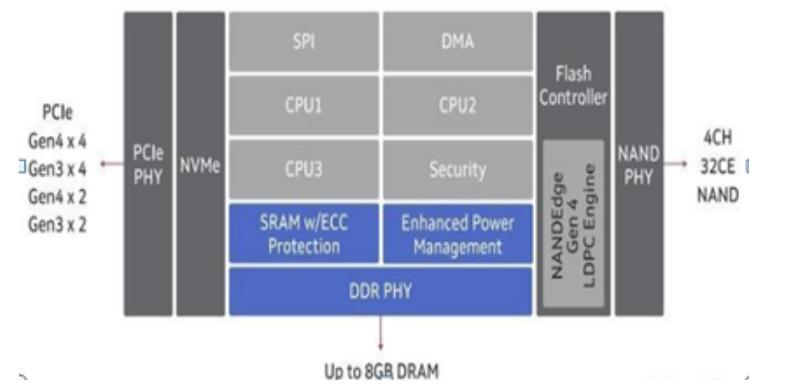

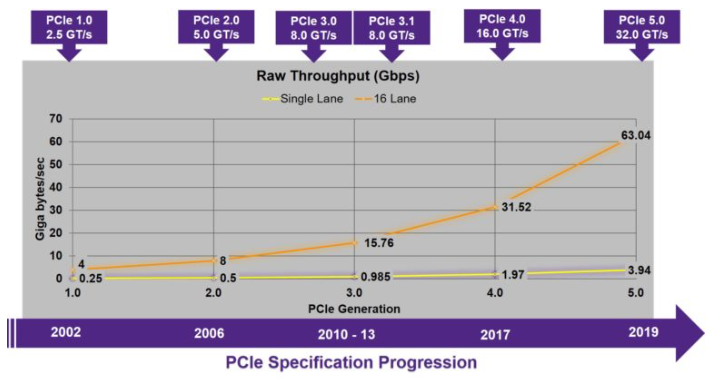

PCIe 5.0是當前最新的PCI Express規范,提供了更高的數據傳輸速率和更大的帶寬。

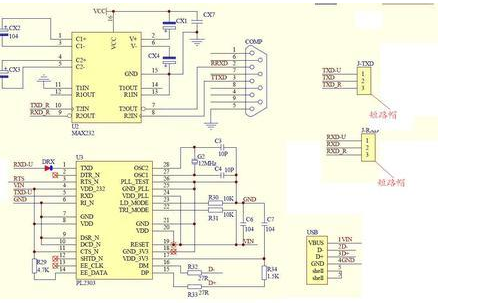

PCIe是連接兩個芯片的接口,負責兩個芯片通信, 連接芯片的通路為高速SerDes, 稱之為鏈路。PCIe確保通路正常-鏈路訓練狀態機。

PCIe在芯片內部是非常重要的一個大的模塊,如果PCIe不能正常工作,那芯片則視為石頭。

01 PCIe 5.0學習問答

Q :RC中幾個端口,是否可以進行P2P間的驗證?

解答 :看RC的具體實現,比如有些RC內部只有一個port也就不能進行p2p,之前做過這樣的設計采用dual ip,這樣就只有一個port,目前x86 RC內部port多,支持p2p,具體看下CPU Feature。

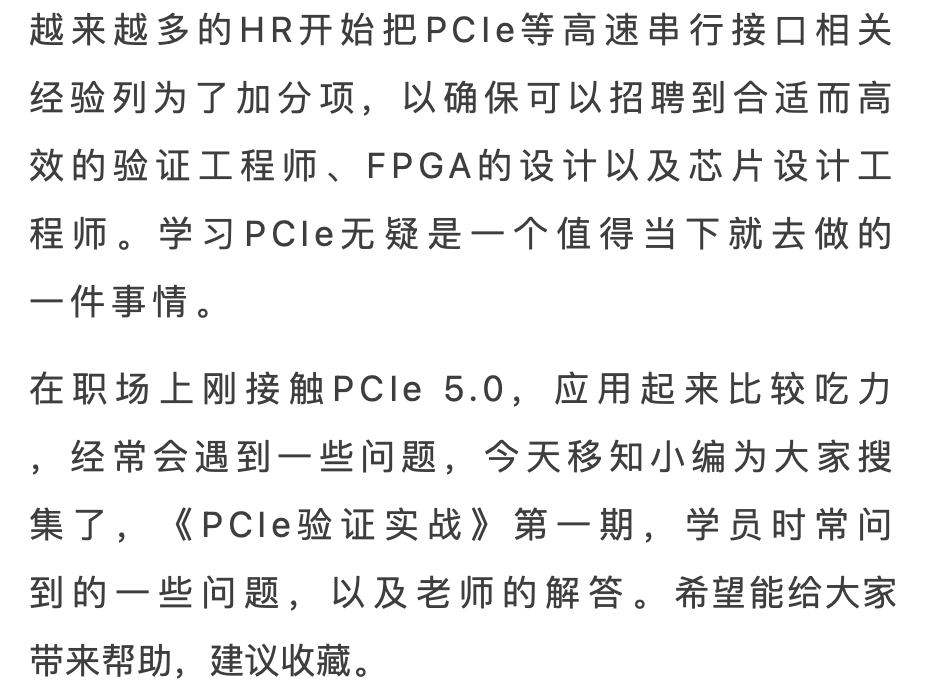

Q :PCIe鏈路訓練均衡的問題;如何配置Synopsys的EP控制器的寄存器,使得在鏈路訓練過程中修改HOST側的PCIE PHY的TX preset值。GEN3_RELATED_OFF寄存器GEN3_EQ_CONTROL_OFF寄存器,通過配置EP的這兩個寄存器配置是否可以實現,修改HOST側的TX preset值。

解答 :

1-EQ流程,RX會根據CTLE/DTE評估的情況來調節對端設備的TX FFE。

2-源碼分析,不能按照問題操作

3-需要仿真-doing

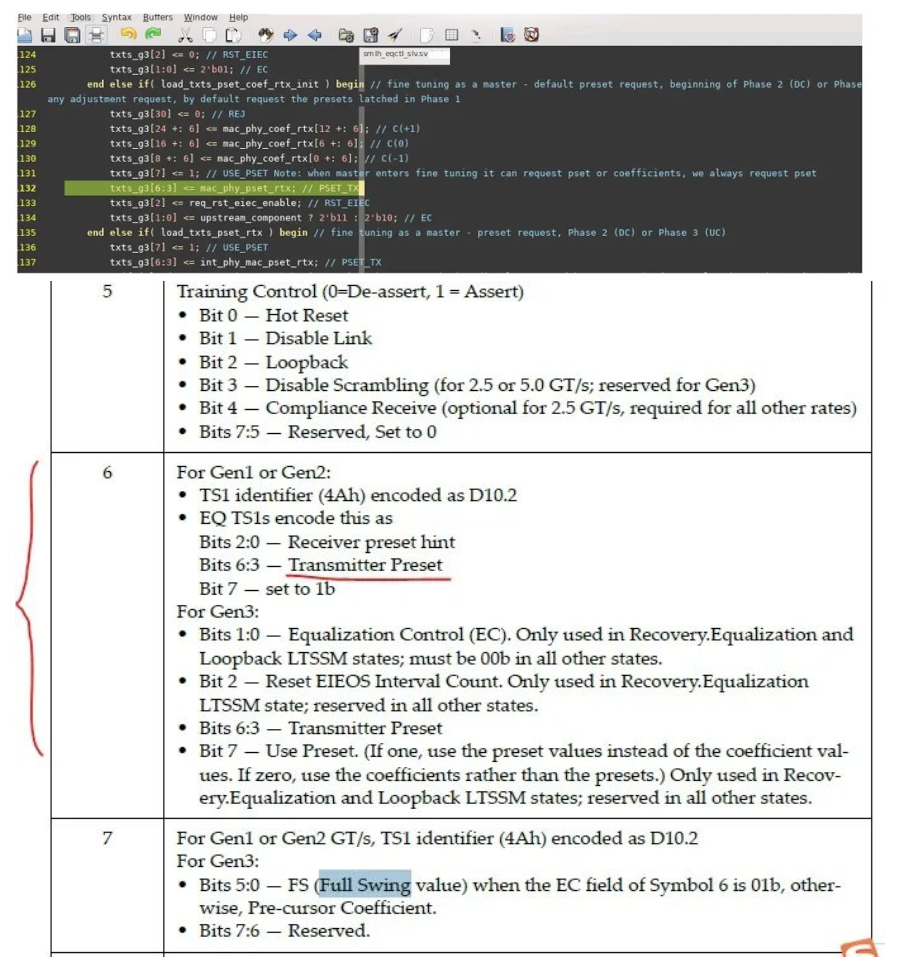

Q :EP在detect的時候TS1發出的 datarate只支持GEN1, 最終EP 和RC也training到GEN1 ,但此時發現 RC target speed 也切到GEN1 ,這個過程是哪一部分會修改到RC的target speed嗎?

解答 :

1-bios到是有可能;我見過原型驗證中有通過bios修改cpl timeout。

2-需要確認controller此寄存器會不會硬件自動修改,RTL代碼確認不會修改。

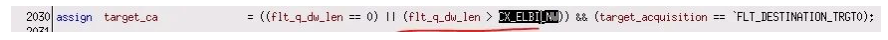

Q :cxl下rc remote訪問EP的MEMBAR0下掛的ELBI接口空間支持2DW讀?

解答 :

不支持,RTL代碼返回CA

cxl文檔里有一個ELBI2的方式,ELBI2將1K-DW(ELBI)擴展到512K-DW,這也是訪問CCG Reg的方式。ELBI的空間太小,不滿足要求。因此2dw的訪問是ELBI2可以支持的,只是ELBI方式不支持。

Q :目標為16G,請問老師,LTSSM為什么跳過了5G,直接進入8G?

解答 :

到16G的訓練流程就是2.5-8-16,pcie vip還提供了一種配置直接2-16.

6.0spce看到過這方面內容的描述。

Q :PCIE序的場景,需要列舉

解答 :

讀不超越寫,請求依賴與響應因此響應不能依賴與請求,i響應包不能穿越P包(host讀tag,ep寫數據)。

-

控制器

+關注

關注

112文章

16214瀏覽量

177478 -

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

RTL

+關注

關注

1文章

385瀏覽量

59710 -

SerDes

+關注

關注

6文章

197瀏覽量

34860 -

PCIe接口

+關注

關注

0文章

120瀏覽量

9680

發布評論請先 登錄

相關推薦

硬盤開啟PCIe 5.0時代

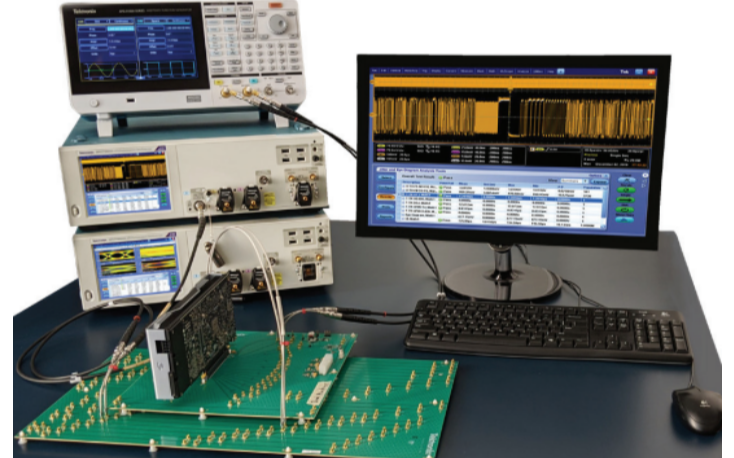

應對一致性測試特定挑戰,需要可靠的PCIe 5.0 發射機驗證

本本內存升級 要注意那些問題?

PCIe 5.0時代正式拉開序幕

PCIe 5.0對互聯芯片的性能驗證要求

什么是 PCIe 5.0? PCIe 5.0規范以及挑戰

microchip全新的PCIe 5.0交換芯片怎么樣

使用Synopsys VIP簽署PCIe 5.0驗證

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

PCIe 5.0驗證實戰,經常遇到的那些問題?

PCIe 5.0驗證實戰,經常遇到的那些問題?

評論