隨著 SoC 設計的復雜性與日俱增,SoC 的系統(tǒng)級功耗估算的重要性顯著提高。系統(tǒng)級 RTL 功耗分析有助于在設計階段的早期確定最壞情況下的系統(tǒng)功耗方案。RTL 功耗分析工具有助于分析大型設計的功耗,并且與門級分析相比,提供數(shù)據(jù)的速度要快得多。

.lib、FSDB/SAIF/STW/QWAVE

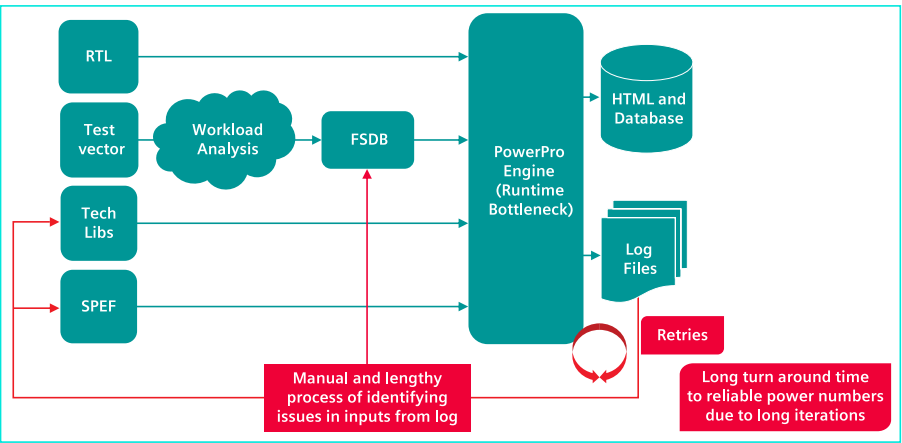

或SPEF等文件中的輸入數(shù)據(jù)如果存在問題,則針對大型系統(tǒng)的功耗估算可能造成嚴重的延遲(圖 1)。用戶可以插入檢查點檢查數(shù)據(jù)完整性來標記這些問題。這些檢查點有助于在用戶偏離目標太遠之前提前捕捉并修復問題,并且可以嘗試生成一次正確的功耗數(shù)據(jù),從而節(jié)省浪費在失敗的嘗試上的大量時間。

圖 1:舊方法

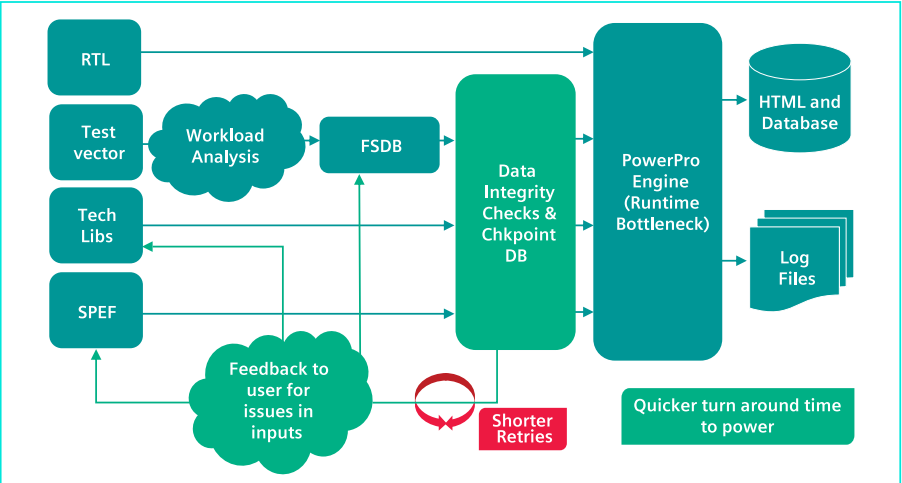

在設計構建和原型階段擁有一種自動輸入限定方法來執(zhí)行各種數(shù)據(jù)完整性檢查,這一點至關重要。這將確保在更快的迭代中,輸入數(shù)據(jù)仍具有高保真度,并產(chǎn)生具有相關性的功耗數(shù)據(jù)。 西門子 EDA 的 PowerPro 解決方案為 RTL 設計人員提供了全面的功能集來實現(xiàn)低功耗設計。PowerPro 提供適用于 RTL 和門級設計的功耗估算、可在 RTL 開發(fā)期間快速查找功耗問題的早期功耗檢查,以及可優(yōu)化功耗設計的時鐘和內存門控(圖 2)。

圖 2:新方法

審核編輯:湯梓紅

-

ARM

+關注

關注

134文章

9046瀏覽量

366817 -

soc

+關注

關注

38文章

4122瀏覽量

217938 -

SoC設計

+關注

關注

1文章

148瀏覽量

18762 -

RTL

+關注

關注

1文章

385瀏覽量

59701

原文標題:Arm 使用 PowerPro 的輸入限定方法

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

multisim簡單的電路可以限定布單層PCB嗎?

基于ARM平臺的MEMS輸入設備的固件設計

AutoCAD中輸入Φ的的常用方法

OPPO手環(huán)EVA限定版解析

KeilC51與MDK-ARM并存方法

Arm使用PowerPro的輸入限定方法

Arm使用PowerPro的輸入限定方法

評論