建立/保持時間對數字電路的影響

數字電路是指使用數字信號進行連接和處理信息的電路。數字電路是由一系列數字邏輯門和觸發器構成的,這些組件可以在特定的輸入下產生特定的輸出。時間是數字電路中不可忽略的因素之一,它對數字電路的運作和性能產生著重要的影響。在本文中,我們將探討時間與數字電路之間的關系,并分析它對于數字電路性能的影響。

數字電路包括各類邏輯門、計數器、觸發器和存儲器等多種器件,這些器件需要精準而穩定的時間來控制它們的運作。在數字電路的設計和測試過程中,時間對如何控制和檢測信號調制、處理和傳遞等方面有著至關重要的作用。數字電路的性能和工作效率都受到時間因素的直接影響。時間因素包括數字信號的傳輸速度、時序特性和時鐘脈沖的頻率等。

首先,時間對于數字電路中信號的傳輸速度至關重要。數字信號的傳輸速度取決于兩個因素:信號傳輸距離和信號傳輸介質。在任何情況下,數字信號的傳輸速度都有上限。因此,距離越遠,傳輸速度就會越慢。另外,不同的介質對數字信號的傳輸速度也有影響。例如,在同一距離下,光導纖維的傳輸速度比銅線電纜快得多。因此,在設計數字電路時,需要考慮信號傳輸速度和信號傳輸介質等因素,以確保數字信號的穩定和準確傳輸。

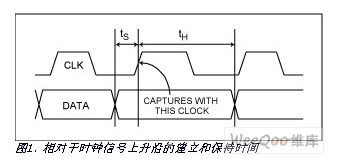

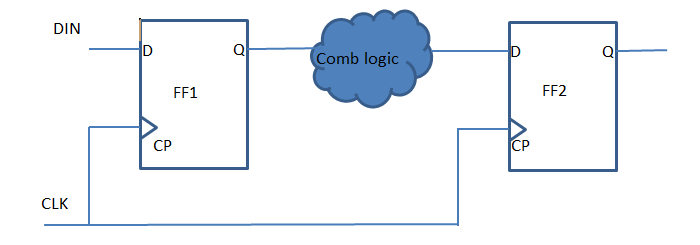

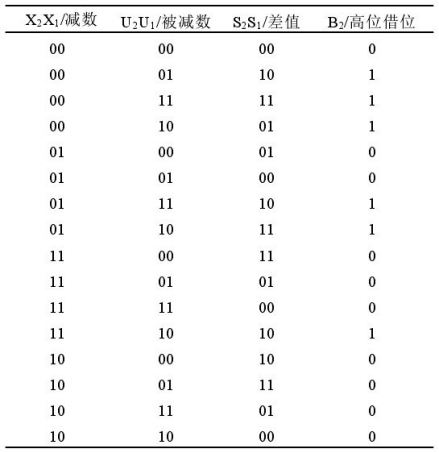

其次,時間對于數字電路的時序特性也非常關鍵。時序特性是一般電路中的一種行為,其功能是使不同的部分在正確的時間點進行正確的操作。在數字電路中,時序特性用于控制各類邏輯門、計數器、觸發器和存儲器等器件的操作。時序特性包括輸入信號的端到端延遲時間、邏輯門的延遲時間、時鐘脈沖的占空比和時鐘的頻率等參數。在設計數字電路時,這些時序特性要被精準的控制和預測,以確保數字電路的正確性和可靠性。

時鐘信號在數字電路中是非常常見的,它是由定時器產生的電信號,可以用來控制數字系統各個部件之間的同步和調度。時鐘信號頻率越高,數字系統的計算速度越快。在數字電路的設計中,時鐘信號的頻率應該和其他信號的速度匹配,以確保數字系統能夠正常工作。當時鐘信號的頻率過高時,數字電路會產生飽和或翻轉錯誤等問題;當時鐘信號的頻率過低時,則會導致數字電路慢速響應、計算速度下降等問題。因此,時鐘頻率也是數字電路中需要精確控制的參數之一。

最后,數字電路的性能和工作效率都受到時間因素的影響。數字電路的性能包括速度、功耗、可靠性和復雜性等方面。在設計數字電路時,需要考慮在特定的時間內完成特定的任務,并考慮滿足資源使用的最小延遲時間。對于工作效率來說,需要最大化數字系統的吞吐量并最小化資源的消耗。因此,在設計數字電路時需要仔細平衡這些參數,并合理配置電路的組件和結構,以實現數字電路性能和工作效率的最優化。

總的來說,時間是數字電路中非常重要的因素,它對數字電路的運作和性能產生著直接的影響。數字電路的設計和測試需要考慮數字信號的傳輸速度、時序特性和時鐘脈沖的頻率等因素,以確保數字電路的正確性、可靠性和工作效率。數字電路的設計和優化需要專業的知識和經驗,可以利用計算機模擬和仿真技術來幫助分析和預測數字電路的性能。最終目標是設計和生產出高性能、高效率和高可靠性的數字電路。

-

存儲器

+關注

關注

38文章

7452瀏覽量

163599 -

數字電路

+關注

關注

193文章

1600瀏覽量

80497 -

觸發器

+關注

關注

14文章

1995瀏覽量

61051

發布評論請先 登錄

相關推薦

數字電路可以處理模擬信號嗎

數字電路是對什么信號進行傳輸的

數字電路中的亞穩態是什么

數字電路和模擬電路的區別與聯系

數字電路仿真元件符號是什么

高速數模轉換器(DAC)的建立和保持時間

與模擬電路比數字電路的優點

數字電路和模擬電路的工作各有何特點?

關于建立時間和保持時間的測量方法

建立時間和保持時間對數字電路的影響

建立/保持時間對數字電路的影響

建立/保持時間對數字電路的影響

評論