我使用的是HVACI_sensorless_2833x的例程,它是使用IQ格式寫的,其實controlsuite里面大多數的例程都是用這個格式來做的,因為它有兩個優勢,首先運行速度快,使用于定點芯片,另一個是可移植性強。

但是我使用的是28335的板子,它是一款浮點計算為主的板子,我忽略了它的主要優勢,一直在跟IQ格式的使用較勁,雖然28335也支持定點格式,但是真正使用起來,卻遠遠不像浮點型那么方便,IQ格式需要你去估計參與計算的變量的數值大小,保證不會溢出,使用這個格式會多花費你一般的時間;我原本只是用來產生SVPWM波形,這個理論看了好幾遍,還是不太懂得,但要復述原理也能說得差不多,從這個例程里面,直接利用build1進行調節,就可以調出來馬鞍波。參考文件可以看這個例程里面的doc文件,這樣就可以解決第一步問題;

二、加鎖相環SRF-SPLL

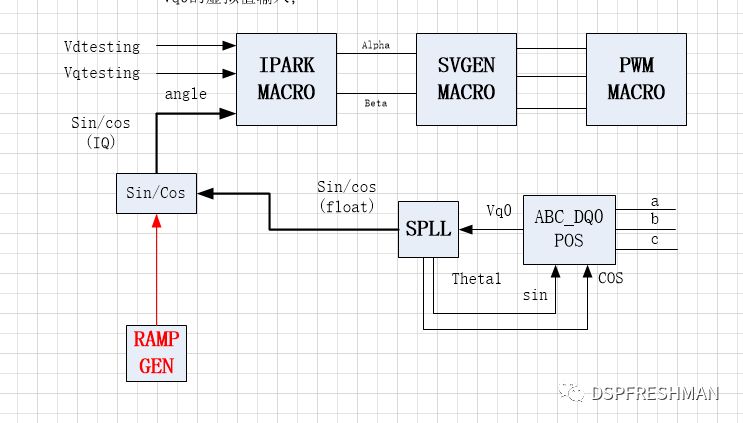

首先給出一張結構圖,我的想法大概是這樣的,實際操作之后證明是可行的;

由三相電壓進入,經過變換,然后把Vq值給到數字鎖相環,鎖相環產生sin/cos數值,給到ipark的輸入angle,然后經過SVGEN產生占空比,得到馬鞍波,紅色部分是用例程中程序直接調試的到的,黑色部分是我這一個月調試的過程,其中大部分時間都用來研究IQ格式了,現在還有好多不是太明白的地方,當然如果你也有遇到,可以跟我及時交流;這里面注意兩種格式變換的地方是在angle那里,由浮點變為定點,然后使用graph功能(初學的話這里也是一個會花費功夫的地方)來進行觀測;

三、注意的問題以及解決方法

我使用的SRF-SPLL是從TI論壇里面找到的參考程序

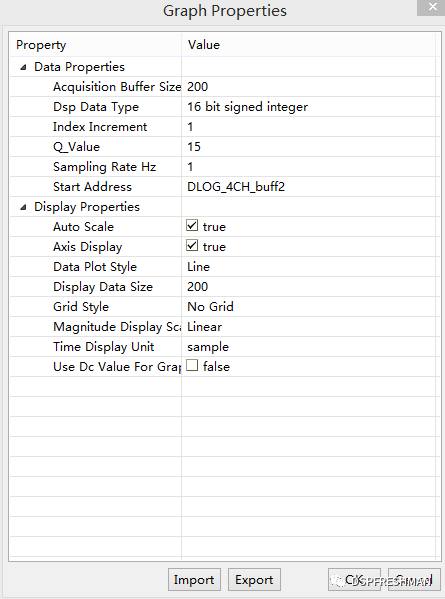

還有一個就是Graph功能的設置,下面給出一個基于本例程的正確的設置方法,如下圖所示:

當然,這只是幫助你少去走一些彎路,實際調試可能還會遇到很多問題;

還有一定,就是SPLL調用的文件,在初始化的時候,1/ISRfrequency是指的工程的采樣周期,不要真的把后面的值代入就完了。

-

鎖相環

+關注

關注

35文章

574瀏覽量

87462 -

數字鎖相環

+關注

關注

3文章

30瀏覽量

13390 -

SVPWM

+關注

關注

14文章

611瀏覽量

90414 -

三相電壓

+關注

關注

0文章

100瀏覽量

14287 -

SPLL

+關注

關注

0文章

3瀏覽量

9173

發布評論請先 登錄

相關推薦

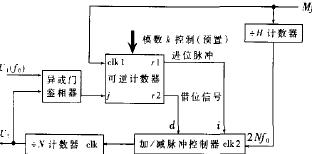

數字鎖相環設計步驟

CCS6.2 Graph圖像功能顯示的數值相差很多的原因?

智能全數字鎖相環的設計

數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

CCS6.2的詳細使用方法說明

如何在CCS6.2中調試SRF數字鎖相環?

如何在CCS6.2中調試SRF數字鎖相環?

評論