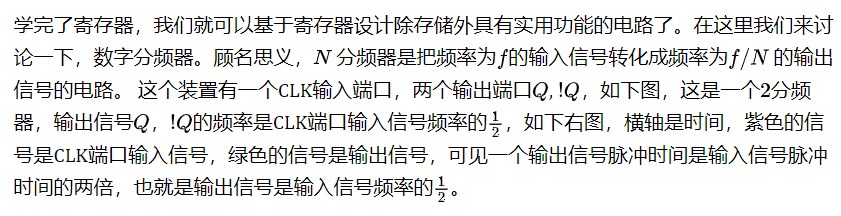

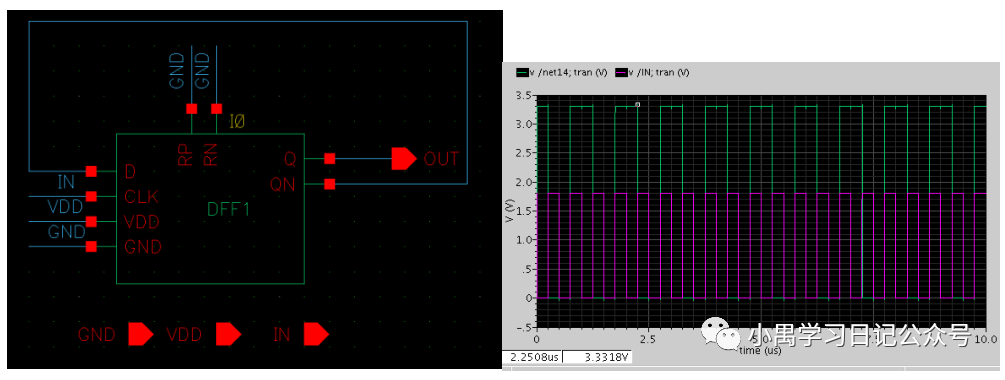

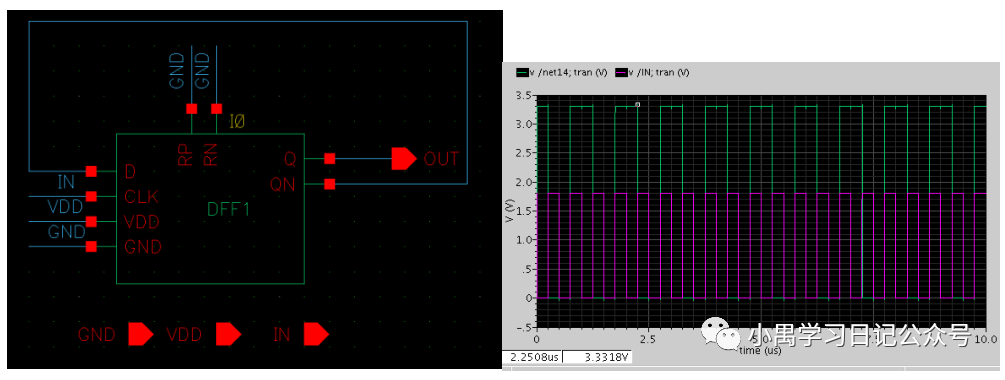

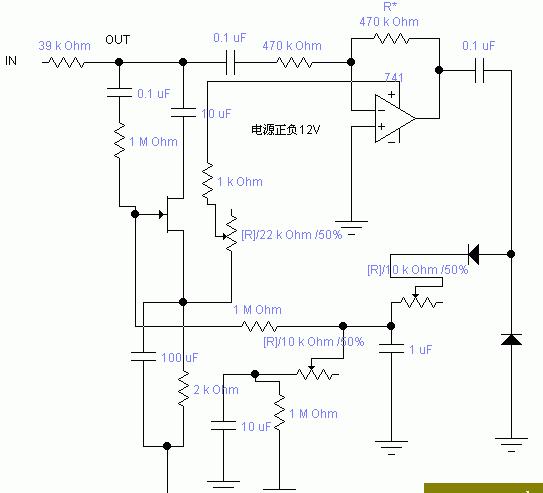

2分頻器電路圖,其中DFF1是D Flip Flop,即D觸發器;右邊是輸入輸出信號圖

由于這篇文章有一定的技術含量,大家不一定能一口氣全讀完。因此先討論本來寫在結尾的閑談。關于分頻器,就我目前的接觸主要是在時鐘綜合器、鎖相環等時鐘相關的模塊中看到分頻器,在FPGA等數字IC或者RFIC中也有用到分頻器。

為了了解分頻器的重要性,我們來看一個實例,石英晶振,通過這個例子,我們還能知道時鐘信號為什么被稱為時鐘信號了。

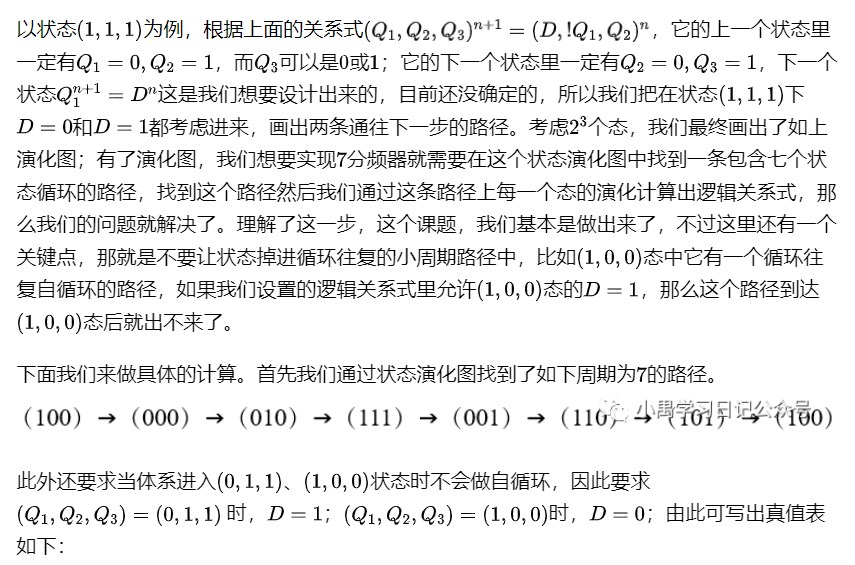

石英晶振是一種基于壓電效應的振蕩器,壓電也就是說施加在石英上的壓力會轉化成電壓,電壓會轉化成對石英的壓力。

通過這個特性,我們石英晶振接在一個反向放大電路后,石英晶振就會產生振蕩信號(關于震蕩信號的產生,我們會在之后的振蕩器章節再進行系統地討論)。

(專業人士可能會想了解分數分頻器,不過分數分頻器一般是通過FPGA來實現,它是通過Verilog代碼綜合出電路;在這里我們由于當前還沒學會Verilog綜合,因此沒有實際可供參考的模擬分數分頻器電路來做研究,因此沒法通過模擬IC的方法直接搭建分數分頻器。)

2分頻器電路圖,其中DFF1是D Flip Flop,即D觸發器;右邊是輸入輸出信號圖

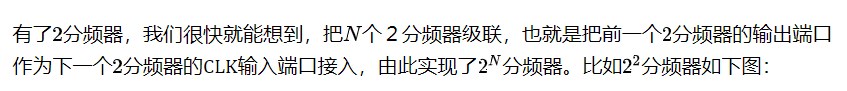

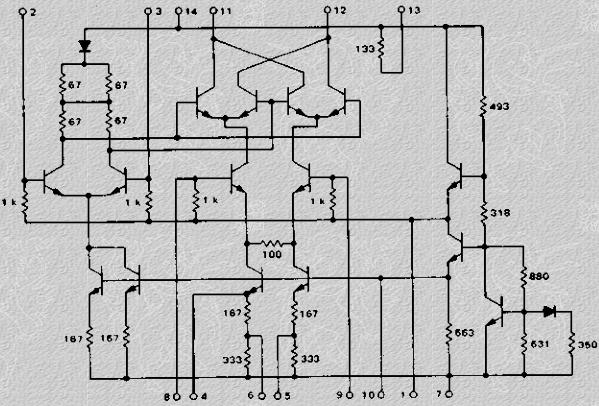

分頻器的原理圖與輸入輸出信號對比圖

3. 任意整數N分頻器的構建

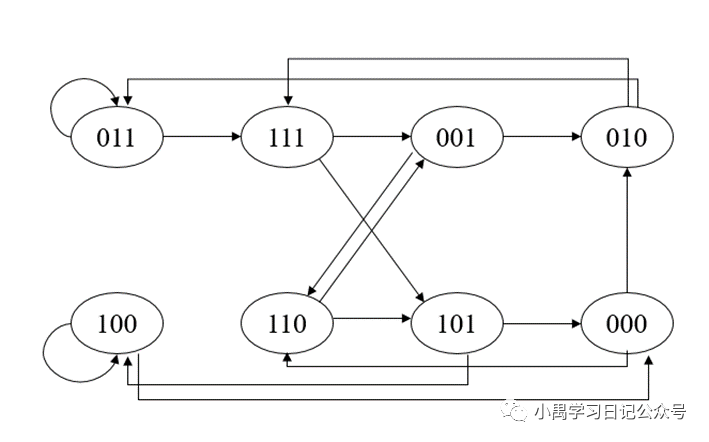

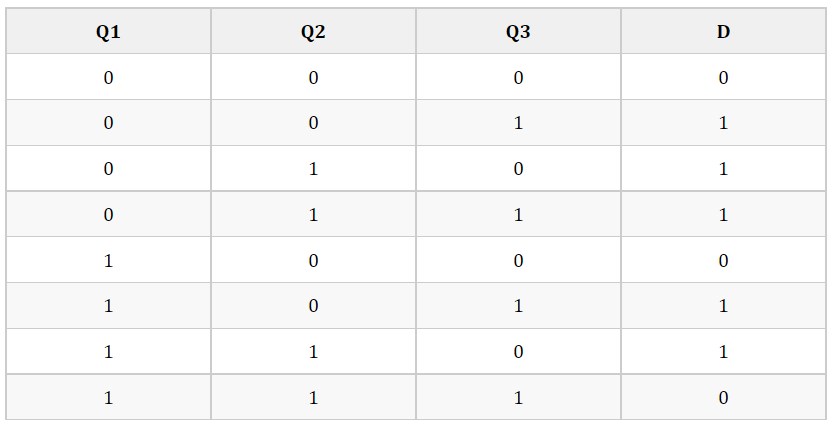

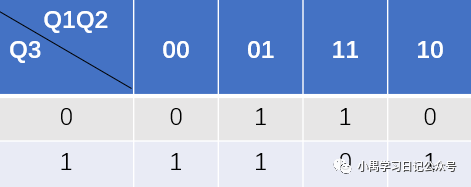

有了真值表,我們就能得到卡諾圖如下:

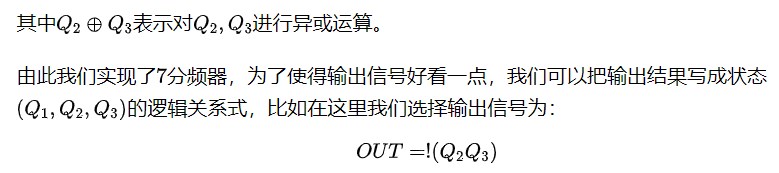

進一步計算出邏輯關系式:

或者可以省去與符號寫成:

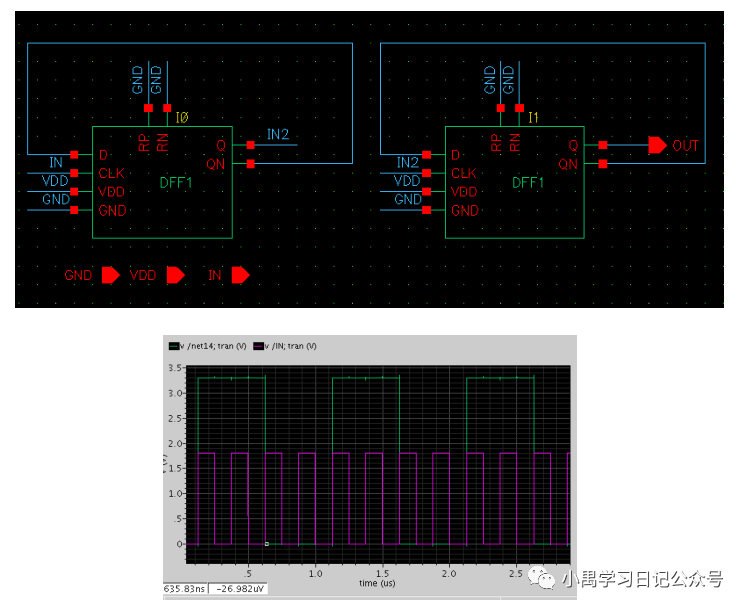

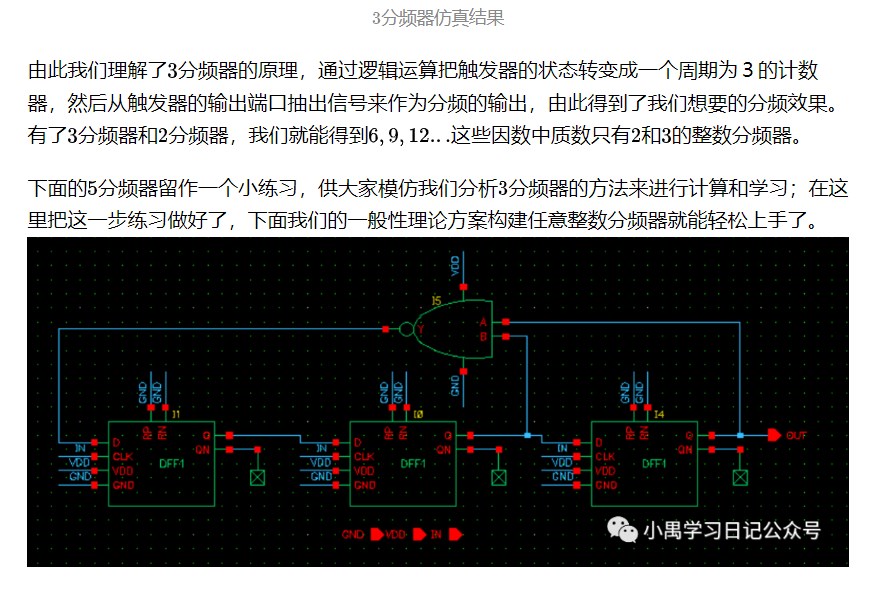

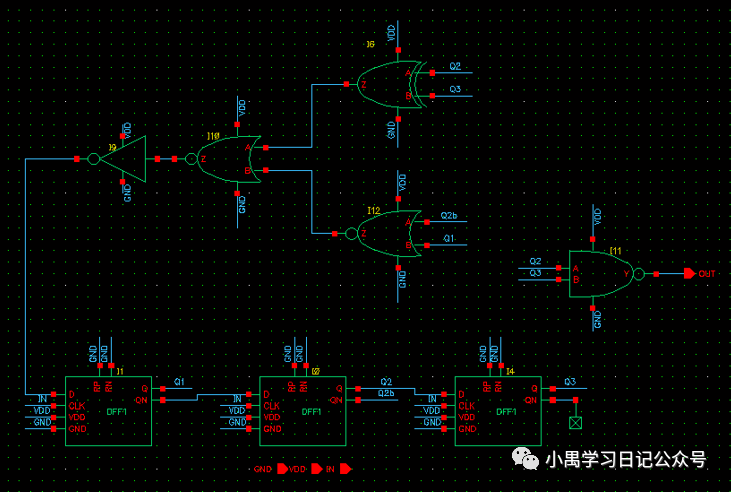

原理圖如下:

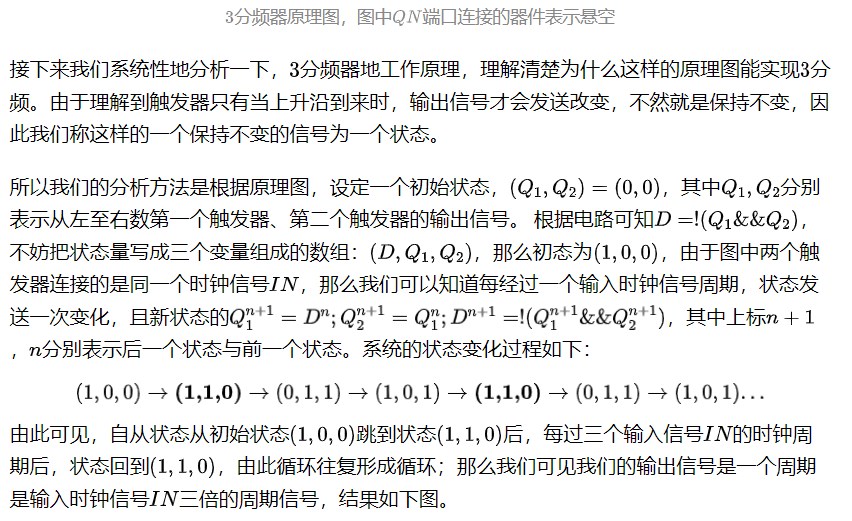

分頻器原理圖

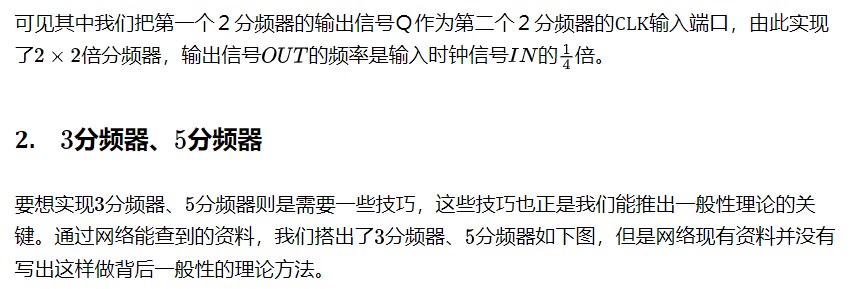

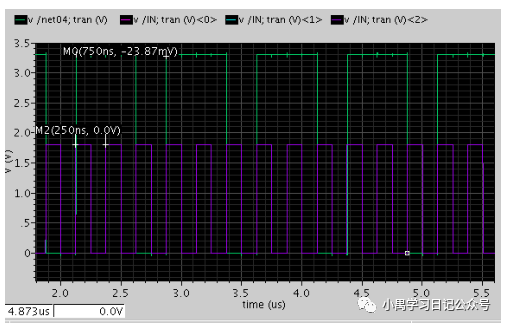

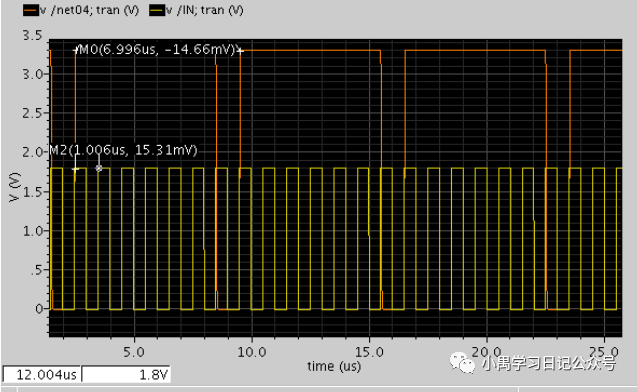

分頻器仿真結果

-

鎖相環

+關注

關注

35文章

583瀏覽量

87694 -

IC設計

+關注

關注

37文章

1291瀏覽量

103768 -

分頻器

+關注

關注

43文章

447瀏覽量

49814 -

觸發器

+關注

關注

14文章

1996瀏覽量

61052 -

狀態機

+關注

關注

2文章

492瀏覽量

27478

發布評論請先 登錄

相關推薦

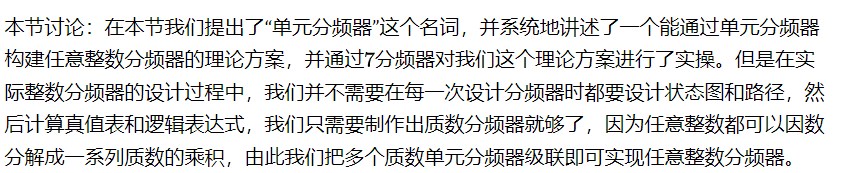

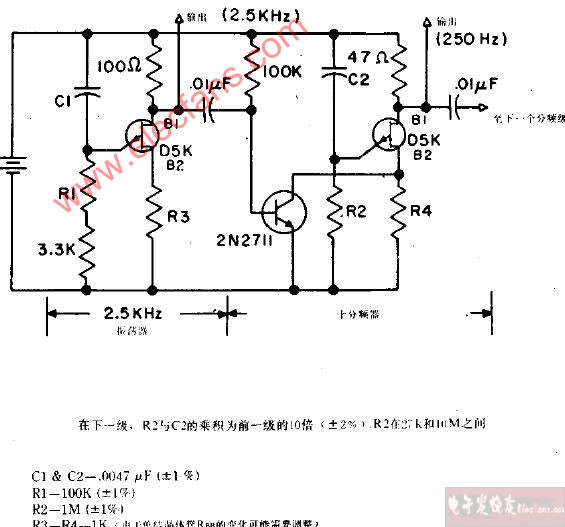

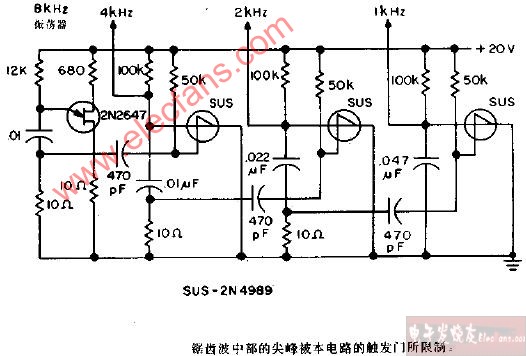

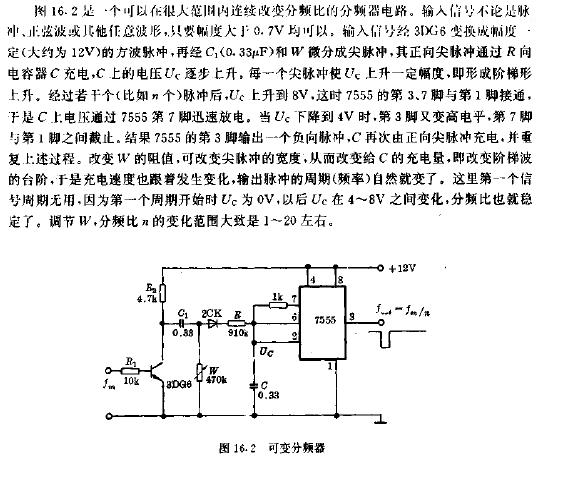

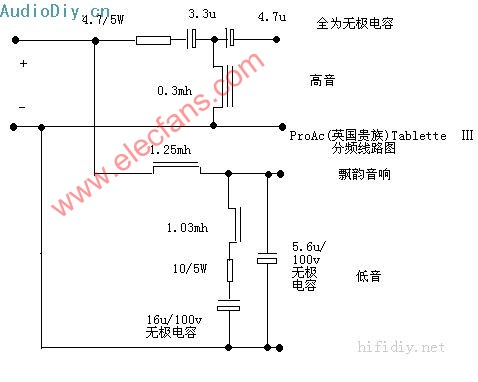

電子分頻器電路圖大全(六款電子分頻器電路設計原理圖詳解)

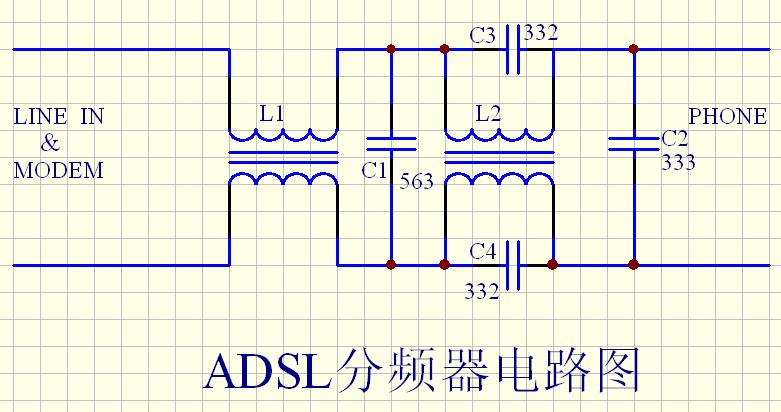

分頻器的作用是什么 半整數分頻器原理圖分析

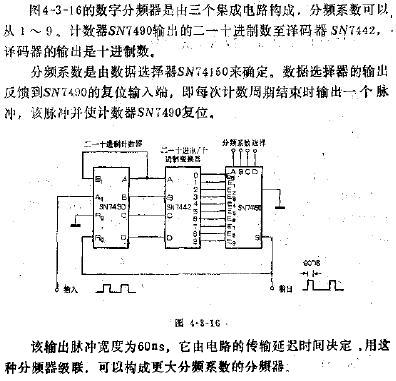

模擬IC設計原理圖3:數字分頻器的原理和電路原理圖

模擬IC設計原理圖3:數字分頻器的原理和電路原理圖

評論