高性能模擬電路中如果layout處理不好很容易惡化模擬電路性能,除了之前給大家介紹的版圖布局布線及電源網絡的劃分,還要留意LDE(Layout Dependent Effect),LDE主要包含STI(Shallow Trench Isolation)和WPE(Well Proximity Effect),本期重點介紹一下這兩種效應并簡單介紹一下其他layout相關效應,希望對大家有所幫助。

1. LDE

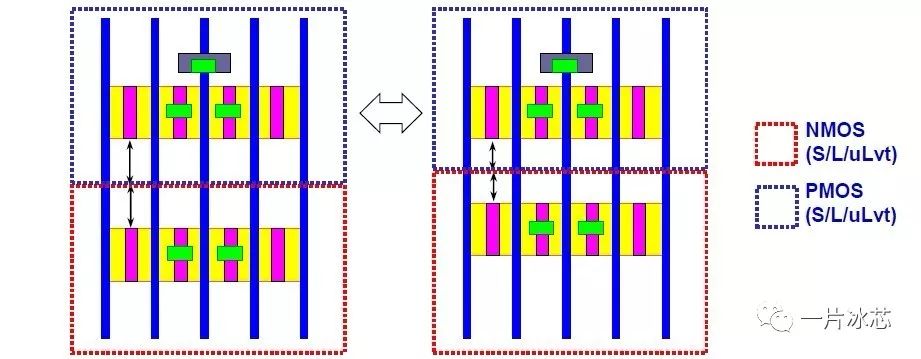

layout相關效應主要包含以下幾個方面:

其中LOD(Length of Diffusion)Effect,也稱為STI Stress Effect。下面章節將逐一展開layout相關效應。

2. 常見LDE****定義

2.1 LOD

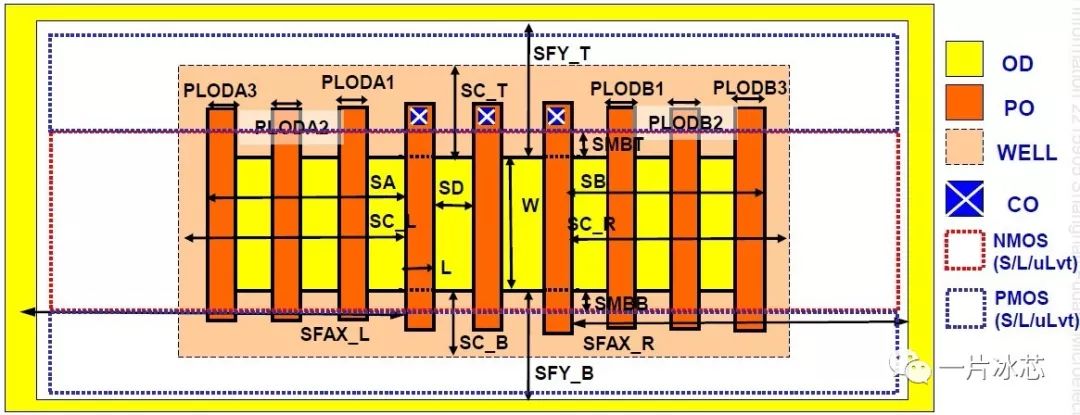

LOD(Length of Diffusion)Effect,也稱為STI Stress Effect,顧名思義就是有源區外的STI隔離會對其帶來應力作用,從而影響晶體管閾值電壓,通常用Poly到有源區邊界的距離(SA/SB,如Fig9所示)來描述,如圖1所示。

Fig1. LOD效應

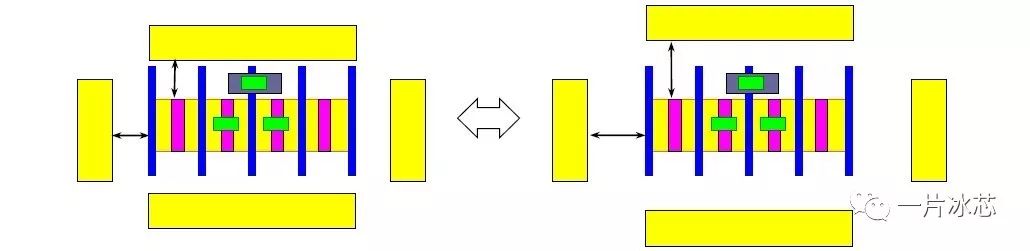

2.2 WPE

集成電路在制造過程中,對阱作離子注入時,注入的離子與阱區周圍的光刻膠發生濺射而富集在阱的邊緣,因而在水平方向呈現摻雜濃度的非均一性,這會導致阱區中的MOS管的閾值電壓隨晶體管與阱邊緣的距離(SC_L/SC_R/SC_T/SC_B,如Fig9所示)而發生變化,這一特性稱為WPE,如圖2所示。

Fig2. WPE效應

2.3 OSE

OD到OD之間的距離(SFAX_L/SFAX_R/SFAX_T/SFAX_B,如Fig9所示)也會影響晶體管特性,這一特性稱為OSE,如圖3所示。

Fig3. OSE效應

2.4 PLE

Length長度(PLODA1/PLODA2/PLODA3/PLODB1/PLODB2/PLODB3,如Fig9所示)也會影響晶體管特性,這一特性稱為PLE,如圖4所示。

Fig4. PLE效應

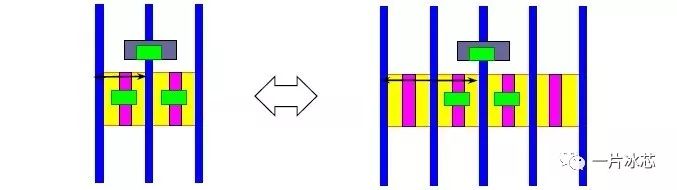

2.5 MBE

N/P管金屬邊界之間的距離(SMBT/SMBB,如Fig9所示)也會影響晶體管特性,這一特性稱為MBE,如圖5所示。

Fig5. MBE效應

2.6 OJE

拐角的OD與非拐角OD也會影響晶體管特性,這一特性稱為OJE,如圖6所示。

Fig6. OJE效應

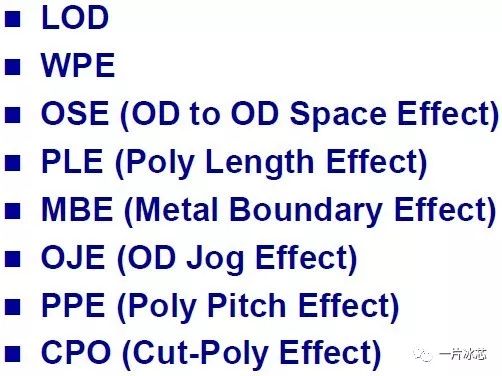

2.7 PPE

Poly之間的pitch也會影響晶體管特性,這一特性稱為PPE,如圖7所示。

Fig7. PPE效應

2.8 CPO

Poly Cut的位置也會影響晶體管特性,這一特性稱為CPO,如圖8所示。

Fig8. CPO效應

2.9 LDE Summary

2.1~2.8節中的LDE總結如下圖9所示。

Fig9. LDE Summary

圖中參數說明如下:

前后仿網表中LDE相關參數如下:

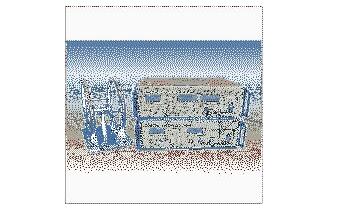

3. 項目中的LOD****問題

圖10為lcvco中的偏置電路,后仿發現ss_lvlt(ss低溫低壓)corner下lcvco振蕩頻率偏小。為了debug這一問題,嘗試了很多方法,前仿時偏置電流由50uA加大到100uA發現與后仿現象一致,因此懷疑后仿時注入lcvco的電流偏大引起lcvco振幅偏大,進而使lcvco中等效并聯電容偏大,降低了振蕩頻率。

后仿發現ss_lvlt corner下M1管的閾值電壓偏大,導致M1管源端電壓低到70mV,而M4管源端電壓為200mV,由于溝道長度調制效應,使得流過M4管的電流偏大,進而降低了lcvco振蕩頻率。

查看layout發現M1管兩側未加dummy管,有源區邊界處的STI隔離產生的應力使得M1管閾值電壓偏大,M1管兩側加dummy后,再次后仿發現ss_lvlt corner下lcvco振蕩頻率正常。

Fig10. lcvco中的偏置電路

4. 減小LDE****方法

①減小阱的個數,將同一電位的器件放在一個阱里,適當拉大有源區到阱邊界的距離,NMOS距離阱邊界較近時,閾值電壓會增大50mV,當距離拉大到3um以上,閾值電壓基本不受影響;②提高管子的對稱性并加入dummy,減小STI應力的同時增大了非dummy器件到阱邊界的距離;③對于高性能模擬電路而言,盡可能保持管子周圍及自身環境(包括OD到OD間的距離、Poly長度等)一致。

-

晶體管

+關注

關注

77文章

9634瀏覽量

137849 -

Layout

+關注

關注

14文章

402瀏覽量

61656 -

偏置電流

+關注

關注

1文章

116瀏覽量

13124 -

閾值電壓

+關注

關注

0文章

73瀏覽量

51365 -

CPO

+關注

關注

0文章

17瀏覽量

168

發布評論請先 登錄

相關推薦

介紹一下EMC相關知識

簡要介紹一下Python-UNO的使用方法

什么是巨磁電阻效應_巨磁電阻效應的應用介紹

詳細介紹一下ACM的優點資料下載

介紹一下Layout相關效應

介紹一下Layout相關效應

評論