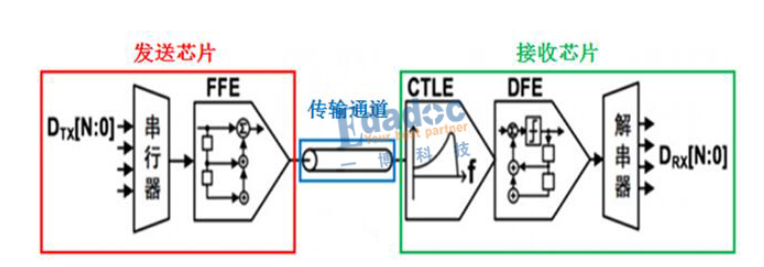

傳統(tǒng)CML結(jié)構(gòu)的CTLE基于源極退化電阻電容實(shí)現(xiàn)均衡,當(dāng)速度提高到56Gb/s或者112Gb/s時(shí)CML-based CTLE面臨速度、面積、功耗的巨大壓力(即使到了7nm工藝節(jié)點(diǎn)),本期介紹一種Inverter-Based CTLE以解決傳統(tǒng)CTLE的不足。

1 從ISSCC2020看SerDes****未來(lái)

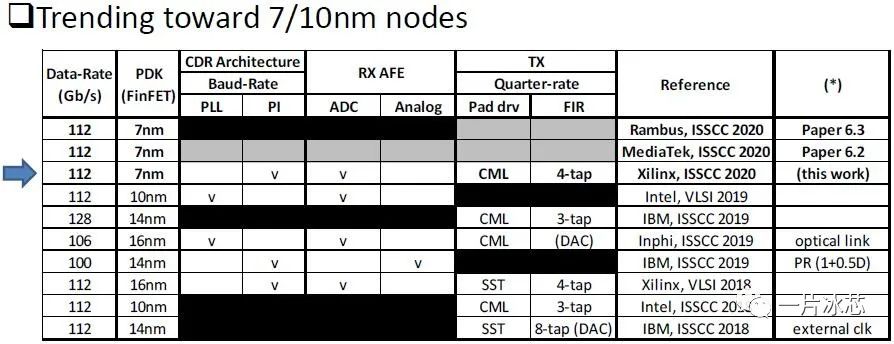

ISSCC2020 SESSION 6第一篇文章 ,是FPGA老大哥Xilinx發(fā)表的。圖1給出了近三年(2018-2020)學(xué)術(shù)界或工業(yè)界發(fā)表的100Gb/s以上SerDes結(jié)構(gòu),我們可以得到以下結(jié)論:

① CDR采用PI-based雙環(huán)路結(jié)構(gòu)成為主流,雙環(huán)路結(jié)構(gòu)的優(yōu)點(diǎn)是PLL環(huán)路(PI時(shí)鐘)和CDR環(huán)路可以相互獨(dú)立,同時(shí)多條Lane可共用同一時(shí)鐘源,節(jié)約了功耗和面積;

② RX的DFE均衡變成了ADC+DSP結(jié)構(gòu),將復(fù)雜的均衡放到數(shù)字域去處理,減小PVT影響,同時(shí)便于工藝遷移;

③ 更多TX Driver采用CML結(jié)構(gòu)(相對(duì)SST),因?yàn)镃ML結(jié)構(gòu)在速度上具有優(yōu)勢(shì);

④ 高速SerDes(56Gb/s+)具有超高的技術(shù)壁壘,玩家基本都是國(guó)外巨頭,國(guó)內(nèi)任重道遠(yuǎn)。

Fig1. 近三年100+ Gb/s SerDes結(jié)構(gòu)

2 Inverter-BasedAFE結(jié)構(gòu)

圖2給出了112Gb/s RX sub-system,圖中陰影部分的數(shù)據(jù)和時(shí)鐘通路采用CMOS實(shí)現(xiàn)。那么CTLE和PGA如何用CMOS實(shí)現(xiàn)?本文為了提高速度提出了Inverter-Based CTLE和PGA 。

Fig2. RX sub-system

傳統(tǒng)RC源極退化CTLE在112Gb/s速率下要保證帶寬和線(xiàn)性度變得異常艱難,因?yàn)閭鹘y(tǒng)CTLE結(jié)構(gòu)較復(fù)雜,電源到地通路堆疊的晶體管或電阻較多而且要在低電源電壓下保證線(xiàn)性度,為了提高CTLE線(xiàn)性度我們只能進(jìn)一步減小晶體管或電阻數(shù)目,減到最后不就變成Inverter了嗎?

圖3給出了112Gb/s RX sub-system中Inverter-Based CTLE結(jié)構(gòu)圖,合理設(shè)置輸入輸出管的共模電壓和擺幅可得到線(xiàn)性增益,在負(fù)載管柵端(圖中g(shù)m,hf和g m,lf )增加RC低通濾波器可實(shí)現(xiàn)peaking,采用有源電感(圖中g(shù) mL )實(shí)現(xiàn)帶寬拓展,具體工作原理詳見(jiàn)第3章。

Fig3. Inverter-Based CTLE結(jié)構(gòu)圖

論文提出Inveter-Based CTLE全部采用純CMOS實(shí)現(xiàn)(無(wú)電阻、電容、偏置、共模反饋),layout非常規(guī)整(Xilinx稱(chēng)之為“sea of gates”),如圖4所示。單級(jí)CTLE面積僅為30 um*15 um,而且性能表現(xiàn)卓越。

Fig4. CTLE layout

3 Inverter-Based CTLE****原理

3.1 不同模式下 Inverter的小信號(hào)模型

文獻(xiàn)[2]給出了Inverter工作在不同模式下的小信號(hào)模型,如圖5所示,不同模式下的Inverter可以充當(dāng)跨導(dǎo)、電阻以及有源電感。

Fig5. 不同工作模式下的Inverter及其等效模型

3.2 CTLE實(shí)現(xiàn)及仿真結(jié)果

將圖5原理應(yīng)用到圖6所示電路可得其低頻增益為g m1 /g ml ,高頻增益為(g m1 +g m2 )/2g ml ,合理設(shè)置三者gm可實(shí)現(xiàn)CTLE均衡功能。

Fig6. Inverter-Based CTLE電路及仿真結(jié)果

文獻(xiàn)[3]在文獻(xiàn)[2]的基礎(chǔ)上做了改進(jìn),提出了一種subtractive CTLE,將原來(lái)的additive CTLE的MOM飛電容(Flying capacitor)變成對(duì)地MOS電容,減小了面積,提高了線(xiàn)性度,但增大了功耗(典型的功耗換性能),如圖7所示。

Fig7. Comparison of (a) additive and (b) subtractive CTLE circuit Inverter-Based

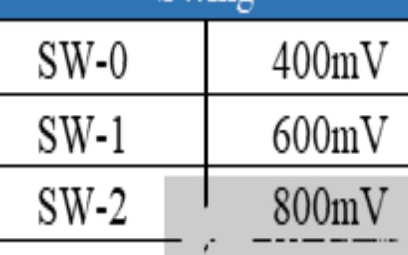

圖8給出了Inverter-based單位增益放大器的大信號(hào)分析,為了在PVT下保證放大器的線(xiàn)性度,要求輸入信號(hào)擺幅小于±300mV @ V DD =1.2V, V T =400mV。

Fig8. Inverter-based unity-gain stage for large-signal analysis

**4 **思考與討論

① Inverter-Based CTLE變成了偽差分結(jié)構(gòu),對(duì)偶次諧波的抑制減弱,這在工程中是否引入較大的失真?

② 為了保證Inverter-Based CTLE的線(xiàn)性度,都采用了什么技術(shù)?

③ FinFET工藝和Bulk工藝下實(shí)現(xiàn)Inverter-Based CTLE有何區(qū)別?

④ 如何實(shí)現(xiàn)Inverter-Based CTLE高低頻增益可配?

-

CMOS

+關(guān)注

關(guān)注

58文章

5603瀏覽量

234233 -

晶體管

+關(guān)注

關(guān)注

77文章

9404瀏覽量

136653 -

DSP芯片

+關(guān)注

關(guān)注

9文章

144瀏覽量

29831 -

CML

+關(guān)注

關(guān)注

0文章

32瀏覽量

19109 -

ADC采樣

+關(guān)注

關(guān)注

0文章

134瀏覽量

12778

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA高速收發(fā)器的高速Serdes均衡技術(shù)

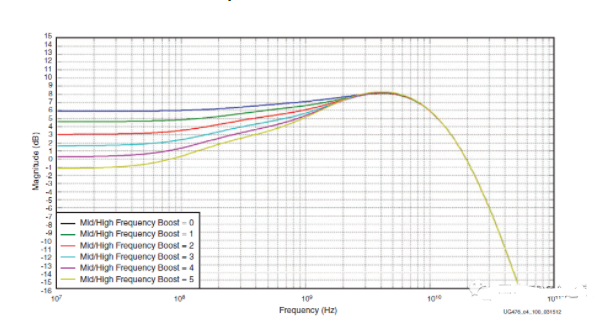

#CTLE技術(shù)#眼圖#示波器 CTLE技術(shù)和運(yùn)用過(guò)程的演示,讓閉合眼圖重新打開(kāi)

淺析FFE均衡技術(shù)

淺析均衡器CTLE

Inverter的工作原理介紹

Frequency Inverter Based Drawi

一種實(shí)用的背景提取與更新算法

Z-Source Inverter for Power Co

以PC Based Controller設(shè)計(jì)Modbus通信

如何設(shè)置CTLE模擬以優(yōu)化接收器眼圖開(kāi)度

CTLE是什么?(原理、特點(diǎn)及作用)

解析DP1.4物理層測(cè)試

一種Inverter-Based CTLE以解決傳統(tǒng)CTLE的不足

一種Inverter-Based CTLE以解決傳統(tǒng)CTLE的不足

評(píng)論