**1 **應用背景

板卡上的芯片需要相互通信,IO接口電平越豐富,芯片通用性越強。以28 nm工藝為例,IO device最高可耐1.98V,core device最高可耐1.0V,而IO電平需要同時滿足1.2V, 1.5V, 1.8V, 2.5V, 3.3V,這就需要設計一款寬輸入電壓范圍耐壓結構的IO模塊。

**2 **Widerange voltage translation

該專利介紹的是一種寬輸入范圍(1.2V~3.3V)的level-shift,為滿足如此寬的電壓輸入,將電路分成了兩種工作模式,一種是高壓模式(>1.8V),一種是低壓工作模式(≤1.8V),兩種模式的切換是由BIAS GENERATION SEGMENT控制,下面我們分別介紹這兩種工作模式。

2.1 高壓模式(2.5V, 3.3V)

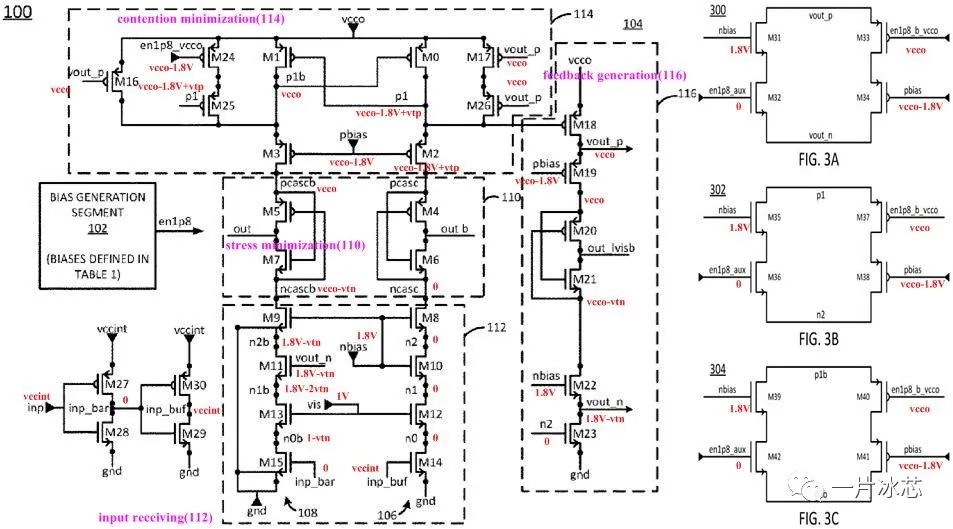

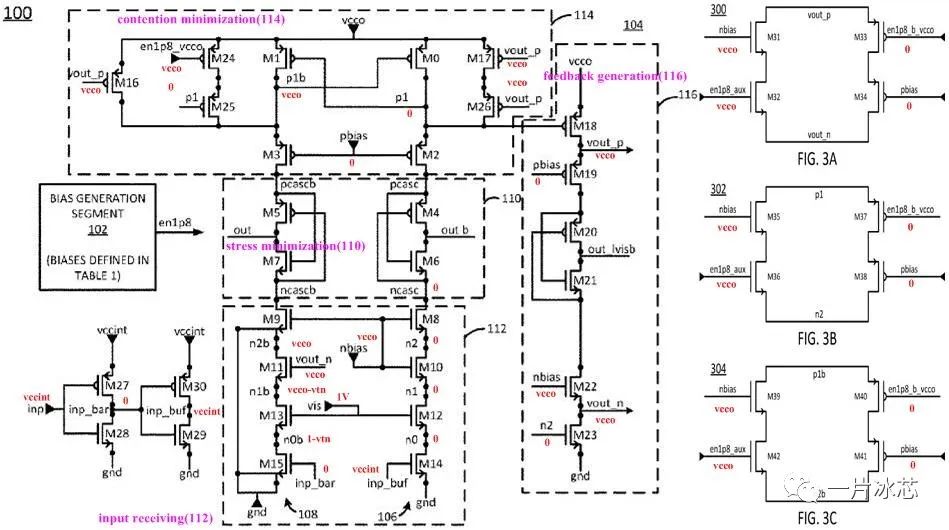

圖1給出了寬輸入level-shift高壓模式(2.5V, 3.3V)電路,圖中M14M15和M27M30為core device,最高工作電壓為0.925V,其他器件均為高壓管(IO device),最高工作電壓為1.89V,vtn和vtp分別為IO device n管和p管的閾值電壓,vcco為IO電源(1.2V3.3V), vccint(0.65V0.925V)為芯片內部數字邏輯電源,BIAS GENERATION SEGMENT中還有一個輔助(auxiliary)電源vccaux(本講不涉及此電源)。

整體電路(100)分為input receiving(112), stress minimization(110), contention minimization(114), feedback generation(116)以及BIAS GENERATION SEGMENT(102)。

其中BIAS GENERATION SEGMENT沒有給出具體電路,只給出了不同模式下的輸出電壓,如表1所示。高壓模式下pbias = vcco-1.8V, nbias = 1.8V, en1p8_vcco = vcco-1.8V, en1p8_aux = 0V,en1p8_b_vcco = vcco, vis = 1V,這些電位是用于保護IO device和core device。

圖1(a)標注了初始時刻inp為高電平(vccint,≤0.925V,如圖2 T1時刻)時關鍵節點的電平(紅色字體),可見初始時刻所有device不存在耐壓問題。其中inp為low voltage domain(vccint)level-shift輸入,vout_p為high voltage domain(vcco)level-shift輸出,初始時刻inp為vccint,vout_p為vcco,完成了不同電壓domain高(inp)到高(vout_p)的轉換。

該結構引入了input receiving(112), stress minimization(110), contention minimization(114)和feedback generation(116)等技術用于解決耐壓、速度、競爭等問題,專利中已經描述的非常詳細,有興趣的可以仔細閱讀。其中M0和M1的尺寸比為5:1(即M1較weak)且M17和M26也較M0 weak,這樣可以解決電平轉換時的高低電平競爭問題,使0→1或1→0的轉換更準更快。

(a)inp為高電平(vccint)工作原理

圖1(b)標注了初始時刻inp由高到低跳變(vccint, ≤0.925V,如圖2 T2~T3時刻)時關鍵節點的電平(紅 & 藍字體),inp由高到低跳變時所有device也不存在耐壓問題。low voltage domain的低電平為0V,high voltage domain的低電平為vcco-1.8V+vtp,完成了不同電壓domain高到低(inp)to高到低(vout_p)的轉換。

(b)inp由高(vccint)到低(0)跳變工作原理

Fig1. 寬輸入level-shift高壓模式(2.5V, 3.3V)電路

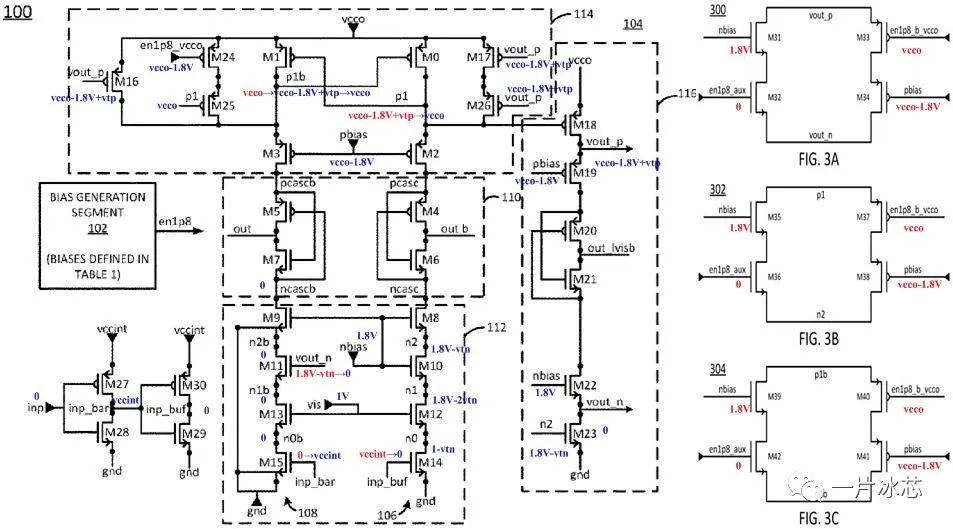

圖2給出了高壓模式下level-shift inp, p1, p1b, vout_p, vout_n的波形,其中T3T4的分析與T1T2類似,這里不再贅述。

Fig2. 寬輸入level-shift高壓模式(2.5V, 3.3V)波形

2.2 低壓模式(1.2V, 1.5V, 1.8V)

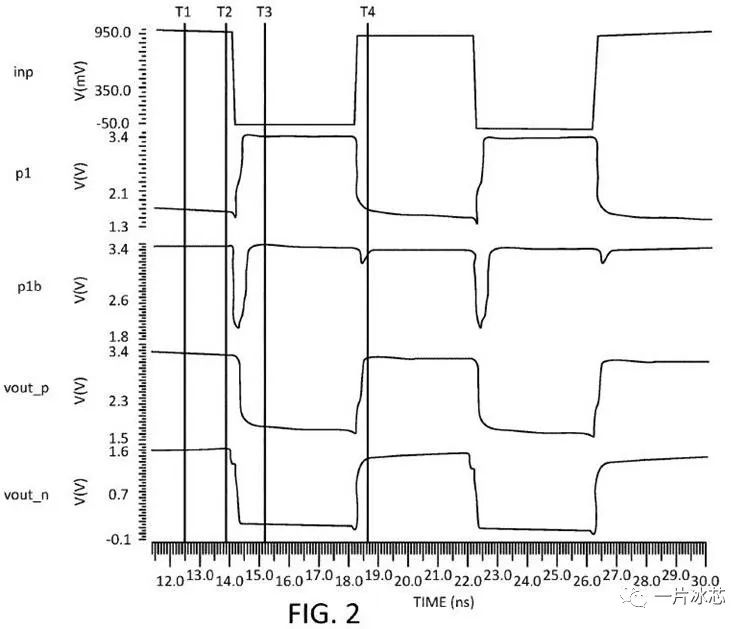

為節約芯片面積,低壓模式與高壓模式共用一套電路,如圖3所示。低壓模式下pbias = 0V, nbias = vcco, en1p8_vcco = vcco, en1p8_aux = vcco, en1p8_b_vcco = 0, vis = 1V,如表1所示。低壓模式出于電壓裕度和速度考慮,不再需要鉗位電壓和鉗位電路。低壓模式下可通過圖3右側電路將vout_p和vout_n,p1和n2,p1b和n2b短接以旁路掉中間鉗位電路。

其中inp為low voltage domain (vccint,≤0.925V) level-shift輸入,vout_p為high voltage domain(vcco,≤1.8V)level-shift輸出,初始時刻inp為vccint,vout_p和vout_n為vcco,完成了不同電壓domain高(inp)到高(vout_p)的轉換。inp由高跳低再跳高的轉換過程與之前高壓模式類似,這里不再贅述。

Fig3. 寬輸入level-shift低壓模式(1.2V, 1.5V, 1.8V)電路

3 Voltage-resistantbuffer

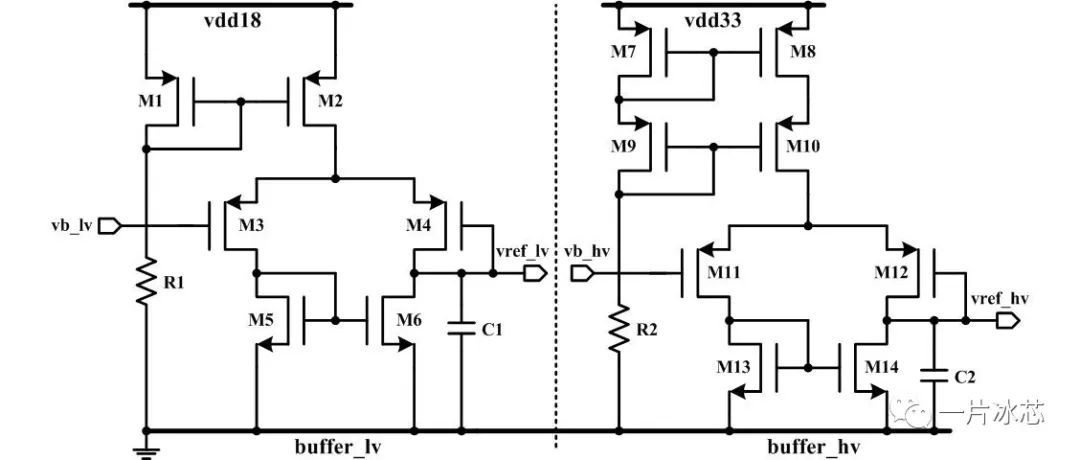

根據第2章分析我們舉一反三,介紹如何實現耐壓結構的buffer,如圖4所示。圖4所有device(電阻除外)任意兩端電壓(bulk除外)在任意工作模式下不得超過1.98V。左側(buffer_lv)電路電源電壓(vdd18)為1.8V,因為沒有耐壓風險,很容易實現。

當左面電路電源電壓(vdd18)提升到3.3V時,所有device均會出現耐壓問題,不加以處理會嚴重影響芯片壽命。我們在左側電路M1,M2漏端插入一組cascode晶體管(如圖4右側M9, M10所示)即可實現耐壓結構的buffer,如圖4右側F。

由此可推廣到更加復雜的電路系統,基本思想就是通過疊管子、鉗位來保護有耐壓風險的晶體管。

Fig4. 低壓和高壓buffer原理圖

**4 **思考與討論

① 專利中的BIAS GENERATION SEGMENT如何實現?整體IO Block又如何實現?一個IO Block又如何同時兼容LVDS、LVCMOS、LVTTL等電平標準?

② 根據以上分析如何舉一反三,設計一款耐壓結構的bandgap、mux等電路?

③ power down時如何不存在耐壓問題?應該加何種電路以輔助實現power down。

④ 當電路規模龐大時,如何check網表中所有device是否存在耐壓問題(正常工作、power down以及上下電過程中都不要有耐壓風險)?

-

電平轉換器

+關注

關注

1文章

173瀏覽量

19548 -

晶體管

+關注

關注

77文章

9635瀏覽量

137854 -

鉗位電壓

+關注

關注

0文章

38瀏覽量

12081 -

IO接口

+關注

關注

0文章

31瀏覽量

13396 -

LVDS電路

+關注

關注

0文章

3瀏覽量

1223

發布評論請先 登錄

相關推薦

寬電壓輸入穩壓電源模塊 E48_UHFCS-3W系列

LTC3588耐壓范圍如何提高?

LT6372-1: Precision Instrumentation Amplifier with Level Shift and Output Clamping Data Sheet

LT6372-0.2: Precision, Funneling Instrumentation Amplifier with Level Shift and Output Clamping Data Sheet

IO模塊中的寬輸入范圍耐壓結構level-shift

IO模塊中的寬輸入范圍耐壓結構level-shift

評論