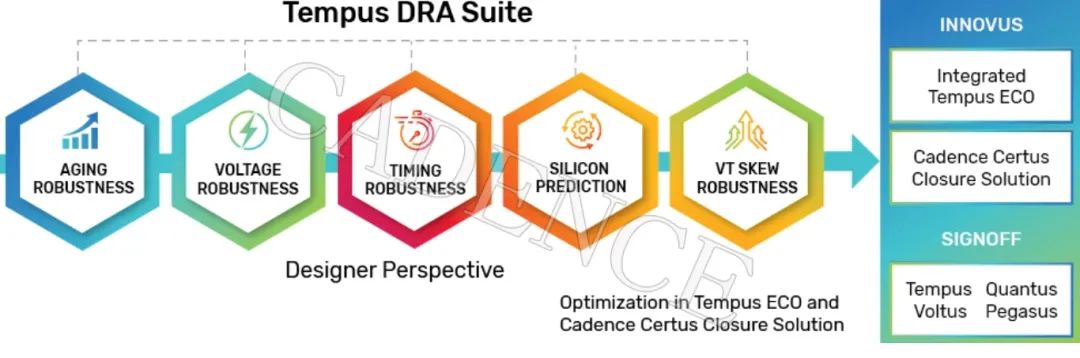

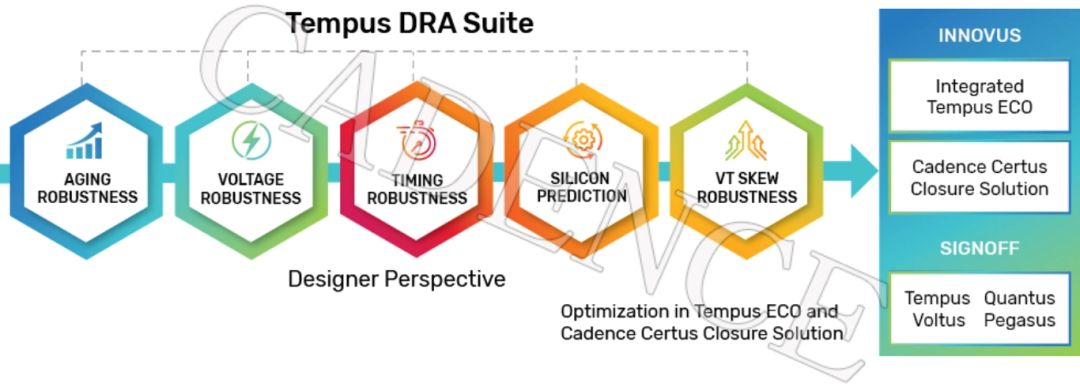

實現簽核時,為了保證芯片設計的耐用性,設計師會面臨重重挑戰,利用 Cadence Tempus 設計穩健性分析(DRA)套件為設計工程師提供領先的建模技術,可實現最佳功耗、性能和面積目標(PPA)。

相較于傳統方法,Tempus DRA 套件提供了一套全面的高級分析功能,有望增強設計級穩健性,實現更優 PPA。

使用 Tempus DRA 套件完成完整分析后,設計工程師可以利用 Cadence Innovus 設計實現系統中的 Tempus ECO 選項進行模塊級的收斂,并使用 Cadence Certus 收斂解決方案進行子系統/全芯片層的簽核收斂,顯著提高設計收斂速度,優化 PPA 目標達成。

如需了解更多信息,請點擊文末“閱讀原文”。

關于 Cadence

Cadence 是電子系統設計領域的關鍵領導者,擁有超過 30 年的計算軟件專業積累。基于公司的智能系統設計戰略,Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計概念成為現實。Cadence 的客戶遍布全球,皆為最具創新能力的企業,他們向超大規模計算、5G 通訊、汽車、移動設備、航空、消費電子、工業和醫療等最具活力的應用市場交付從芯片、電路板到完整系統的卓越電子產品。Cadence 已連續九年名列美國財富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請訪問公司網站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版權所有。在全球范圍保留所有權利。Cadence、Cadence 徽標和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標志均為 Cadence Design Systems, Inc. 的商標或注冊商標。所有其他標識均為其各自所有者的資產。

-

Cadence

+關注

關注

64文章

915瀏覽量

141871

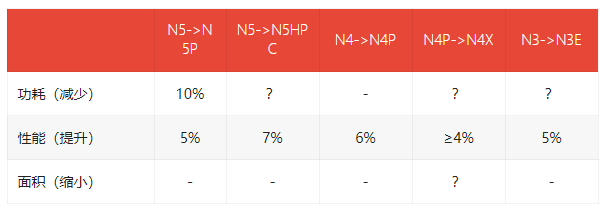

原文標題:Tempus DRA 套件:使用先進的芯片建模實現高達 10% 的 PPA 提升

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DRA74x、DRA75x和DA2x系列設備的服務質量(QoS)旋鈕

知識分享 | 輕松實現優質建模

DRA75x、DRA74x信息娛樂應用處理器器件版本2.0數據表

DRA75xP、DRA74xP信息娛樂應用處理器芯片版本1.0數據表

DRA77xP、DRA76xP信息娛樂應用處理器芯片版本1.0數據表

SK海力士斥資10億美元,加碼先進芯片封裝研發以滿足AI需求

英特爾:未來節點演進版性能提升預計不超過10%

Tempus DRA 套件加速先進節點技術

Tempus DRA 套件:使用先進的芯片建模實現高達 10% 的 PPA 提升

Tempus DRA 套件:使用先進的芯片建模實現高達 10% 的 PPA 提升

評論