晶圓術(shù)語

1.芯片(chip、die)、器件(device)、電路(circuit)、微芯片(microchip)或條碼(bar):所有這些名詞指的是在晶圓表面占大部分面積的微芯片圖形;

- 劃片線(scribe line、saw line)或街區(qū)(street、avenue):這些區(qū)域是在晶圓上用來分隔不同芯片之間的間隔區(qū)。劃片線通常是空白的,但有些公司在間隔區(qū)內(nèi)放置對(duì)準(zhǔn)標(biāo)記,或測(cè)試的結(jié)構(gòu);

- 工程實(shí)驗(yàn)片(engineering die)和測(cè)試芯片(test die):這些芯片與正式芯片或電路芯片不同。它包括特殊的器件和電路模塊用于晶圓生產(chǎn)工藝的電性測(cè)試;

- 邊緣芯片(edge die):在晶圓邊上的一些掩膜殘缺不全的芯片而產(chǎn)生的面積損耗。由于單個(gè)芯片尺寸增大而造成的更多邊緣浪費(fèi)會(huì)由采用更大直徑晶圓所彌補(bǔ)。推動(dòng)半導(dǎo)體工業(yè)向更大直徑晶圓發(fā)展的動(dòng)力之一就是為了減少邊緣芯片所占的面積;

- 晶圓的晶面(wafer crystal plane):圖中的剖面標(biāo)示了器件下面的晶格構(gòu)造,此圖中顯示的器件邊緣與晶格構(gòu)造的方向是確定的;

- 晶圓定位邊(wafer flats)/凹槽(notche):圖示的晶圓由注定位邊(major flat)和副定位邊(minorflat),表示這是一個(gè)P型《100》晶向的晶圓。300mm和450mm直徑的晶圓都是用凹槽作為晶格導(dǎo)向的標(biāo)識(shí)。這些定位邊和凹槽在一些晶圓生產(chǎn)工藝中還輔助晶圓的套準(zhǔn)。

芯片ECO流程

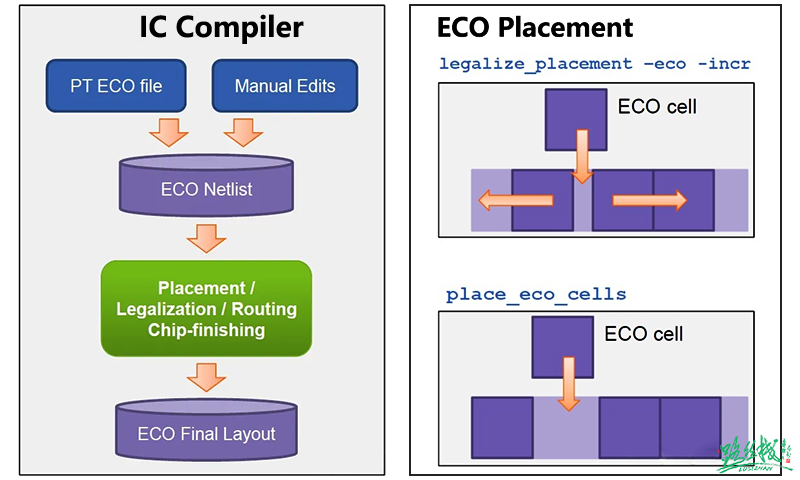

ECO 指的是Engineering Change Order,即工程變更指令。ECO可以發(fā)生在Tapeout之前,過程中,或者之后;Tapeout之后的ECO,改動(dòng)少的可能僅需要改幾層Metal layer,改動(dòng)大可能需要?jiǎng)邮畮讓覯etal layer,甚至重新流片。ECO 的實(shí)現(xiàn)流程如下圖所示:

如果MPW或者FullMask的芯片,驗(yàn)證有功能或者性能缺陷,通過ECO對(duì)電路和標(biāo)準(zhǔn)單元布局進(jìn)行小范圍調(diào)整,保持原設(shè)計(jì)布局布線結(jié)果基本不變的前提下做小規(guī)模優(yōu)化,修復(fù)芯片的剩余違例,最終達(dá)到芯片的簽核標(biāo)準(zhǔn)。不能通過后端布局布線的流程來修復(fù)違例(重新走一遍流程太費(fèi)時(shí)了),而要通過ECO的流程來進(jìn)行時(shí)序、DRC、DRV以及功耗等優(yōu)化。

-

芯片

+關(guān)注

關(guān)注

453文章

50417瀏覽量

421849 -

晶圓

+關(guān)注

關(guān)注

52文章

4844瀏覽量

127803 -

ECO

+關(guān)注

關(guān)注

0文章

52瀏覽量

14867

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶圓術(shù)語 芯片ECO流程

晶圓術(shù)語 芯片ECO流程

評(píng)論