RK3588平臺驅(qū)動調(diào)試篇 [ PCIE篇 ] - PCIE的開發(fā)指南

1、PCIE接口概述

PCIe(Peripheral Component Interconnect Express)是一種用于連接計算機內(nèi)部組件的高速接口標準。以下是關(guān)于PCIe接口的簡要介紹:

高速傳輸: PCIe接口提供了高速的數(shù)據(jù)傳輸通道,可用于連接各種硬件設(shè)備,如圖形卡、存儲設(shè)備、網(wǎng)絡(luò)適配器等。它的速度通常以每秒傳輸?shù)臄?shù)據(jù)位數(shù)(例如PCIe x1、x4、x8、x16等)來表示,每個通道的帶寬可以根據(jù)需要擴展。

點對點連接: PCIe采用點對點連接的架構(gòu),這意味著每個設(shè)備都直接連接到主板上的PCIe插槽,而不需要與其他設(shè)備共享帶寬。這有助于減少延遲并提高性能。

熱插拔支持: PCIe接口支持熱插拔,允許用戶在計算機運行時添加或移除PCIe設(shè)備,而不需要重新啟動計算機。

廣泛應(yīng)用: PCIe接口廣泛用于連接圖形卡、固態(tài)硬盤(SSD)、擴展卡、網(wǎng)絡(luò)適配器和其他高性能設(shè)備。這使得計算機用戶可以根據(jù)需要擴展和升級系統(tǒng)的性能和功能。

PCIe接口是一種計算機硬件連接標準,它提供了高速、高性能的數(shù)據(jù)傳輸通道,支持多種設(shè)備的連接。

2、傳輸速率簡介

PCIe 分類、速度,按lane的個數(shù)分有 x1 x2 x4 x8 x16 (最大可支持32個通道),按代來分 有 gen1 gen2 gen3 gen4

PCIe gen1 和 PCIe gen2 采用的編解碼方式是 8b/10b,PCIe gen3 和 之后的 采用的是 128b/130b 的編碼方式。

8b/10b 意思是說,當我們要傳輸8b的數(shù)據(jù)時,實際在通道上傳輸?shù)氖?0b的數(shù)據(jù),解碼的時候,我們希望得到的是8b的有效數(shù)據(jù)。這樣,相當于有效的帶寬是實際帶寬的 80%。

同理128b/130b,是傳輸128bit數(shù)據(jù)實際線路中傳輸?shù)氖?30bit數(shù)據(jù)。

速率圖中的單位間的關(guān)系:

傳輸速率單位 GT/s,表示 千兆傳輸/秒,是實際每秒傳輸?shù)奈粩?shù),他不包括額外吞吐量的開銷位。

兩個例子:

PCIe gen1 x1 傳輸速率 2.5GT/s = 2500MT/s = ( 2500 / 10 ) MB/s

PCIe gen3 x1 傳輸速率 8GT/s = 8000MT/s = ( 8000 / 130 ) x ( 128/8 ) MB/s= 984.6153... MB/s

PCIe 可?帶寬:吞吐量 = 傳輸速率 * 編碼?案

例如:PCIe 2.0 協(xié)議的每?條 Lane ?持58 / 10 = 4 Gbps = 500 MB/s 的速率,Pcie 2.0 x 8的通道為例,x8的可?帶寬為 48 = 32 Gbps = 4 GB/s。

3、 芯片PCIE資源

3.1 硬件介紹

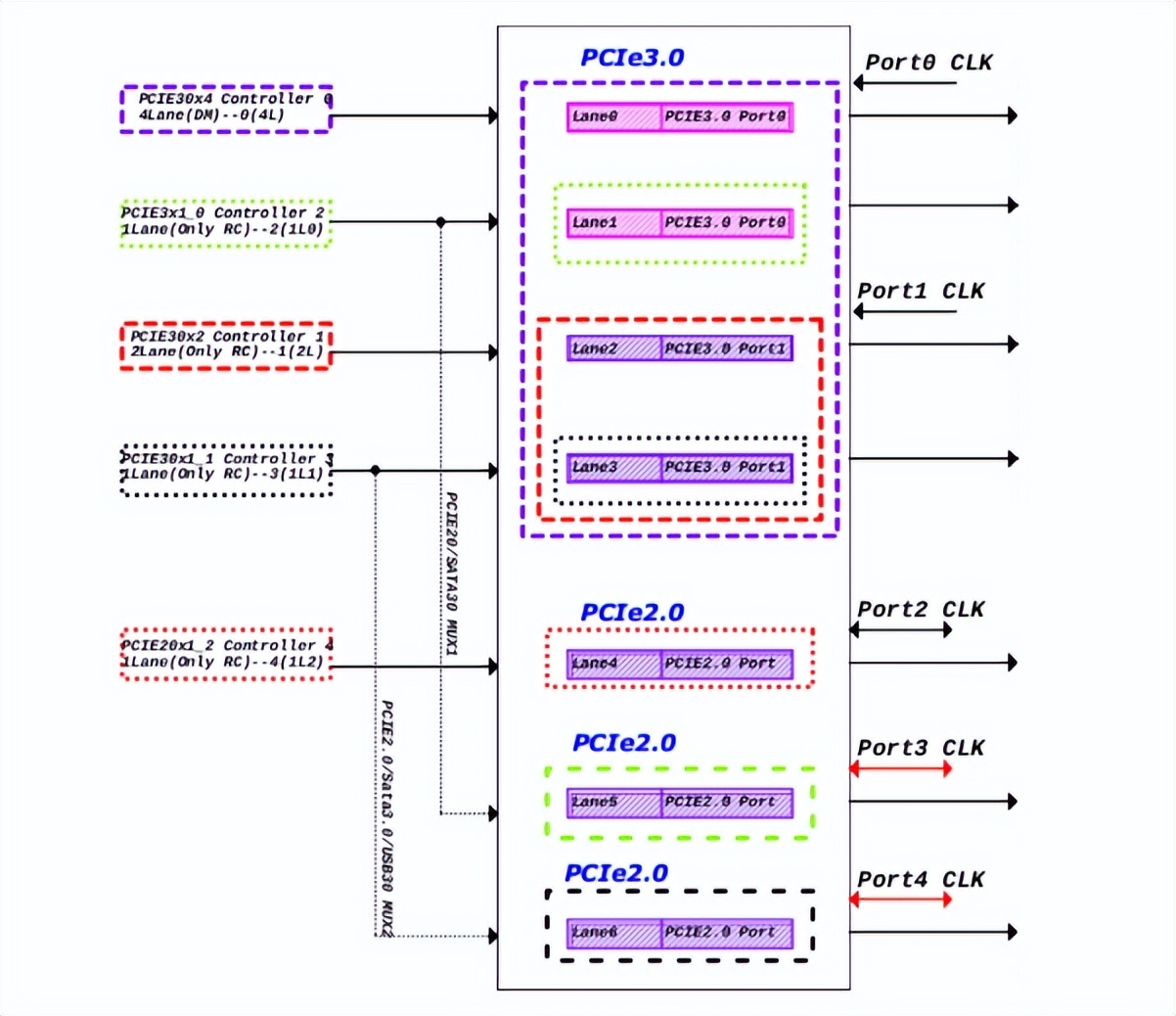

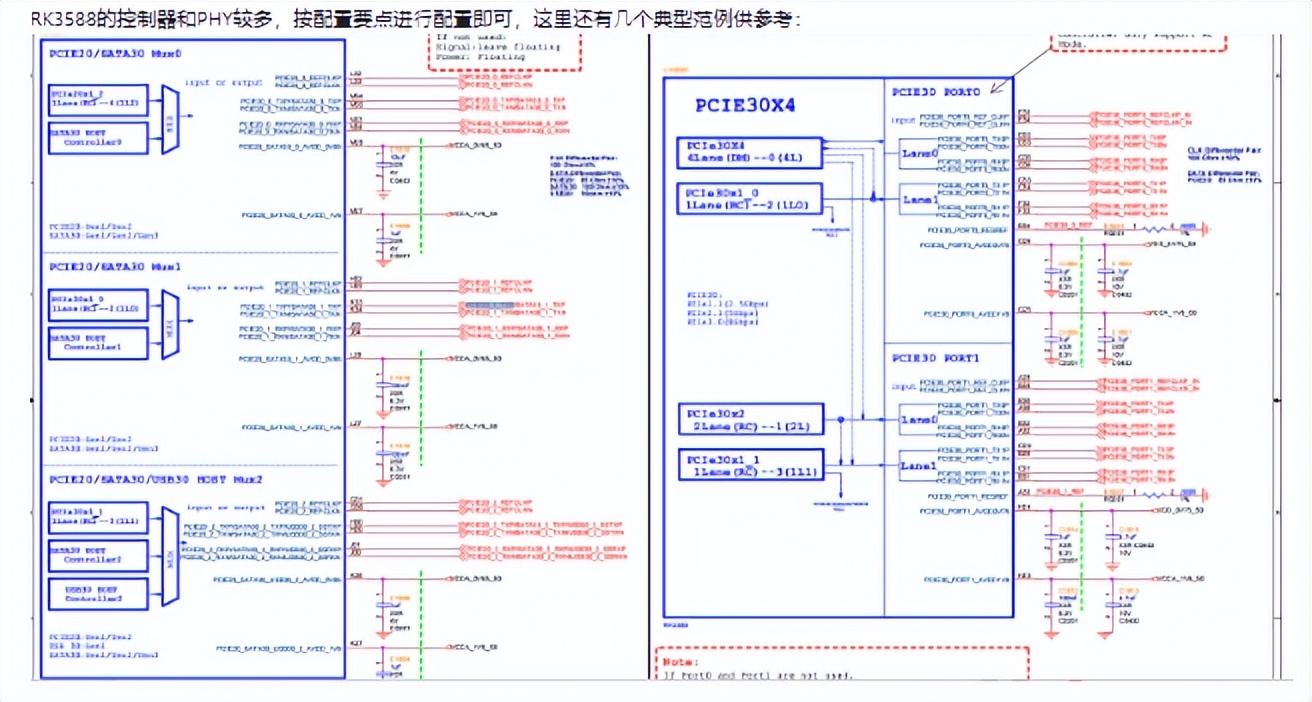

RK3588共有5個PCIe的控制器,硬件IP是?樣的,配置不?樣,其中?個4Lane DM模式可以?持作為EP使?,另外?個2Lane和3個1Lane控制器均只能作為RC使?。RK3588有兩種PCIe PHY,其中?種為pcie3.0PHY,含2個Port共4個Lane,另?種是pcie2.0的PHY有3個,每個都是2.0 1Lane,跟SATA和USB combo使?。pcie3.0 PHY的4Lane可以根據(jù)實際需求拆分使?,拆分后需要合理配置對應(yīng)的控制器。

3.2 kernel dts解析之PCIe

控制器在DTS對應(yīng)節(jié)點名稱:

| 資源 | 模式 | dts節(jié)點 | 可用phy | 內(nèi)部DMA |

|

PCIe Gen3 x 4lane |

RC/EP |

pcie3x4: pcie@fe150000 |

pcie30phy | 是 |

|

PCIe Gen3 x 2lane |

RC only |

pcie3x2: pcie@fe160000 |

pcie30phy | 否 |

|

PCIe Gen3 x 1lane |

RC only |

pcie2x1l0: pcie@fe170000 |

pcie30phy, combphy1_ps |

否 |

|

PCIe Gen3 x 1lane |

RC only |

pcie2x1l1: pcie@fe180000 |

pcie30phy, combphy2_psu |

否 |

|

PCIe Gen3 x 1lane |

RC only |

pcie2x1l2: pcie@fe190000 |

combphy0_ps | 否 |

在kernel/arch/arm64/boot/dts/rockchip/rk3588.dtsi下有具體描述

使用限制

pcie30phy拆分后,pcie30x4控制器,?作于2Lane模式時只能固定配合pcie30phy的port0,?作于 1Lane模式時,只能固定配合pcie30phy的port0lane0;

pcie30phy拆分后,pcie30x2控制器,?作于2Lane模式時只能固定配合pcie30phy的port1,?作于 1Lane模式時,只能固定配合pcie30phy的port1lane0;

pcie30phy拆分為4個1Lane,pcie3phy的port0lane1只能固定配合pcie2x1l0控制器,pcie3phy的 port1lane1只能固定配合pcie2x1l1控制器;

pcie30x4控制器?作于EP模式,可以使?4Lane模式,或者2Lane模式使?pcie30phy的port0, pcie30phy的port1中2lane可以作為RC配合其他控制器使?。默認使?common clock作為reference clock時,?法實現(xiàn)pcie30phy port0的lane0?作于EP模式,lane1?作于RC模式配合其他控制器使 ?,因為Port0的兩個lane是共??個輸?的reference clock,RC和EP同時使?clock可能會有沖突。

RK3588 pcie30phy 如果只使?其中?個port,另?個port也需要供電,refclk等其他信號可接地。

4、PCIe 使用配置

4.1 簡介

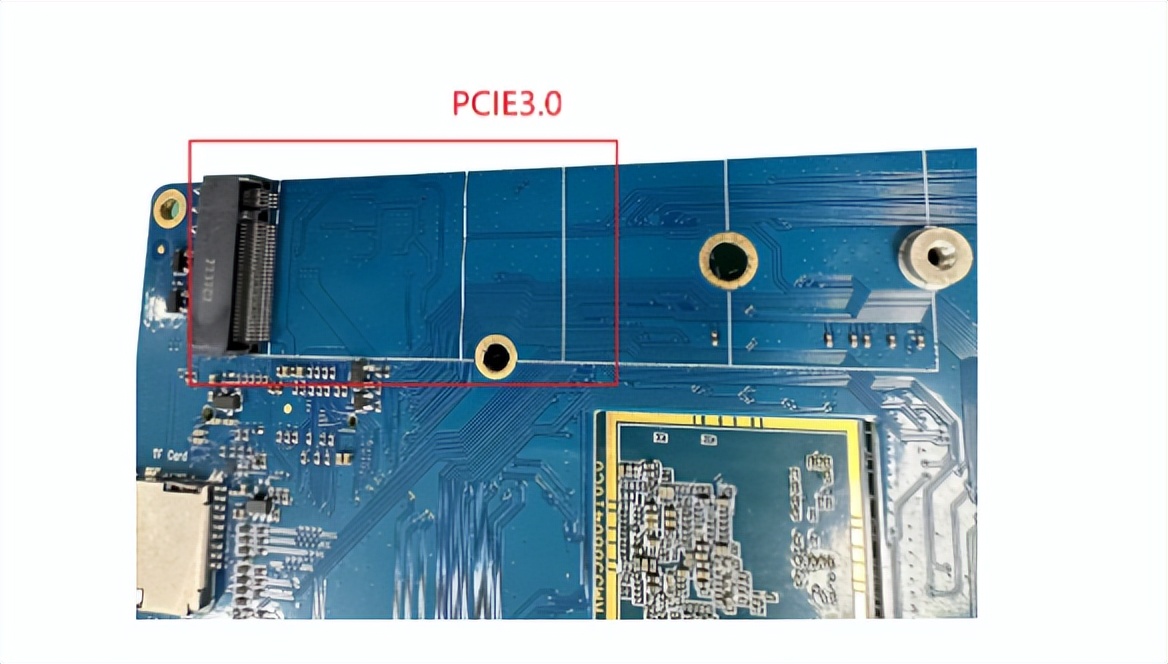

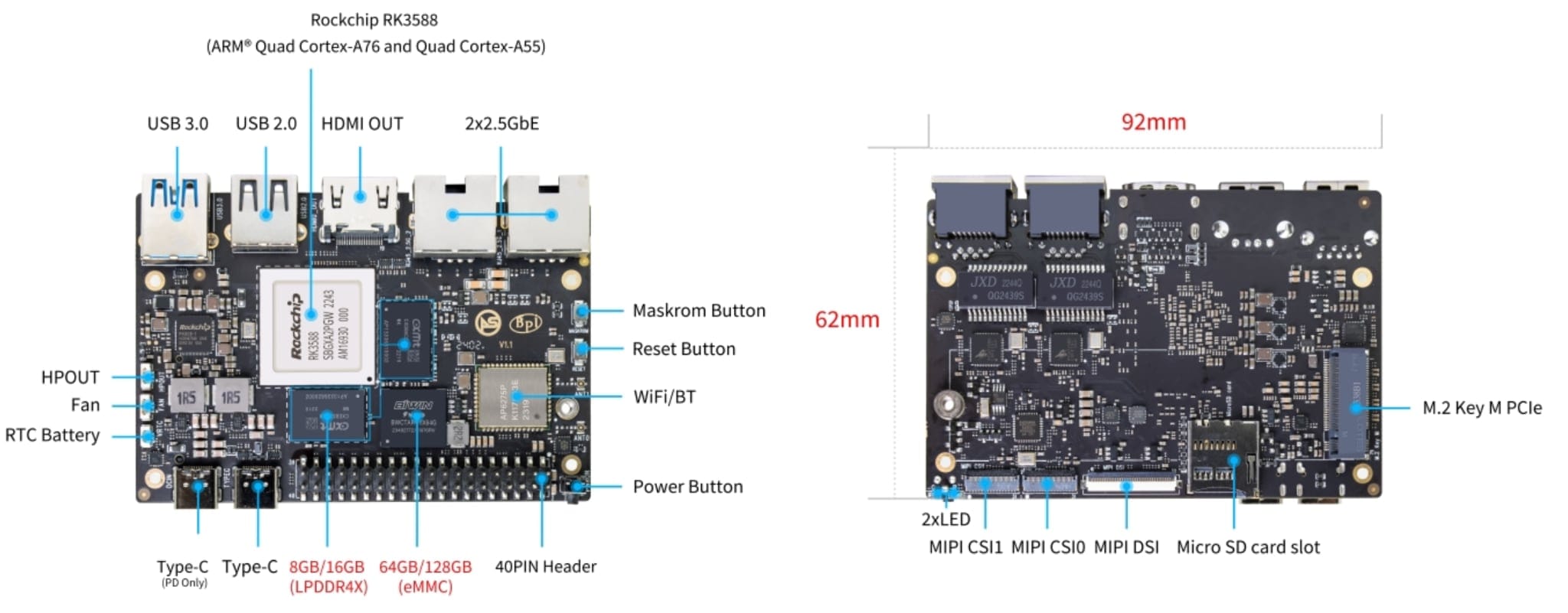

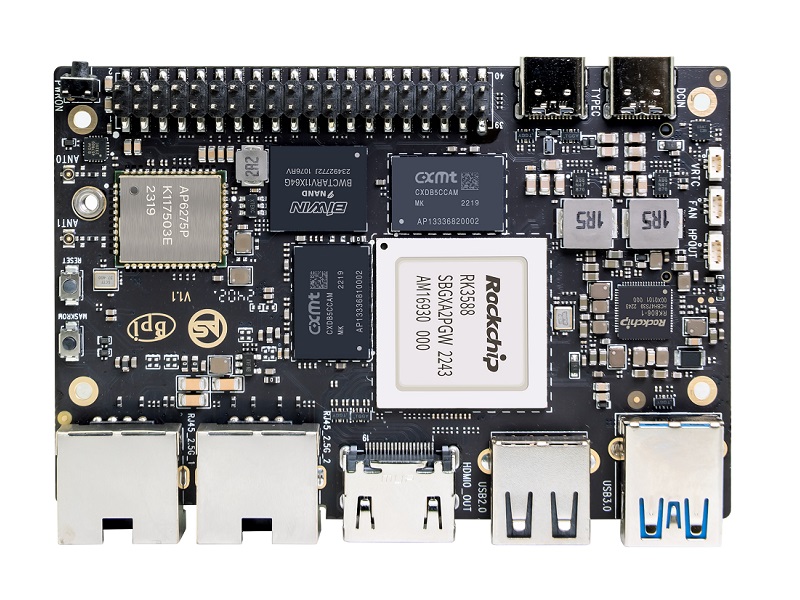

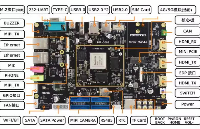

Armsom-W3開發(fā)板上有 1 個 PCIe3.0 x 4 接口和一個PCIe2.0接口,如圖

可以插入對應(yīng)模組使用, 如圖:

4.2 硬件設(shè)計

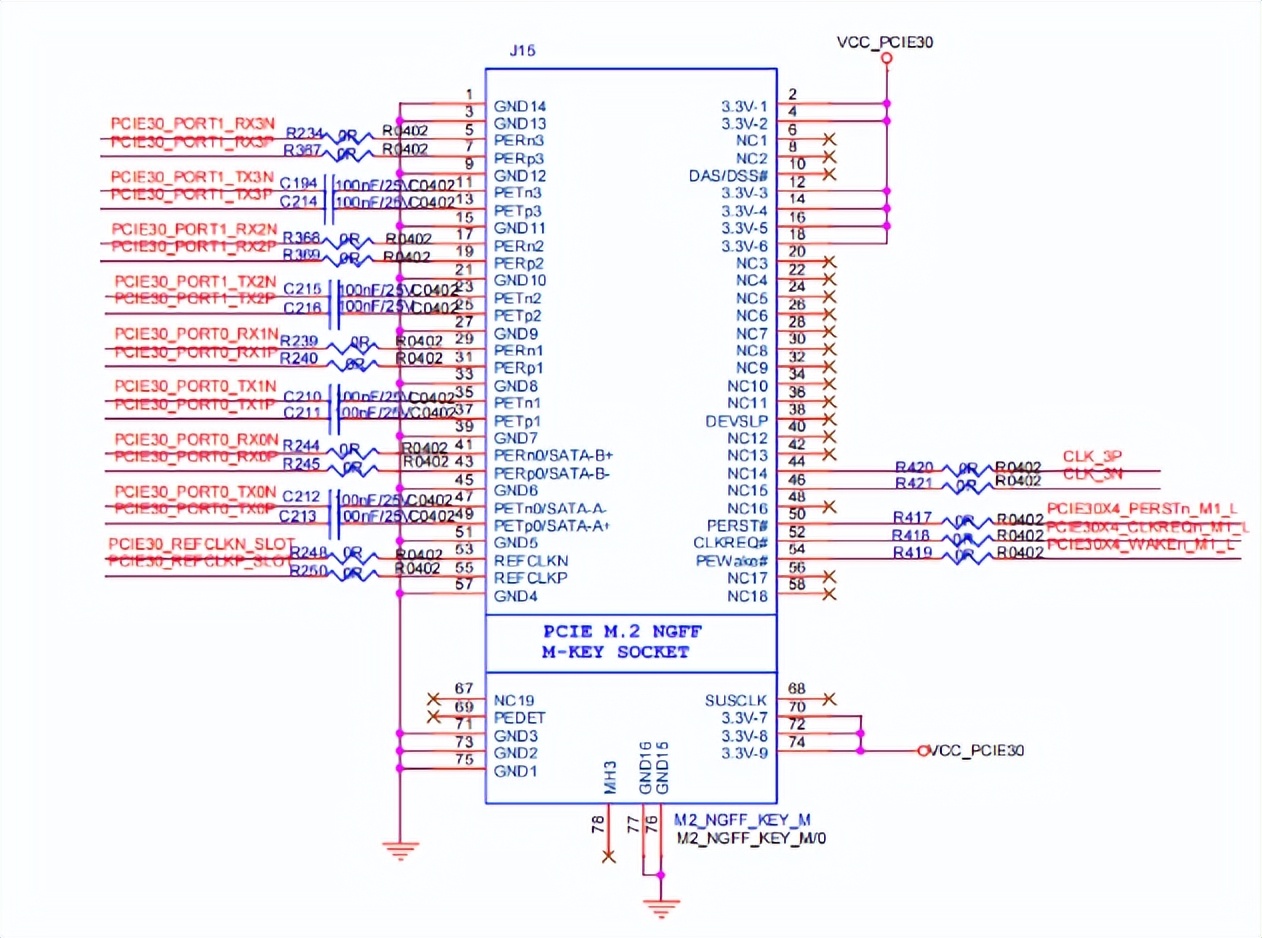

PCIe3.0 x 4 接口:

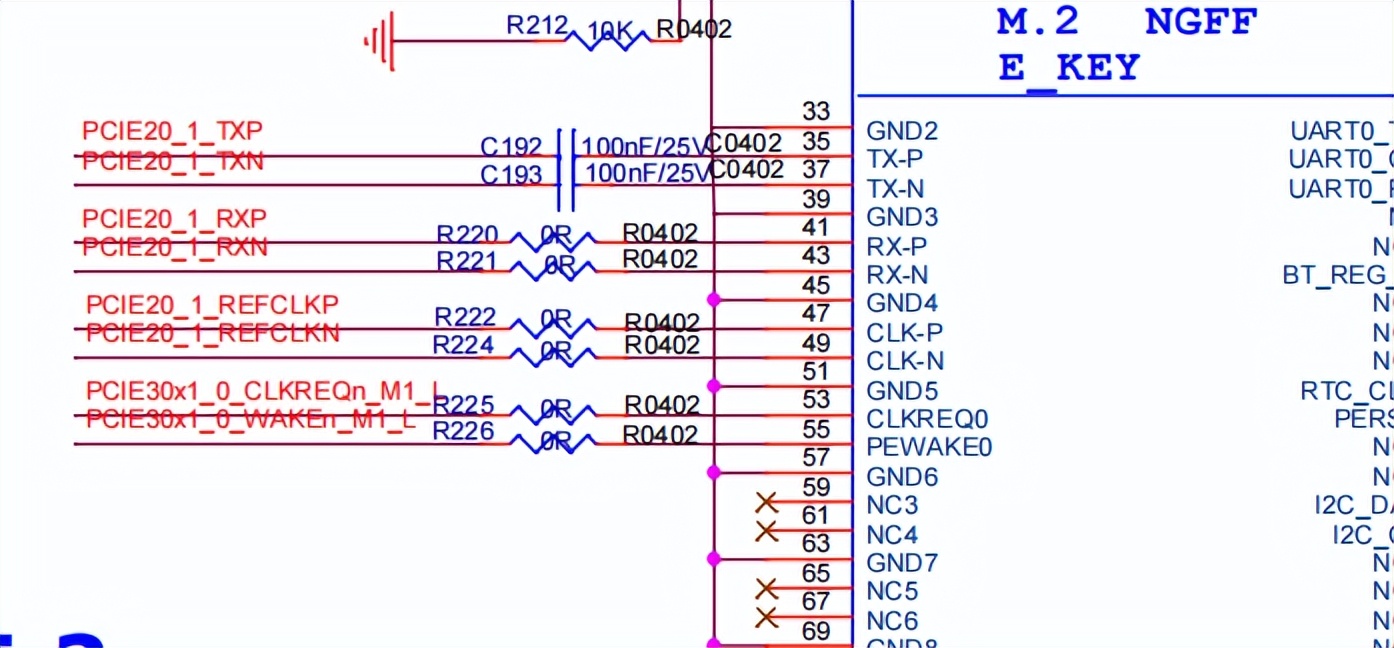

PCIe 2.0接口:

4.3 軟件配置

一般根據(jù)原理圖在 DTS 中配置供電引腳、復位引腳,選擇正確的 pcie 控制器節(jié)點和 PHY 節(jié)點使能就可以。

在kernel/arch/arm64/boot/dts/rockchip/rk3588-armsom-w3.dts中配置如下:

/ {

vcc12v_dcin: vcc12v-dcin {

compatible = "regulator-fixed";

regulator-name = "vcc12v_dcin";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = ;

regulator-max-microvolt = ;

};

vcc5v0_sys: vcc5v0-sys {

compatible = "regulator-fixed";

regulator-name = "vcc5v0_sys";

regulator-always-on;

regulator-boot-on;

regulator-min-microvolt = ;

regulator-max-microvolt = ;

vin-supply = ;

};

vcc3v3_pcie2x1l0: vcc3v3-pcie2x1l0 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie2x1l0";

regulator-min-microvolt = ;

regulator-max-microvolt = ;

enable-active-high;

regulator-boot-on;

regulator-always-on;

gpios = ;

startup-delay-us = ;

vin-supply = ;

};

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = ;

regulator-max-microvolt = ;

enable-active-high;

gpios = ;

startup-delay-us = ;

vin-supply = ;

};

}

&pcie2x1l0 {

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&combphy1_ps {

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = ;

status = "okay";

};

&pcie3x4 {

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

pcie30phy、combphy1_ps:PHY 節(jié)點

pcie3x4、pcie2x1l0:pcie3x4 控制器節(jié)點

reset-gpios:復位引腳屬性

vcc3v3_pcie2x1l0、vcc3v3_pcie30:供電引腳節(jié)點

4.4 其他PCIE配置的實例

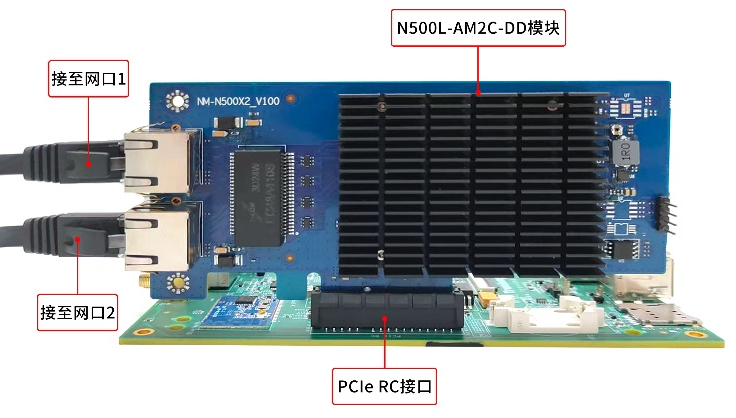

RK3588的控制器和PHY較多,按配置要點進?配置即可,這?還有?個典型范例供參考:

4.4.1 ?例1 pcie3.0phy拆分2個2Lane RC, 3個PCIe 2.0 1Lane

/ {

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = ;

regulator-max-microvolt = ;

enable-active-high;

gpios = ;

startup-delay-us = ;

vin-supply = ;

};

};

&combphy0_ps {

status = "okay";

};

&combphy1_ps {

status = "okay";

};

&combphy2_psu {

status = "okay";

};

&pcie2x1l0 {

phys = ;

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie2x1l1 {

phys = ;

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie2x1l2 {

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie30phy {

/*pcie30phy的組合使?模式:

PHY_MODE_PCIE_NANBNB /* P1:PCIe3x2 + P0:PCIe3x2 */

PHY_MODE_PCIE_NANBBI /* P1:PCIe3x2 + P0:PCIe3x1*2 */

PHY_MODE_PCIE_NABINB /* P1:PCIe3x1*2 + P0:PCIe3x2 */

PHY_MODE_PCIE_NABIBI /* P1:PCIe3x1*2 + P0:PCIe3x1*2 */

*/

rockchip,pcie30-phymode = ;

status = "okay";

};

&pcie3x2 {

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie3x4 {

num-lanes = ;//拆分為2lan使用

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

4.4.2 ?例2 pcie3.0phy拆分為4個1Lane, 1個使?PCIe 2.0 1 Lane

/ {

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = ;

regulator-max-microvolt = ;

enable-active-high;

gpios = ;

startup-delay-us = ;

vin-supply = ;

};

};

&combphy0_ps {

status = "okay";

};

&pcie2x1l0 {

phys = ;

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie2x1l1 {

phys = ;

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie2x1l2 {

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = ;

status = "okay";

};

&pcie3x2 {

num-lanes = ;

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

&pcie3x4 {

num-lanes = ;

reset-gpios = ;

vpcie3v3-supply = ;

status = "okay";

};

pcie30phy拆分為4個1Lane時,port0lane0固定配合pcie3x4控制器,pcie3phy的port0lane1固定配合pcie2x1l0控制器,port1lane0固定配合pcie3x2控制器,pcie3phy的port1lane1固定配合pcie2x1l1控制器,加上combphy0_ps固定配合pcie2x1l2。

審核編輯 黃宇

-

PCIe

+關(guān)注

關(guān)注

15文章

1217瀏覽量

82445 -

開源

+關(guān)注

關(guān)注

3文章

3251瀏覽量

42406 -

banana pi

+關(guān)注

關(guān)注

1文章

108瀏覽量

2970

發(fā)布評論請先 登錄

相關(guān)推薦

RK3588 SDK入門之編譯使用篇

國產(chǎn)最強SOC—RK3588之虛擬機搭建篇

用戶手冊 | 國產(chǎn)最強SOC——RK3588之鏡像升級篇

Banana Pi BPI-R3路由器開發(fā)板運行 OrayOS物聯(lián)網(wǎng)系統(tǒng)

用戶手冊 | 國產(chǎn)最強SOC——RK3588之調(diào)試登錄篇

迅為瑞芯微RK3588開發(fā)板深度剖析丨首選的性能

迅為RK3588開發(fā)板深度剖析丨首選的性能

探索巔峰性能 |迅為 RK3588開發(fā)板深度剖析

Banana Pi BPI-M7 RK3588開源硬件開發(fā)板評測試

Banana Pi BPI-M7 RK3588開發(fā)板運行RKLLM軟件堆AI大模型部署

實測952Mbps!四路千兆網(wǎng)PCIe拓展方案,國產(chǎn)工業(yè)級!

2024挑戰(zhàn)性價比最高的RK3588s開發(fā)板-youyeetoo R1評測

Banana Pi BPI-W3 RK3588平臺驅(qū)動調(diào)試篇 [ PCIE篇一 ] - PCIE的開發(fā)指南

Banana Pi BPI-W3 RK3588平臺驅(qū)動調(diào)試篇 [ PCIE篇一 ] - PCIE的開發(fā)指南

評論