首先,考慮x和z在verilog條件語句中的使用情況,然后我們再考慮在verilog中用x和z給其他reg/wire賦值的情況。

(一)首先,考慮x和z在verilog條件語句中的使用情況。

Verilogcase語句中,2'b1x和2’b0x造成的仿真器、綜合器的mismatch,

舉個例子:

match2'b1xto11or10

match2’b0xto01or00

HDLCompilertool

both2'b1xand2’b0xareevaluatedtofalse. Becauseofthesimulationandsynthesismismatches,theHDLCompilertoolissuesanELAB-310warning.

case(A) 2'b1x:...//Youwant2'b1xtomatch11and10but //HDLCompileralwaysevaluatesthiscomparisontofalse 2'b0x:...//youwant2'b0xtomatch00and01but //HDLCompileralwaysevaluatesthiscomparisontofalse default:... endcase

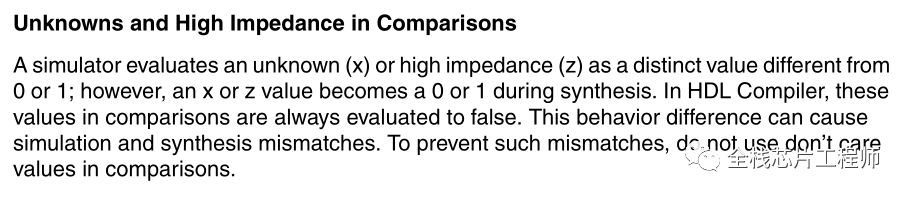

官方說明:我們可以得到兩點信息:

第一點:

Asimulatorevaluatesanunknown(x)orhighimpedance(z)asadistinctvaluedifferentfrom0or1;however,anxorzvaluebecomesa0or1duringsynthesis.

第二點:

DC工具會直接將verilog比較判斷語句中的xorz直接理解為false。所以禁止在verilog比較判斷語句中使用xorz。

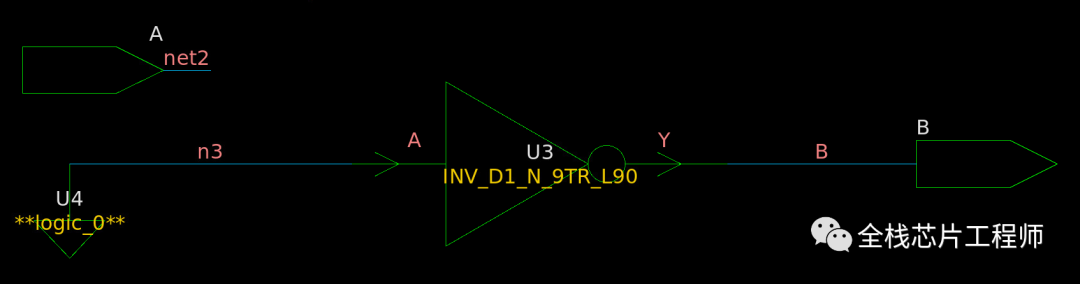

參見如下代碼,DC工具會理解if(A==1'bx)為false,因此DC會直接assigns1toregB并且報ELAB-310warning.

moduletest( inputA, outputregB ); always@(*)begin if(A==1'bx) B=0; else B=1; end endmodule

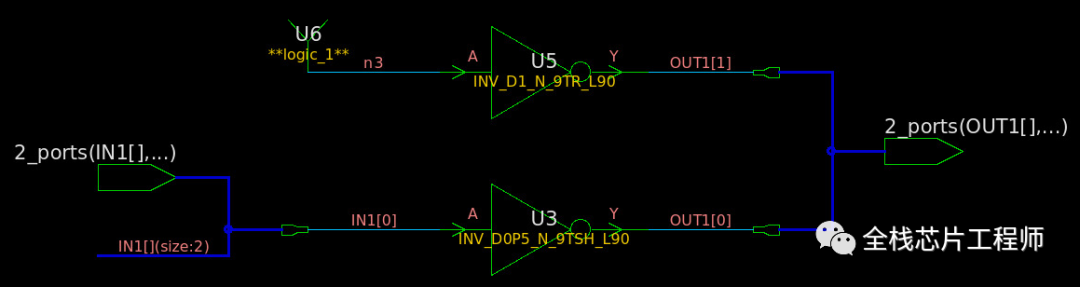

實際綜合如下,果不其然,有意思哇!后面幾個稍微復雜點的代碼更有趣!

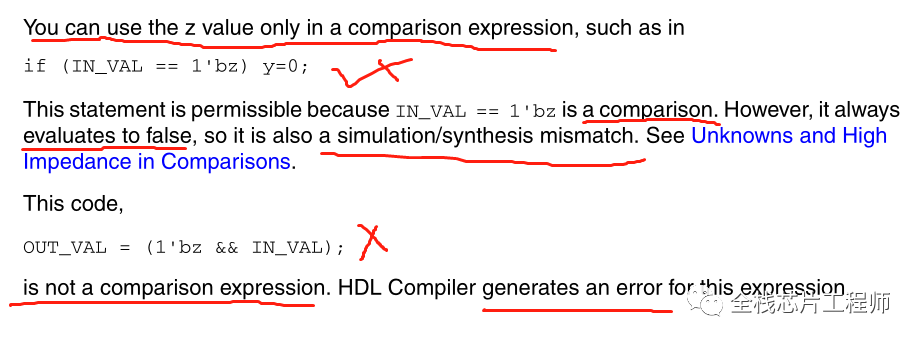

再補充z的使用:

結論:仿真工具可以理解x、z、0、1狀態,但是綜合工具遇到帶x、z的比較判斷條件時,直接理解該條件為false。

(二)然后我們再考慮在verilog中用x和z給其他reg/wire賦值的情況。

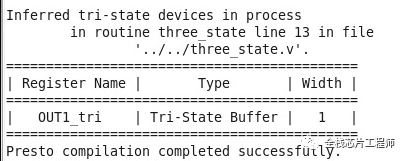

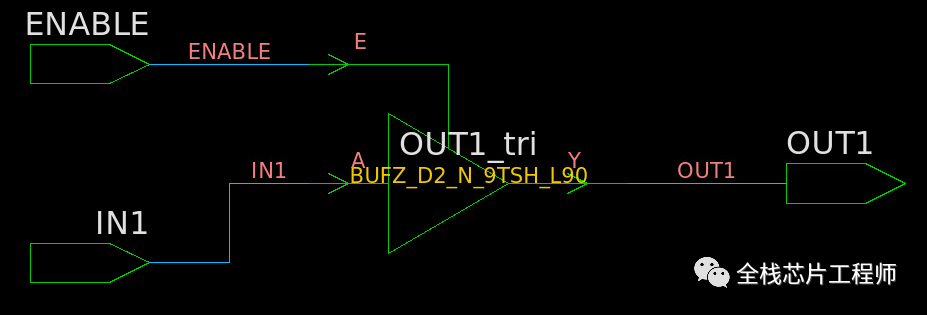

案例1:z賦值是沒問題的,會綜合出來三態門,參見如下代碼1:

modulethree_state(ENABLE,IN1,OUT1); inputIN1,ENABLE; outputregOUT1; always@(ENABLEorIN1)begin if(ENABLE) OUT1=IN1; else OUT1=1'bz;//assignshigh-impedancestate end endmodule

Logicalbufferofasingleinputwithanactive-highoutputenable.Theoutputis3-statedwhentheenableislow.

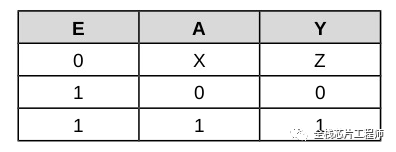

真值表:

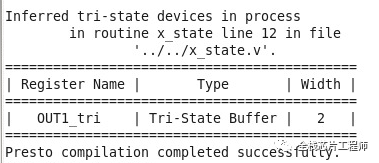

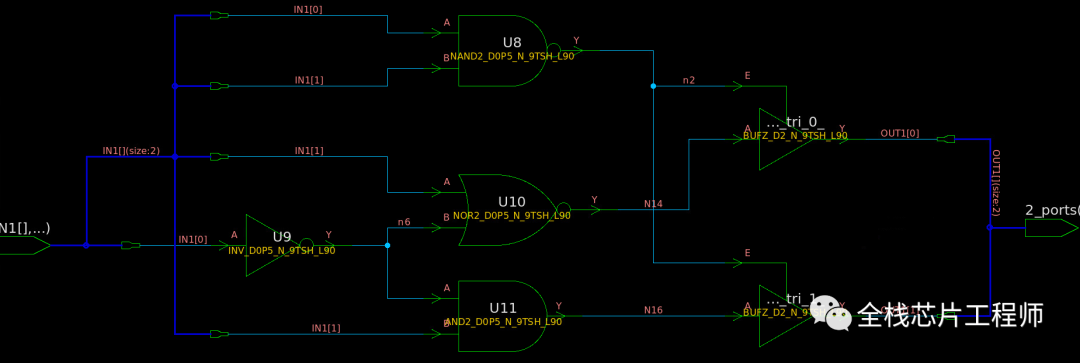

案例2:z賦值是沒問題的,會綜合出來三態門,參見如下代碼2:

modulex_state(IN1,OUT1); input[1:0]IN1; outputreg[1:0]OUT1; always@(*)begin case(IN1) 2'b00:OUT1=2'b00; 2'b01:OUT1=2'b01; 2'b10:OUT1=2'b10; default:OUT1=2'bzz;//assignshigh-impedancestate endcase end endmodule

再看X賦值是什么情況。

案例1:利用DC綜合工具實測如下代碼綜合效果:

modulex_state(IN1,OUT1); input[1:0]IN1; outputreg[1:0]OUT1; always@(*)begin case(IN1) 2'b00:OUT1=2'b01; 2'b11:OUT1=2'b00; default:OUT1=2'bxx; endcase end endmodule

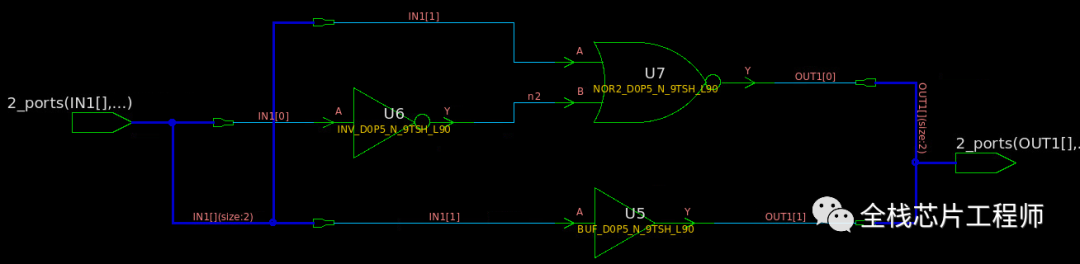

可見,x賦值直接被DC工具省略,也沒有latch出現。

案例2:

modulex_state(IN1,OUT1); input[1:0]IN1; outputreg[1:0]OUT1; always@(*)begin case(IN1) 2'b00:OUT1=2'b00; 2'b01:OUT1=2'b01; 2'b10:OUT1=2'b10; default:OUT1=2'bxx;//assignshigh-impedancestate endcase end endmodule

可見,x賦值直接被DC工具省略,也沒有latch出現。

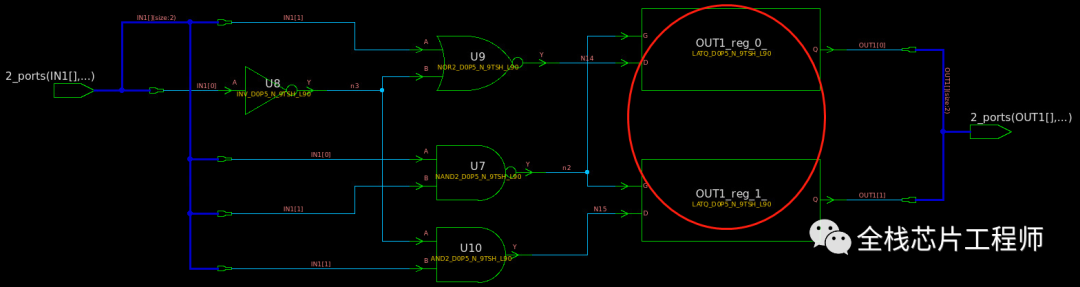

案例3:注釋掉default,非full_case,必然出現latch!

modulex_state(IN1,OUT1); input[1:0]IN1; outputreg[1:0]OUT1; always@(*)begin case(IN1) 2'b00:OUT1=2'b00; 2'b01:OUT1=2'b01; 2'b10:OUT1=2'b10; endcase end endmodule

因此,盡管x賦值直接被DC工具省略,也沒有latch出現,但是仍然建議不要使用x賦值,除非full_case情況下,不會執行default條件下的x賦值分支,寫x賦值可以用于仿真查看波形,如下代碼所示:

always@(*)begin case(pmu_state) //Duringpowerdownsequence,shiftingpatterntoactive //ISOLATE->RETAIN->PWRDOWN //andstayunchangeduringpowereddownstate `ARM_POWERING_DOWN,`ARM_POWERED_DOWN:begin nxt_isolate_n=1'b0; nxt_retain_n=ISOLATEn; nxt_pwrdown=~RETAINn; end //Duringpowerupsequence,shiftingpatterntoactive //PWRDOWN->RETAIN->ISOLATE `ARM_POWERING_UP,`ARM_POWERED_UP:begin nxt_pwrdown=1'b0; nxt_retain_n=~PWRDOWN; nxt_isolate_n=RETAINn; end //PropagateX default:begin nxt_isolate_n=1'bX; nxt_retain_n=1'bX; nxt_pwrdown=1'bX; end endcase end

審核編輯:湯梓紅

-

仿真器

+關注

關注

14文章

1016瀏覽量

83632 -

Verilog

+關注

關注

28文章

1343瀏覽量

109980 -

HDL

+關注

關注

8文章

327瀏覽量

47336 -

代碼

+關注

關注

30文章

4744瀏覽量

68345 -

綜合器

+關注

關注

0文章

9瀏覽量

6440

原文標題:Verilog中,2'b1x和2’b0x造成的仿真器、綜合器的mismatch?!

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CUBEIDE運行完可以看RAM的使用情況,運行中可以實時查看RAM的使用情況嗎?

如何查看RAM使用情況?

電池使用情況統計信息

如何檢查imx6中的GPU使用情況?

SoC如何查看內存使用情況

python if語句多個條件怎么用

TMS320C64x在高性能DSP應用中的高速緩存使用情況

考慮x和z在verilog條件語句中的使用情況

考慮x和z在verilog條件語句中的使用情況

評論