組合電路在 HLS 中的重要性

該項(xiàng)目通過一個(gè)示例演示了 HLS 中組合電路對(duì)設(shè)計(jì)的影響。

在 HLS 中描述組合任務(wù)非常重要,因?yàn)樗苯佑绊懻麄€(gè)系統(tǒng)的性能。這里我舉一個(gè)簡(jiǎn)單的例子來解釋一下這個(gè)問題。

介紹

高級(jí)綜合工具將算法轉(zhuǎn)換為等效的 RTL 描述。該描述代表邏輯電路,可以通過ASIC或FPGA技術(shù)來綜合。

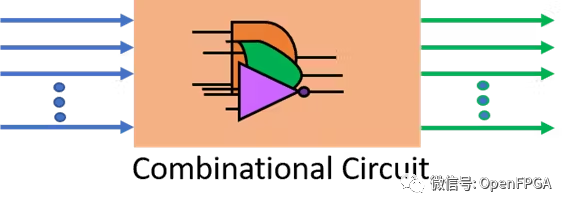

邏輯電路可以是以下兩種類型之一:組合電路或時(shí)序電路。組合電路的輸出僅是其輸入上的當(dāng)前邏輯值的函數(shù)。如圖1所示,只需使用基本邏輯門即可實(shí)現(xiàn)組合電路,不需要存儲(chǔ)單元。

圖1

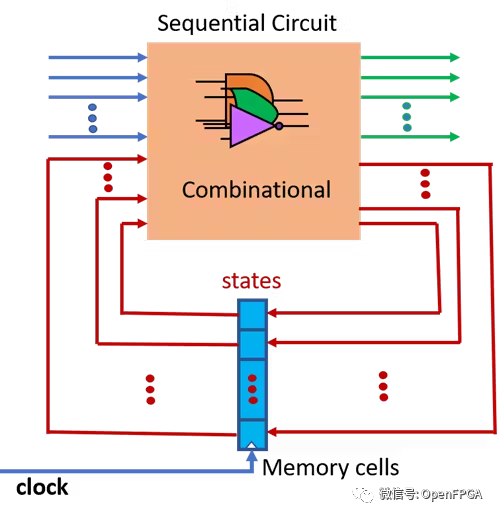

另一方面,時(shí)序電路的輸出不僅取決于其輸入的當(dāng)前值,還取決于過去時(shí)間的輸入值的歷史記錄。

電路狀態(tài)通常模擬輸入值歷史的影響。一組存儲(chǔ)單元可以代表這些狀態(tài)。

圖2

圖2顯示了由組合電路和一組保存電路狀態(tài)的存儲(chǔ)單元組成的時(shí)序電路的結(jié)構(gòu)。存儲(chǔ)器單元可以是觸發(fā)器、BRAM或DDR存儲(chǔ)器的形式。

組合部分接收兩組數(shù)據(jù):主輸入和狀態(tài)。然后它生成兩組輸出:主要輸出和下一個(gè)狀態(tài)。系統(tǒng)中的其他模塊使用主輸出,而下一個(gè)狀態(tài)數(shù)據(jù)修改存儲(chǔ)單元并定義新的電路狀態(tài)。

動(dòng)機(jī)

所有組合電路都需要一個(gè)時(shí)間間隔,以便在其輸入發(fā)生任何變化后產(chǎn)生穩(wěn)定的輸出。這個(gè)時(shí)間被稱為傳播延遲。組合電路中從輸入到輸出的不同路徑可能具有各種延遲。最長(zhǎng)路徑也稱為關(guān)鍵路徑,被定義為設(shè)計(jì)傳播延遲。

在時(shí)序電路中,時(shí)鐘周期對(duì)設(shè)計(jì)性能有直接影響。圖 2 中組合部分的傳播延遲決定了最小時(shí)鐘周期。因此,它的好壞直接影響到整個(gè)系統(tǒng)的性能。

時(shí)序電路通常需要幾個(gè)時(shí)鐘周期來完成其相關(guān)任務(wù)。所需時(shí)鐘周期的最大數(shù)量稱為設(shè)計(jì)延遲。組合部分也對(duì)相關(guān)時(shí)序電路的延遲有直接影響。

因此,了解如何在 HLS 中設(shè)計(jì)高效的組合電路是在硬件上開發(fā)高性能算法的第一步。

組合電路的影響

在這里,將通過一個(gè)例子來解釋正確的 C/C++ 描述組合設(shè)計(jì)如何能夠加快實(shí)現(xiàn)速度。

假設(shè)我們要在如圖 3 所示的 Basys3 FPGA 評(píng)估板上可用的四個(gè)七段上顯示數(shù)字的四位十進(jìn)制數(shù)字。

圖3

第一步是提取四位十進(jìn)制數(shù)字,然后找到每個(gè)數(shù)字對(duì)應(yīng)的七段代碼,并將代碼發(fā)送到板上的段選擇上。這里我只解釋第一個(gè)任務(wù),即提取四位小數(shù)。

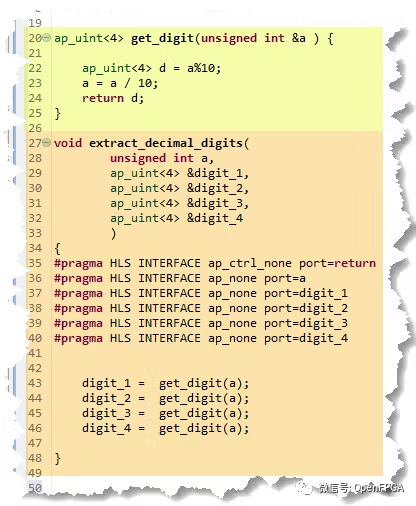

讓我們考慮以下 Vivado-HLS 代碼,該代碼提取 4 位無符號(hào)整數(shù)的十進(jìn)制數(shù)字。設(shè)計(jì)頂部函數(shù)是extract_decimal_digits ,它接受輸入參數(shù)(即a )并生成四個(gè)輸出(即 digital_1、digit_2、digit_3、digit_4)。它調(diào)用函數(shù)get_digit四次來提取每個(gè)數(shù)字。get_digit函數(shù)提取接收到的號(hào)碼的第一位數(shù)字,然后對(duì)其進(jìn)行修改。

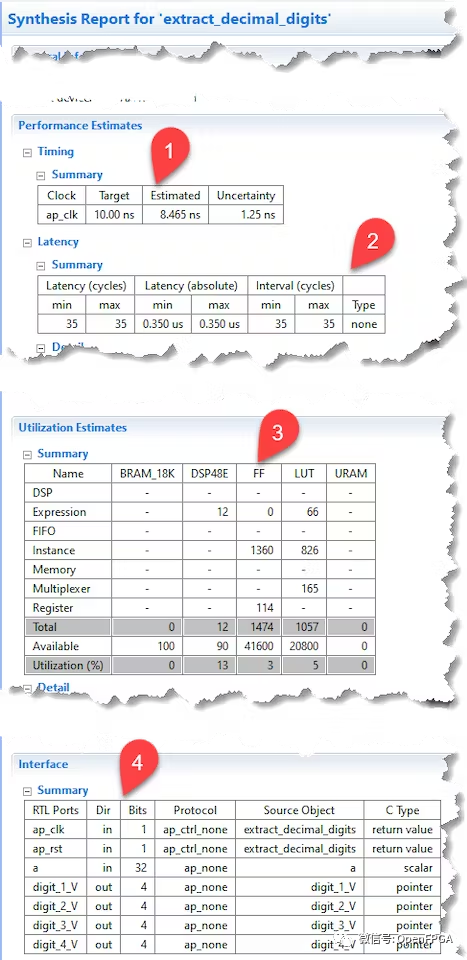

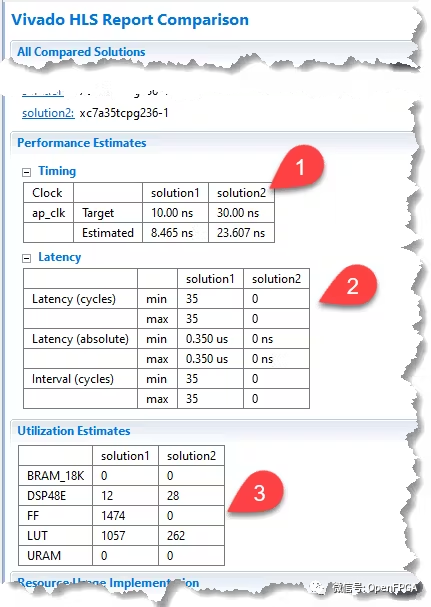

如果我們執(zhí)行高級(jí)綜合過程來生成等效的 RTL 設(shè)計(jì),則圖 5 顯示了 Basys3 板的報(bào)告。Vivado-HLS 綜合過程利用參數(shù)化的 Xilinx LogiCORE 除法器內(nèi)核來實(shí)現(xiàn)模運(yùn)算。該代碼具有流水線結(jié)構(gòu)。

可以看出,設(shè)計(jì)時(shí)鐘周期約束為10 ns(用1注釋)。流水線設(shè)計(jì)需要 35 個(gè)周期來完成其任務(wù),即 0.35 us(用 2 表示)。此外,它還使用了 12 個(gè) DSP、1474 個(gè) FF 和 1057 個(gè) LUT。

圖5

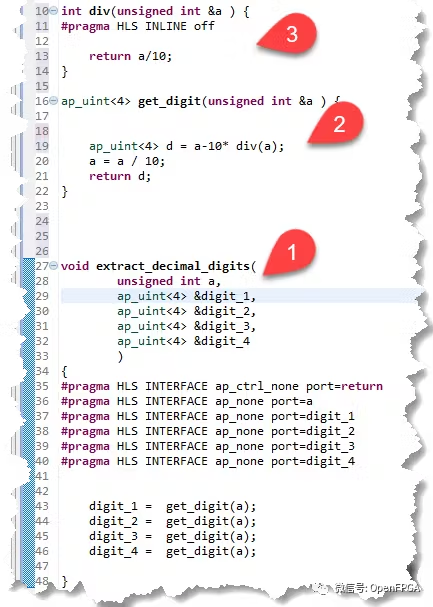

現(xiàn)在讓我們考慮以下實(shí)現(xiàn),將模運(yùn)算替換為其等效的算術(shù)表達(dá)式,即 a%10 = a – 10*(a/10)。如果我們直接使用這個(gè)表達(dá)式,編譯器會(huì)優(yōu)化代碼,再次使用模運(yùn)算,并生成相同的 RTL 描述。為了阻止編譯器優(yōu)化代碼,我使用了一個(gè)單獨(dú)的子函數(shù)來執(zhí)行除 10 運(yùn)算符。另外,還關(guān)閉了編譯器函數(shù)內(nèi)聯(lián)功能。

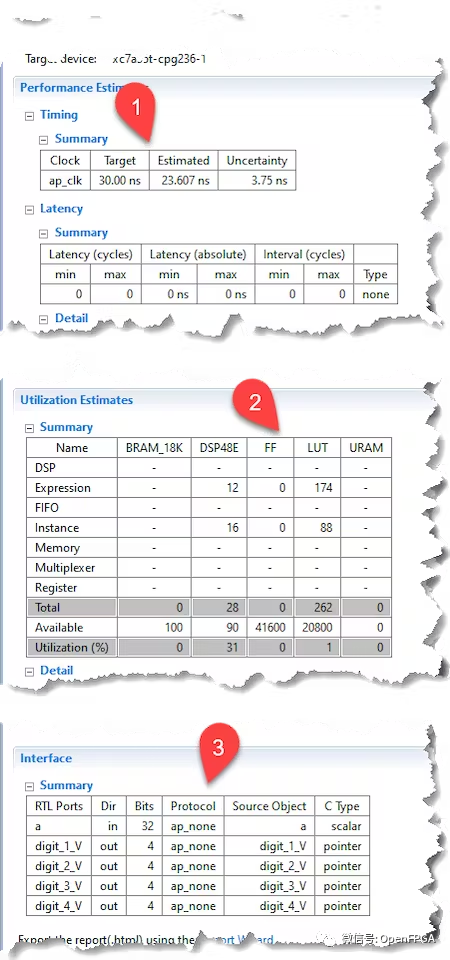

現(xiàn)在,如果我們綜合此代碼,圖 7 將顯示相應(yīng)的報(bào)告。

該電路完全由組合電路搭建。電路傳播延遲為23.607 ns,使用28個(gè)DSP和262個(gè)LUT。

圖7

比較這兩種實(shí)現(xiàn)方式:圖 8 顯示了比較結(jié)果。在該圖中,“Solution 1”對(duì)應(yīng)于使用模運(yùn)算符的第一種方案,“Solution 2”代表第二種方案。

可以看出,第一種方案需要 35 個(gè)時(shí)鐘周期,由于時(shí)鐘周期為 10 ns,因此需要 350 ns才能生成輸出。然而,第二種方案只需要 23.607 ns 即可生成輸出。所以第二個(gè)實(shí)現(xiàn)速度快了 14.83 倍。

此外,第二種方案在 FPGA 上使用的資源要少得多。

結(jié)論

設(shè)計(jì)高效的組合電路是在 HLS 中開發(fā)算法或系統(tǒng)控制器的第一步。多種優(yōu)化技術(shù)和編碼風(fēng)格可用于描述復(fù)雜算法的組合部分。

審核編輯:劉清

-

邏輯電路

+關(guān)注

關(guān)注

13文章

490瀏覽量

42452 -

asic

+關(guān)注

關(guān)注

34文章

1175瀏覽量

119975 -

RTL

+關(guān)注

關(guān)注

1文章

384瀏覽量

59503 -

組合電路

+關(guān)注

關(guān)注

0文章

10瀏覽量

6683 -

HLS

+關(guān)注

關(guān)注

1文章

128瀏覽量

23907

原文標(biāo)題:組合電路在 HLS 中的重要性

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

探索Vivado HLS設(shè)計(jì)流,Vivado HLS高層次綜合設(shè)計(jì)

如何在HLS 14.3中編寫pow功能?

如何使用Vivado HLS生成了一個(gè)IP

合成中的Vivado HLS中的Pragma錯(cuò)誤怎么解決

【正點(diǎn)原子FPGA連載】第一章HLS簡(jiǎn)介-領(lǐng)航者ZYNQ之HLS 開發(fā)指南

Vivado HLS設(shè)計(jì)流的相關(guān)資料分享

FPGA高層次綜合HLS之Vitis HLS知識(shí)庫簡(jiǎn)析

使用Vitis HLS創(chuàng)建屬于自己的IP相關(guān)資料分享

HLS中RTL無法導(dǎo)出IP核是為什么?

組合邏輯電路中的競(jìng)爭(zhēng)冒險(xiǎn)

hls協(xié)議是什么?hls協(xié)議詳細(xì)介紹

FPGA設(shè)計(jì)中的HLS 工具應(yīng)用

hls之xfopencv

組合邏輯電路中的危害

HLS中組合電路對(duì)設(shè)計(jì)的影響

HLS中組合電路對(duì)設(shè)計(jì)的影響

評(píng)論