其他端接方式:

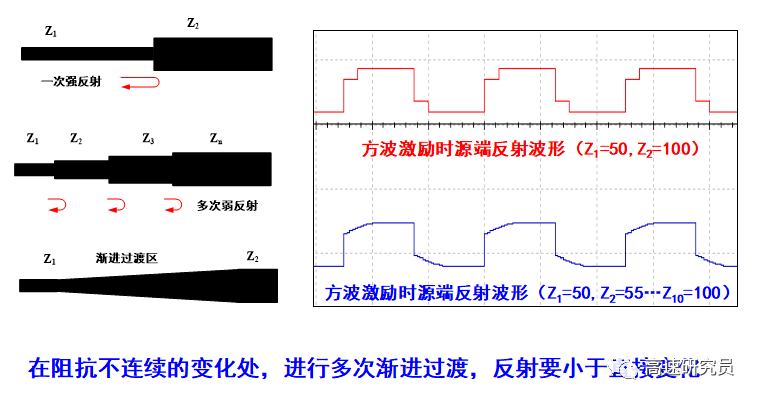

3.過渡匹配

優點:成本低,功耗低。在高速高頻信號中應用廣泛。

缺點:反射依然存在,只是優化。

4.使用Power Divider / Splitter

仿真驗證結果表明,端接技術可以有效抑制傳輸線上的反射噪聲,改善高速電路的性能。任何一種端接匹配都要和拓撲相聯系,根據信號質量的要求并綜合考慮端接技術對信號的影響,才能得到最佳的端接匹配效果。篇幅限制,后續再介紹常用的一些端接和匹配實例。

5.多負載端接技術

在實際電路中常常會遇到單一驅動源驅動多個負載的情況,這時需要根據負載情況及電路的布線拓撲結構來確定端接方式和使用端接的數量。一般情況下可以考慮以下兩種方案。

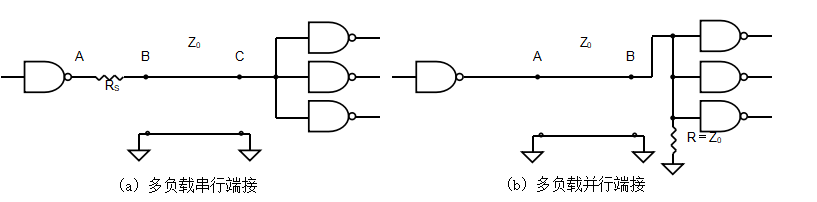

多負載串行方式下的端接策略

如果多個負載之間的距離較近,可通過一條傳輸線與驅動端連接,負載都位于這條傳輸線的終端,這時只需要一個端接電路。如采用串行端接,則在傳輸線源端加入一串行電阻即可,上圖a所示。

如采用并行端接(以簡單并行端接為例),則端接應置于離源端距離最遠的負載處,同時,線網的拓撲結構應優先采用菊花鏈的連接方式,如上圖b所示。

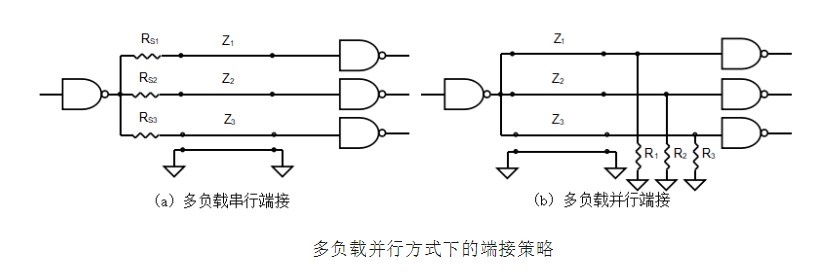

如果多個負載之間的距離較遠,需要通過多條傳輸線與驅動端連接,這時每個負載都需要一個端接電路。

如采用串行端接,則在傳輸線源端每條傳輸線上均加入一串行電阻,如下圖a所示。如采用并行端接(以簡單并行端接為例),則應在每一負載處都進行端接,如下圖b所示。

在采用匹配的時候,但要確保匹配元件盡量靠近源端或負載端,這樣可以減少電感,使匹配更為有效。

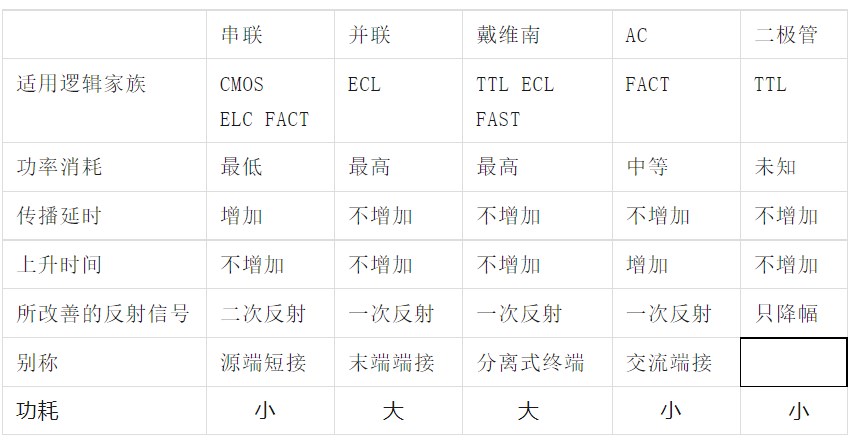

6.端接技術比較

7.不同工藝器件的端接策略

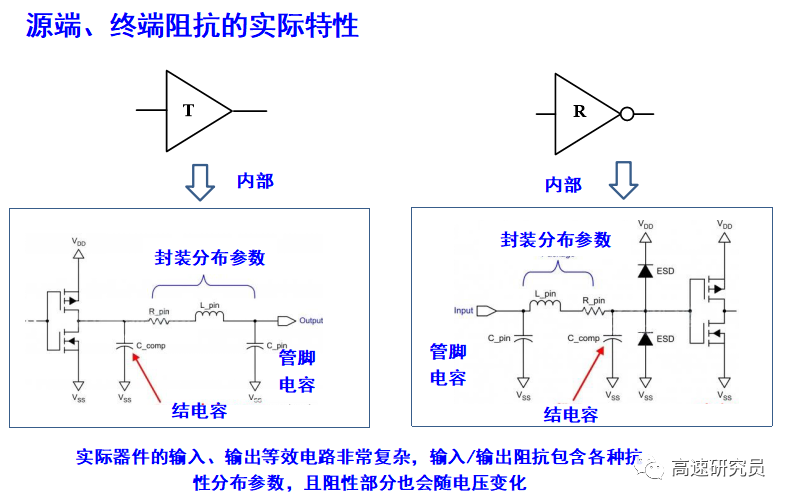

阻抗匹配與端接技術方案隨著互聯長度和電路中邏輯器件的家族在不同也會有所不同,只有針對具體情況,使用正確適當的端接方法才能有效地減小信號反射。

一般來說,對于一個CMOS工藝的驅動源,其輸出阻抗值較穩定且接近傳輸線的阻抗值,因此對于CMOS器件使用串行端接技術就會獲得較好的效果。而TTL工藝的驅動源在輸出邏輯高電平和低電平時其輸出阻抗有所不同,這時,使用并行戴維寧端接方案則是一種較好的策略。

ECL器件一般都具有很低的輸出阻抗,因此,在ECL電路的接收端使用一下拉端接電阻(下拉電平需要根據實際情況選取)來吸收能量則是ECL電路的通用端接技術。

當然,上述方法也不是絕對的,具體電路上的差別、網絡拓撲結構的選取、接收端的負載數等都是可以影響端接策略的因素,因此在高速電路中實施電路的端接方案時,需要根據具體情況通過分析仿真來選取合適的端接方案以獲得最佳的端接效果。

-

阻抗匹配

+關注

關注

14文章

348瀏覽量

30756 -

TTL電路

+關注

關注

2文章

65瀏覽量

15064 -

傳輸線

+關注

關注

0文章

375瀏覽量

23998 -

CMOS工藝

+關注

關注

1文章

58瀏覽量

15663 -

ECL

+關注

關注

0文章

38瀏覽量

13417

發布評論請先 登錄

相關推薦

傳輸線在阻抗匹配時串聯端接電阻為什么要靠近發送端

淺析阻抗匹配及其應用

傳輸線阻抗匹配

從阻抗匹配的角度來解析射頻微波傳輸線的設計技術

微帶傳輸線阻抗匹配應用經驗

ps脈沖傳輸線的多容性負載阻抗匹配模型和計算

解析通信網路的阻抗匹配與射頻傳輸線的設計技術

微帶傳輸線阻抗匹配電路設計

淺談阻抗匹配(七)傳輸線的端接技術

淺談阻抗匹配(七)傳輸線的端接技術

評論