高速先生成員--黃剛

高速先生經常會說一句話,那就是對于信號質量的優化是無極限的,這里說的優化,其實說的就是PCB的設計優化。首先肯定的是,不同的設計工程師去做同樣一塊PCB板的設計,做出來的肯定都不會完全一樣。那不一樣就意味著信號的性能有差異。舉個例子,兩位工程師都去設計同一款10G的高速產品的PCB信號通道,可能兩位工程師能力都很強,很多的高速設計規則都能夠掌握。的確,他們設計出來的產品在功能測試上都能夠pass。但是在都能pass的情況下其實也能卷起來,例如在pass的前提下分別進行眼圖的測試,可能一位工程師設計的這條通道是眼高200mV,另外一位工程師卻達到了250mV!

雖然對于高速先生來說,也不太提倡這個內卷的方式,但是不代表不優化哈,我們的基本目標是通過合適的設計優化能夠留出足夠的裕量,保證板子能夠順利工作。如果在這個基礎上有些客戶的產品的確是需要有更嚴苛的要求,高速先生也同樣可以欣然奉陪哈,不過可能付出的設計代價可能是更高等級的板材,更高成本的工藝能力等等。。。

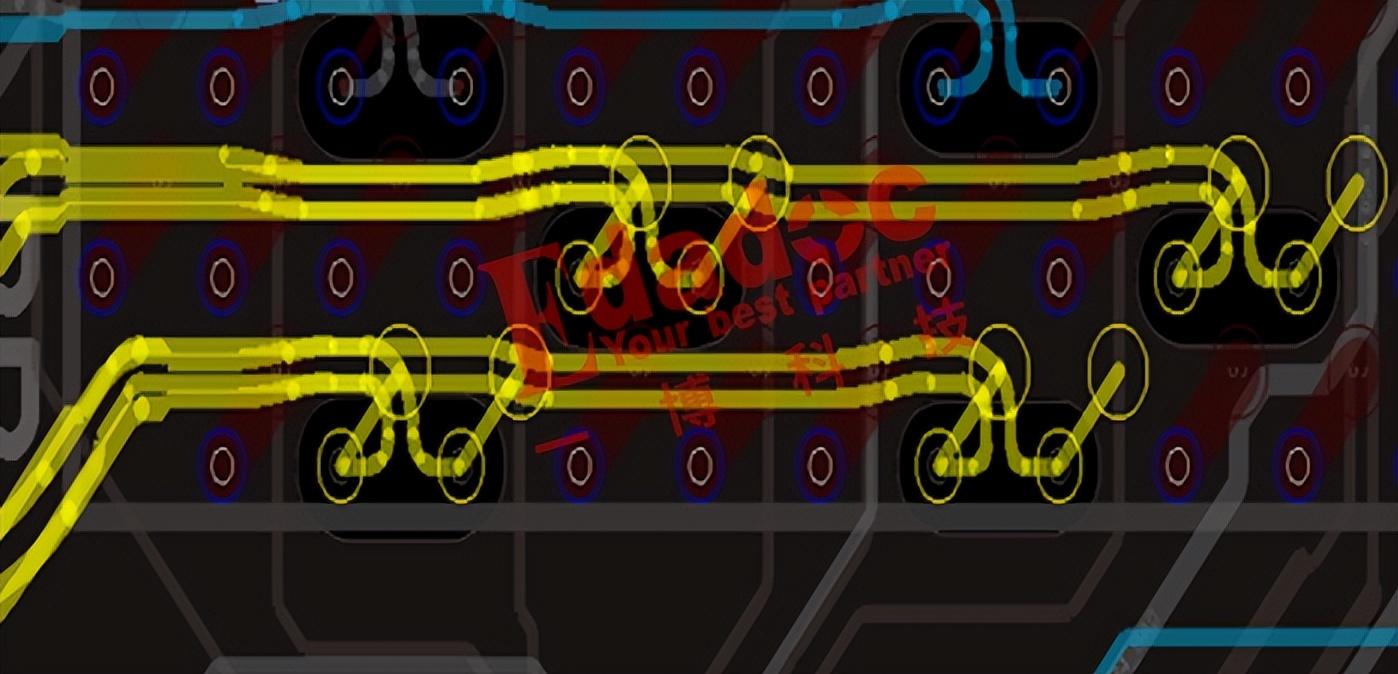

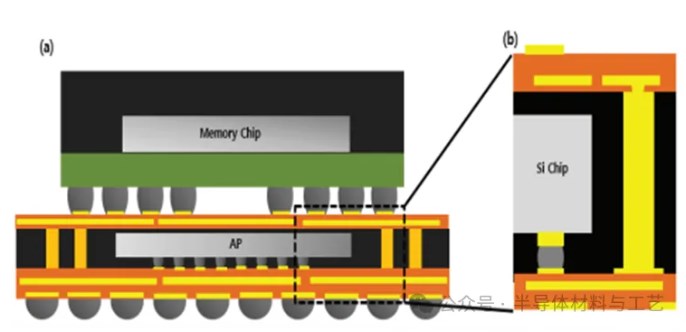

開場白有點長哈,大家都有點等不及了,正題來啦!Chris最近正在研究高速信號之間在BGA扇出這個位置的串擾,大家知道,一般在BGA內,高速信號都是相鄰的,因此要通過打過孔到內層,然后走出BGA,這就是所謂的BGA扇出。

這種BGA扇出結構設計對高速信號性能而言,難點就2個,一是這個扇出位置的阻抗優化,其實基本上說的就是扇出過孔的阻抗優化了;第二個就是相鄰高速信號線之間的串擾了。什么!你不會還以為說的串擾主要來自于走線和走線之間的串擾吧?

BGA扇出的串擾當然主要是由扇出過孔之間導致的,因此Chris研究了在高速信號分配到不同BGA的pin位置情況下,相鄰兩對信號的扇出過孔串擾到底有多大的差異。沒聽懂什么意思嗎?不要緊,Chris畫了圖告訴你們。

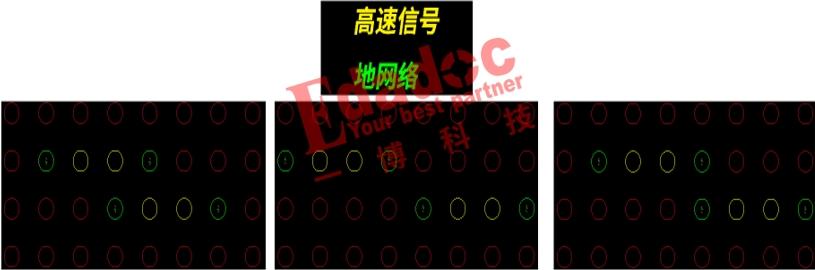

Chris設計了幾個簡單的BGA扇出場景,分別來模擬高速信號pin和地網絡pin的不同分布方式,其實設計工程師是很容易發現它們的差異的。從左到右可以發現,相鄰的兩對高速差分線的pin在X方向慢慢變遠,其實也就是我們在BGA的pin排列里面經常會遇到的三種高速信號pin的分布方式了。那么到底這三種方式下扇出過孔之后的串擾性能如何呢?

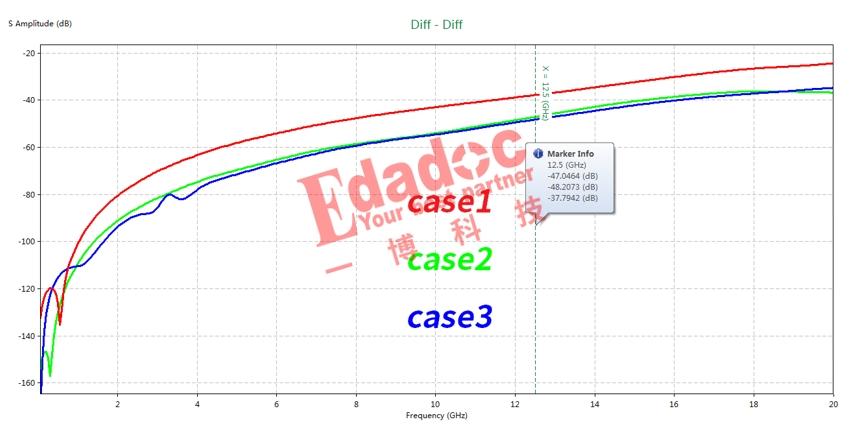

扇出完之后就這個樣子了,為了減小變量,兩對信號通過過孔是換到同一個內層扇出的哈,除了這個之外,過孔的反焊盤處理方式也是一樣,另外大家可能還沒注意到另外一點,那就是地過孔的數量也是一樣的哈!比較三種case兩對高速信號扇出的串擾?相信都不需要Chris了,設計工程師自己都能夠比較出來了吧。當然Chris能告訴你們的是,他們的具體串擾值。

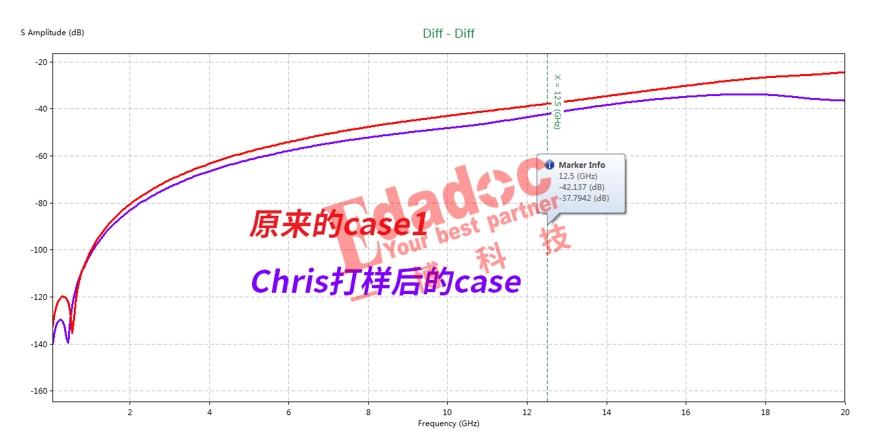

以25Gbps信號為例,我們看到12.5GHz這個頻點上的串擾,case2比case1好了差不多10個db,case2到case3的改善就不明顯了,因為已經很小了,也符合理論。

這時坐在旁邊的雷豹也加入起來了,作為設計出身的他,也提出了自己的觀點。他認為不同pin的分布是原理圖已經定好的,當然兩對高速信號的pin本身就遠的話,串擾天然就好啊,這又不是設計工程師所能夠改變的!

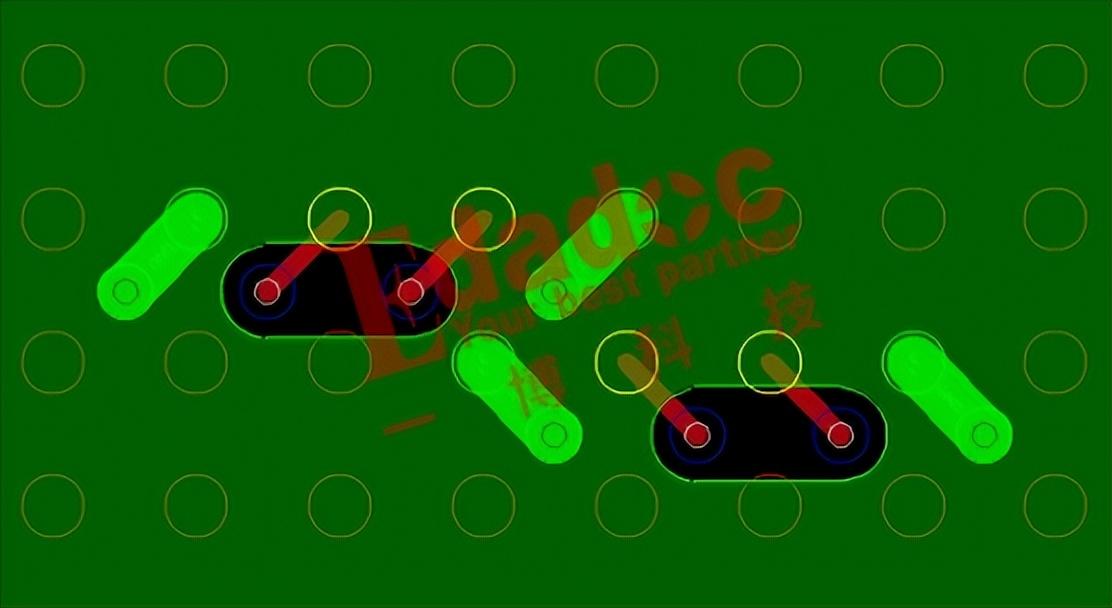

話粗理不糙,Chris當然也贊同哈,但是贊同率就沒那么高。然后Chris就拿出上面的case1和雷豹說,case1是兩對高速信號pin最近的case了,當然串擾也是最差的。那么它就一定沒辦法通過設計做優化了嗎?

看到雷豹若有所思的樣子,Chris決定先給雷豹打個樣!同樣的高速信號pin和地pin的位置不變,如果從case1變成這樣呢?

然后Chris再不緊不慢的做個仿真驗證下,這不就5db的串擾裕量就多起來了嗎!

哦哦!雷豹突然就懂了,然后不等Chris開口,自己就跳起來先說,我還能想到其他的PCB優化方式!

好啊,那我們大家就一起等著唄!

大家也幫忙一起想想哈,pin不變的情況下,還有什么PCB優化的方式能改善原來case1的串擾呢?

審核編輯 黃宇

-

BGA

+關注

關注

4文章

537瀏覽量

46733 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發布評論請先 登錄

相關推薦

BGA芯片在汽車電子中的應用

BGA芯片的測試方法與標準

BGA芯片的封裝類型 BGA芯片與其他封裝形式的比較

BGA芯片的定義和原理

BGA封裝與SMT技術的關系

BGA封裝對散熱性能的影響

BGA封裝技術的發展 BGA封裝的優勢與應用

智能手機SoC扇出技術(Fan-Out)的應用與探索

SMT貼片中BGA封裝的優缺點

有沒搞錯!花了大價錢的激光孔設計性能竟然不如普通通孔?

同樣是升壓電路,MCU+MOS+電感這個方式和升壓芯片+MOS+電感這個方式,有哪些優缺點和異同點?

同樣是運動感應,微波雷達感應技術和紅外感應技術有什么區別?

解析扇入型封裝和扇出型封裝的區別

同樣是BGA扇出,為什么別人設計出來的性能就是比你好!

同樣是BGA扇出,為什么別人設計出來的性能就是比你好!

評論