觀看視頻,您將了解為什么千兆多媒體串行鏈路(GMSL) SerDes技術能夠提供傳輸容量激增的多類數據所需的帶寬,從而成功在車輛中部署復雜的ADAS和信息娛樂功能。

GMSL

旨在將高速視頻鏈路性能提升到全新水平

ADI公司的千兆多媒體串行鏈路(GMSL)技術支持在汽車中可靠地傳輸高分辨率數字視頻,從而改變數百萬駕駛員的駕駛體驗。公路上行駛的車輛中已有超過6億個GMSL鏈路,這些車輛來自25家以上的汽車制造商。自2004年以來,部署這些鏈路的汽車總計行駛了超過20萬億公里,即超過2光年,改善了道路安全、用戶界面和車內娛樂,造福于數百萬用戶。每公里的行駛里程都能提供寶貴的數據以改進下一代GMSL,并通過領先的ASIL兼容解決方案實現視頻鏈路功能安全的新標準。

然而,應用于汽車僅僅是個開始。探索GMSL在安全性、自主性等方面的創新應用,讓未來的機器“超越一切可能”。

汽車中的攝像頭和顯示屏的數量不斷增加,圖像質量不斷提高,因此需要更高的數據速率進行視頻傳輸。GMSL旨在支持這些趨勢,并在此過程中簡化系統架構。GMSL鏈路可傳輸汽車中的所有視頻,包括攝像頭到計算機、計算機之間以及從計算機到顯示屏的視頻。攝像頭為道路安全、駕駛輔助和智能用戶界面提供了支持。顯示屏正在取代機械儀表和控件,并為駕駛員提供關鍵信息和信息娛樂。

ADI公司每一代GMSL的鏈路數據速率都比上一代提高了一倍。

GMSL1支持高達3 Gbps的鏈路

GMSL2支持高達6 Gbps的鏈路

已量產的最新一代GMSL3提供12 Gbps的鏈路速率

下一代GMSL將繼續創新,進一步為更高性能的計算和軟件定義應用提供高級特性和功能。

ADI 讓新一代GMSL向后兼容上一代產品,從而簡化客戶從一代GMSL過渡到下一代GMSL的過程。

GMSL

優勢展示

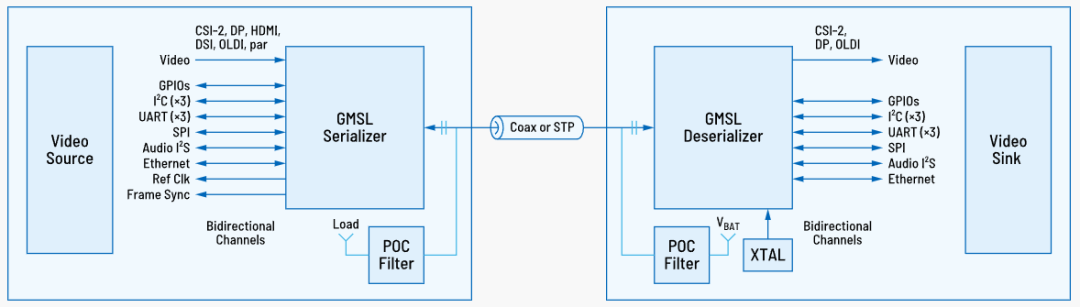

GMSL連接框圖

一切通過單根線纜傳輸

GMSL通過單根同軸電纜或屏蔽雙絞線(STP)線纜來橋接ADAS傳感器所需的一切。

視頻、供電、攝像頭和顯示屏控制與同步、觸控、觸覺反饋、時鐘、音頻、軟件更新以及狀態報告,全都可以通過同一條線纜同時傳輸。

采用GMSL的攝像頭通常只有一個連接器,該連接器能提供攝像頭所需的一切,并將視頻從攝像頭傳輸出去。

每個GMSL鏈路可以傳輸多個視頻流。

更少的連接器和線纜意味著重量更輕、復雜性更低

GMSL能夠通過單根線纜來橋接和傳輸一切,因此降低了布線要求,減少了影音系統的重量、能耗和成本。線纜的減少可提高燃油經濟性,或延長電動汽車的續航里程。

顯示屏可以采用菊花鏈連接,從而進一步減少布線。GMSL促進了增量數據聚合,因此車輛變得更輕,制造更簡單,操作更簡便。

任何視頻協議都可以通過GMSL鏈路橋接到任何其他視頻協議。例如,DisplayPort轉CSI-2,或HDMI轉OLDI。

高性能汽車ASIL串行器/解串器解決方案

ADI的GMSL鏈路是汽車SerDes市場中性能領先的產品,其數據速率高達12 Gbps,目前已大規模量產。我們的創新以安全性、可靠性和性能為核心。GMSL支持實現所需的任何級別的ASIL解決方案。

完整的低功耗、小尺寸器件組合

ADI的持續創新和100多款優化器件的組合,確保GMSL器件為每種使用場景提供小尺寸和低功耗的解決方案。

審核編輯:湯梓紅

-

ADI

+關注

關注

144文章

45812瀏覽量

248703 -

GMSL

+關注

關注

2文章

26瀏覽量

15641 -

串行鏈路

+關注

關注

0文章

7瀏覽量

8147

原文標題:為什么每輛汽車都需要高速串行鏈路?

文章出處:【微信號:ADI智庫,微信公眾號:ADI智庫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速串行鏈路仿真工具應用實戰

高速數據保障交通安全:專用高速視頻鏈路

時鐘抖動對高速鏈路性能的影響

高速時鐘如何驅動串行鏈路?

時鐘抖動對高速鏈路性能的影響

消除高速串行鏈路的時鐘抖動

基于FPGA連接的JESD204B高速串行鏈路設計需要考慮的基本硬件及時序問題詳解

為什么每輛汽車都需要高速串行鏈路?

為什么每輛汽車都需要高速串行鏈路?

評論