電子發燒友網報道(文/周凱揚)隨著摩爾定律越來越難以維系,晶體管擴展帶來的性能與成本優勢逐漸減弱,半導體行業已經面臨著新的拐點。Chiplet和3DIC集成的方案相較傳統的單片技術相比,占用空間更小、性能更高,也因此成了新的設計主流,席卷了AI、服務器與汽車芯片等市場。但新的設計方案除了需要新一代的die-to-die的接口IP、2.5D/3D的封裝技術外,也需要在EDA工具與工作流上做出創新。

西門子3D IC設計流工具

為了解決3DIC集成在設計工具上面臨的挑戰,西門子推出了3D IC設計流工具和IC封裝解決方案,用于開發先進的2.5D/3D IC異構SIP設計。這套設計流工具包括3DIC架構、設計、分析、測試和可靠性工作流。

其中3D IC架構工作流使得3DIC在STCO架構探索和預測分析上有了可能,系統和RTL設計師可以利用通用的連接IP模型庫,快速找到可行的設計架構,比如Chiplet元件和標準D2D接口,在設計初期就能對PPA有個評估。

可靠性工作流則主要用于解決3DIC設計面臨的另外兩大挑戰,熱管理和機械應力。盡管不少EDA設計工具都支持大規模的3D疊加,但仍需要考慮多芯片熱功率曲線、熱相互作用,以及堆疊芯片和硅中介層存在的潛在機械應力問題。可靠性工作流通過協同仿真與優化,來對熱管理和機械應力進行分析,從而確保先進SiP設計達到目標質量、良率和可靠性。

值得一提的是,西門子也在呼吁推出3DIC設計工具的一套標準,在將多供應商的Chiplet集成到一個異構封裝中去時,也需要Chiplet的供應商提供給客戶一套標準化的設計模型,這樣才能確保其完美融入終端用戶的EDA工具設計流中,比如模擬Chiplet需要一個以Verilog-AMS實現的模擬功能模型。像臺積電的3Dblox,就屬于在早期提高設計效率的一套開放標準。

芯和半導體3DIC Chiplet先進封裝設計分析全流程EDA平臺

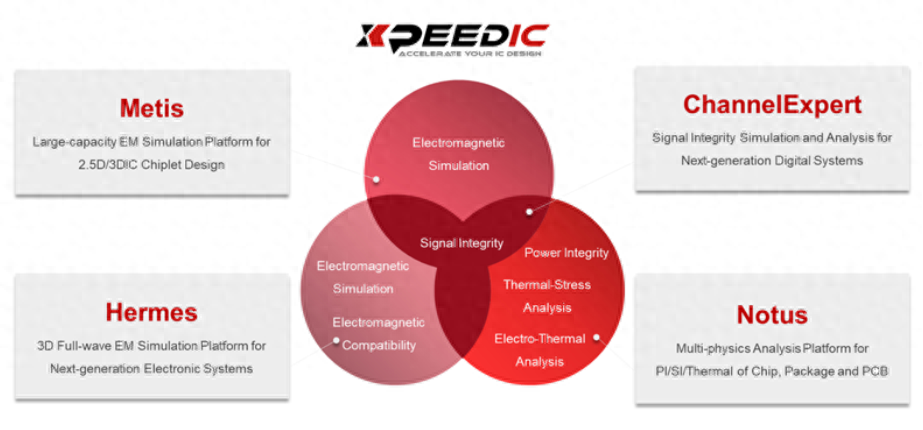

芯和半導體為國內首家推出3DIC Chiplet先進封裝設計分析全流程EDA平臺的公司,集合了新思科技的3DIC Compiler這一2.5D/3D多裸晶芯片封裝協同設計與分析方案,以及Metis這一芯和半導體自研的2.5D/3DIC先進封裝EDA仿真方案等,提供了一套完整的3DIC設計、仿真和驗證方案,涵蓋了臺積電CoWoS-S/R/L、英特爾EMIB和三星I/H Cube等多工藝平臺。

其中3D Compiler提供了一個直觀的2D、3D界面,供設計者對集成數億晶體管的多裸晶2.5D/3D芯片進行系統集成,且支持臺積電、三星等主流晶圓代工廠的工藝/封裝文件格式。該工具涵蓋了HBM堆疊、異構邏輯芯片堆疊以及邏輯芯片上的內存堆疊等。

而Metis則可以跳過傳統建模工具的配置過程,通過考慮關鍵區域內的物理環境來快速完成仿真設計的優化,從而實現超大規模異構封裝的高精度仿真需求。今年全新升級的Metis已經全面支持了各種Interposer工藝,SI仿真在精度和效率上都實現了遙遙領先,同時新增了前仿真模板和金屬蝕刻腳功能。

寫在最后

隨著AI計算帶來的又一波新品潮,3D集成的芯片設計勢必會被更廣泛地應用。以AMD為例,他們的3D集成不僅僅是用在了V-Cache上,同樣也將用于CPU、GPU和內存的Chiplet架構上。這也是為何AMD在即將發布的MI300系列加速器上,敢給出8倍AI性能和5倍能耗比的指標。為了支持更多這類設計的出現,而不再僅僅面向一小批具備先進開發經驗的玩家,EDA廠商們也應該盡快擁抱3D集成的設計。

-

eda

+關注

關注

71文章

2708瀏覽量

172868

發布評論請先 登錄

相關推薦

小小的EDA市場,已經擠滿了86家國產供應商...

大模型時代的算力需求

特斯拉韓國公布Model 3/Y電池供應商陣容:寧德時代、松下、LG新能源

如何選擇工業電容器供應商

新思科技攜手英特爾推出可量產Multi-Die芯片設計解決方案

新思科技面向英特爾代工推出可量產的多裸晶芯片設計參考流程,加速芯片創新

新思科技與臺積公司深度合作,推動芯片設計創新

現場速遞|橋田智能榮獲柯馬“最具競爭力供應商”獎項

聯電獲蘋果iPhone 16天線模塊核心芯片訂單

正力新能榮獲德業供應商“2023年度優秀品質獎”

新思科技與英特爾深化合作,以新思科技IP和經Intel 18A工藝認證的EDA流程加速先進芯片設計

芯和半導體最新發布“SI/PI/多物理場分析”EDA解決方案

大算力時代下,跨越多工藝、多IP供應商的3DIC也需要EDA支持

大算力時代下,跨越多工藝、多IP供應商的3DIC也需要EDA支持

評論