點(diǎn)擊藍(lán)字關(guān)注我們

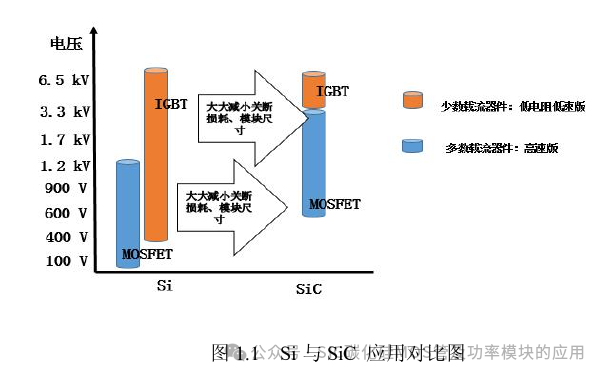

對(duì)于高壓開(kāi)關(guān)電源應(yīng)用,碳化硅或SiC MOSFET與傳統(tǒng)硅MOSFET和 IGBT相比具有顯著優(yōu)勢(shì)。SiCMOSFET很好地兼顧了高壓、高頻和開(kāi)關(guān)性能優(yōu)勢(shì)。它是電壓控制的場(chǎng)效應(yīng)器件,能夠像IGBT一樣進(jìn)行高壓開(kāi)關(guān),同時(shí)開(kāi)關(guān)頻率等于或高于低壓硅MOSFET的開(kāi)關(guān)頻率。之前的文章中,我們介紹了SiCMOSFET特有的器件特性和如何優(yōu)化SiC柵極驅(qū)動(dòng)電路。今天將帶來(lái)本系列文章的第三部分SiC MOSFET的封裝、系統(tǒng)性能和應(yīng)用。

封裝

WBG半導(dǎo)體使高壓轉(zhuǎn)換器能夠在更接近低壓轉(zhuǎn)換器(低于100V)開(kāi)關(guān)頻率的情況下工作。對(duì)于低壓轉(zhuǎn)換器而言,半導(dǎo)體封裝的發(fā)展對(duì)當(dāng)今開(kāi)關(guān)性能的實(shí)現(xiàn)起到了關(guān)鍵作用。硅MOSFET封裝取得了進(jìn)步,例如雙面散熱、夾焊、熱增強(qiáng)功率封裝和低電感、無(wú)引線(xiàn)封裝。同樣,柵極驅(qū)動(dòng)器IC封裝也“瘦身”明顯。更短的芯片到引線(xiàn)、鍵合線(xiàn)連接,加上模制無(wú)引線(xiàn)封裝(MLP),對(duì)于最大限度地減少驅(qū)動(dòng)器側(cè)的寄生電感至關(guān)重要。驅(qū)動(dòng)器和MOSFET(DrMOS)共封裝是減少寄生電感、提高效率和縮小電路板面積的最新步驟。DrMOS得以實(shí)現(xiàn)也是因?yàn)橐肓祟?lèi)似低壓轉(zhuǎn)換器應(yīng)用中所使用的封裝改進(jìn)措施。

在高壓轉(zhuǎn)換器領(lǐng)域,爬電距離和電氣間隙等最小間距要求使得高性能 SiC MOSFET依然采用低性能To?220型和To?247型封裝。這些封裝已經(jīng)十分完善,長(zhǎng)期以來(lái)一直是行業(yè)標(biāo)準(zhǔn)。它們非常適合工業(yè)應(yīng)用,堅(jiān)固且易于散熱,但其長(zhǎng)引線(xiàn)和內(nèi)部鍵合線(xiàn)導(dǎo)致寄生電感更高。SiC MOSFET現(xiàn)在使這些寄生電感受到熱應(yīng)力、頻率和dV/dt速率的影響,以前在高壓硅晶體管中,這是從未設(shè)想到的。可以說(shuō),SiC促進(jìn)了對(duì)高壓分立封裝的重新思考。

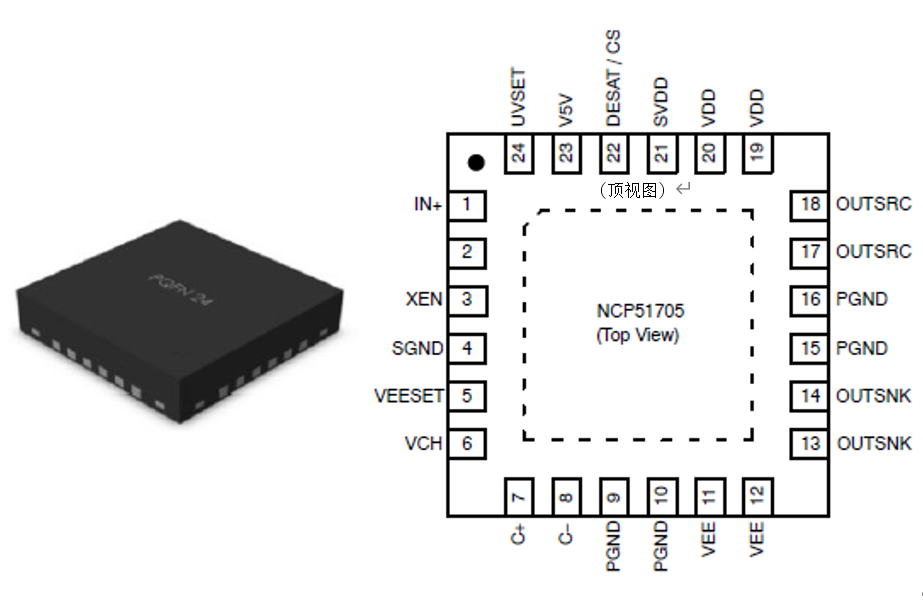

不像分立器件,SiC柵極驅(qū)動(dòng)器能夠充分利用那些原本用于低壓電源轉(zhuǎn)換器的驅(qū)動(dòng)器件的封裝改進(jìn)。NCP5170芯片封裝成24引腳、4x4 mm、熱增強(qiáng)MLP,如圖15所示。

圖15.NCP51705 24引腳、4x4mm、MLP封裝和引腳輸出

所有高電流電源引腳都布了兩個(gè),位于IC的右半部分。此外,這些引腳都通過(guò)內(nèi)部雙鍵合線(xiàn)連接到芯片,以實(shí)現(xiàn)盡可能最低的電感。所有低功耗數(shù)字信號(hào)僅為單引腳,位于IC的左半部分,為PWM或數(shù)字控制器提供了方便、直接的接口。

NCP51705封裝的底部包括一個(gè)電絕緣、導(dǎo)熱、暴露的焊盤(pán)。該焊盤(pán)未連接到PGND或SGND,但會(huì)通過(guò)熱通孔連接到隔離銅PCB焊盤(pán)進(jìn)行散熱。

如果散熱成為一個(gè)問(wèn)題,應(yīng)特別注意四個(gè)主要的功耗因素:

-

與驅(qū)動(dòng)外部SiC MOSFET相關(guān)的OUTSRC和OUTSNK損耗。這些是與開(kāi)關(guān)頻率成比例的柵極電荷相關(guān)損耗。降低開(kāi)關(guān)頻率將降低功耗;

-

VDD和V5V之間的LDO,能夠提供高達(dá)20mA的電源。切勿加載V5V到其他負(fù)載,電壓軌僅用于數(shù)字隔離器或光耦合器的偏壓

-

VDD和VCH之間的LDO,這是內(nèi)部電荷泵的一部分

-

內(nèi)部電荷泵電源開(kāi)關(guān),可禁用并用外部負(fù)偏壓替換,如電荷泵—VEE(VEESET)部分所述

系統(tǒng)性能

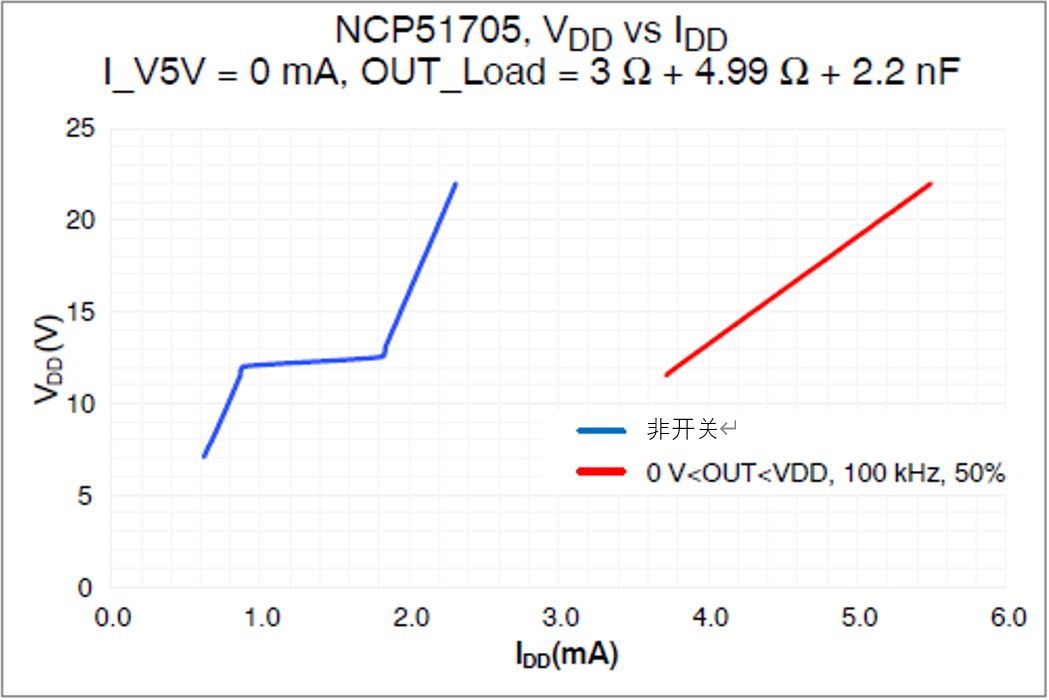

對(duì)于VDD>7V,靜態(tài)電流線(xiàn)性緩升,直至超過(guò)設(shè)置的UVLO閾值。圖16所示的藍(lán)色曲線(xiàn)表示在沒(méi)有PWM輸入信號(hào)并且VDD(UVLO)=12V,V5V調(diào)節(jié)器無(wú)負(fù)載的情況下,VDD相對(duì)于IDD的變化曲線(xiàn)。對(duì)于7V

紅色曲線(xiàn)表示在禁用內(nèi)部電荷泵的同時(shí)向IN+施加100kHz、50%占空比脈沖輸入的情況。使用4.99Ω+2.2nF負(fù)載,這是典型SiC MOSFET的等效輸入阻抗。外部灌拉電阻為3?。對(duì)于12V

圖16.VDD與IDD,非開(kāi)關(guān)與開(kāi)關(guān)

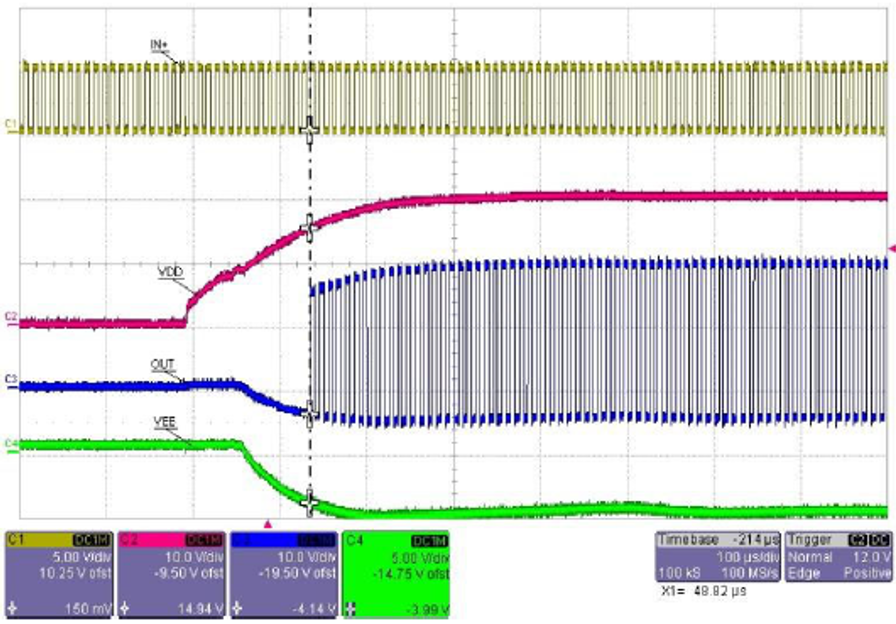

圖17所示的啟動(dòng)波形顯示了在VDD之前已經(jīng)輸入了PWM信號(hào)到IN+。VDD從0V上升至20V,UVSET=2V(未在圖中顯示),相當(dāng)于VDD(UVLO)=12V。VEE被設(shè)置為在?5V調(diào)節(jié),VEESET=V5V(未在圖中顯示),相當(dāng)于VEE(UVLO)=?4V。當(dāng)VEE=?4V時(shí),輸出便會(huì)使能,此時(shí)VDD>12V(VDD=15V)。還要注意,在近100μs的時(shí)間內(nèi),OUT(VGS)小于20V。根據(jù)VDD爬升的dV/dt速率,該時(shí)間可能更長(zhǎng),因此,在編程UVSET時(shí)應(yīng)考慮SiC MOSFET的熱應(yīng)力。

圖17.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

VDD(UVLO)=12V,VEE(UVLO)=-4V

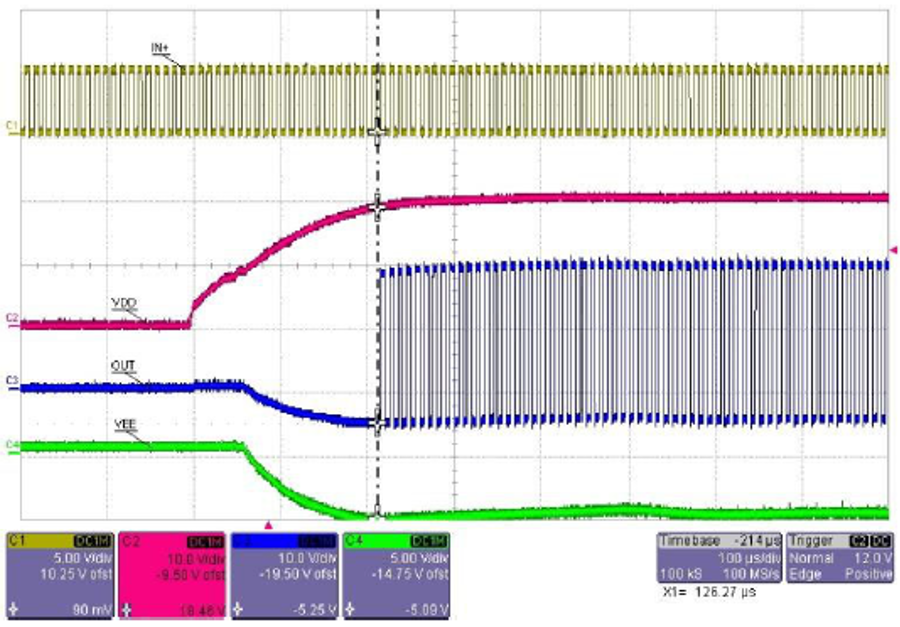

圖18中顯示了相同的啟動(dòng)波形,但UVSET=3V(未顯示),相當(dāng)于 VDD(UVLO)=18V。在這種情況下,當(dāng)VDD=18V時(shí),OUT(VGS)便會(huì)啟用,此時(shí)VEEEE=?5V)。哪個(gè)UVLO占優(yōu)勢(shì)取決于VDD與VEE的dV/dt速率。關(guān)鍵點(diǎn)是NCP51705輸出被禁用,直到VDD和VEE都高于或低于各自的UVLO閾值。與圖17相比,請(qǐng)注意較高的UVLO設(shè)置對(duì) OUT(VGS)的影響,其中第一個(gè)OUT脈沖出現(xiàn)在20V和?5V附近。

圖18.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

VDD(UVLO)=18V,VEE(UVLO)=-4V

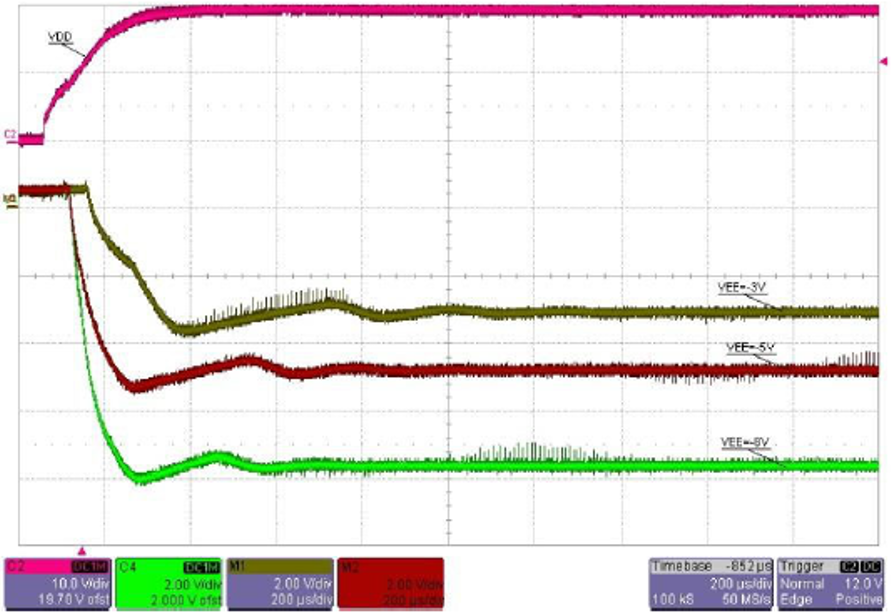

NCP51705內(nèi)部電荷泵有一個(gè)緩慢的控制回路,其效果可從VEE啟動(dòng)期間觀察到的輕微下沖和<400μs的穩(wěn)定時(shí)間中看出,如圖19所示。超過(guò)400μs時(shí),VEE電壓穩(wěn)定至?3V、?5V或?8V的調(diào)節(jié)設(shè)定值。

圖19.VEE啟動(dòng)

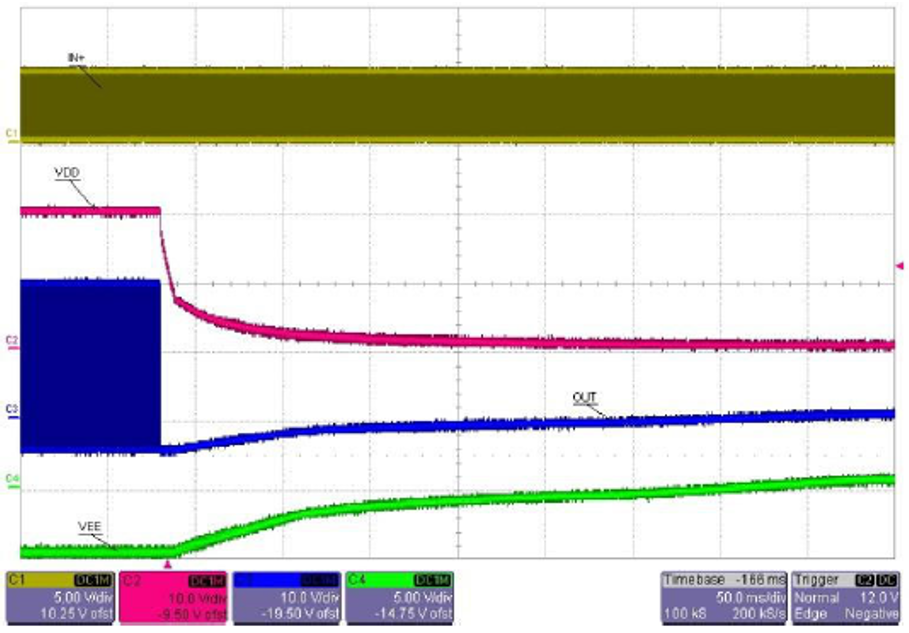

關(guān)機(jī)操作平穩(wěn),無(wú)毛刺。如圖20所示,OUT停止開(kāi)關(guān)并跟蹤掉電的 VEE。VEE從?5V到0V的放電時(shí)間約為300ms。

圖20.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;關(guān)閉

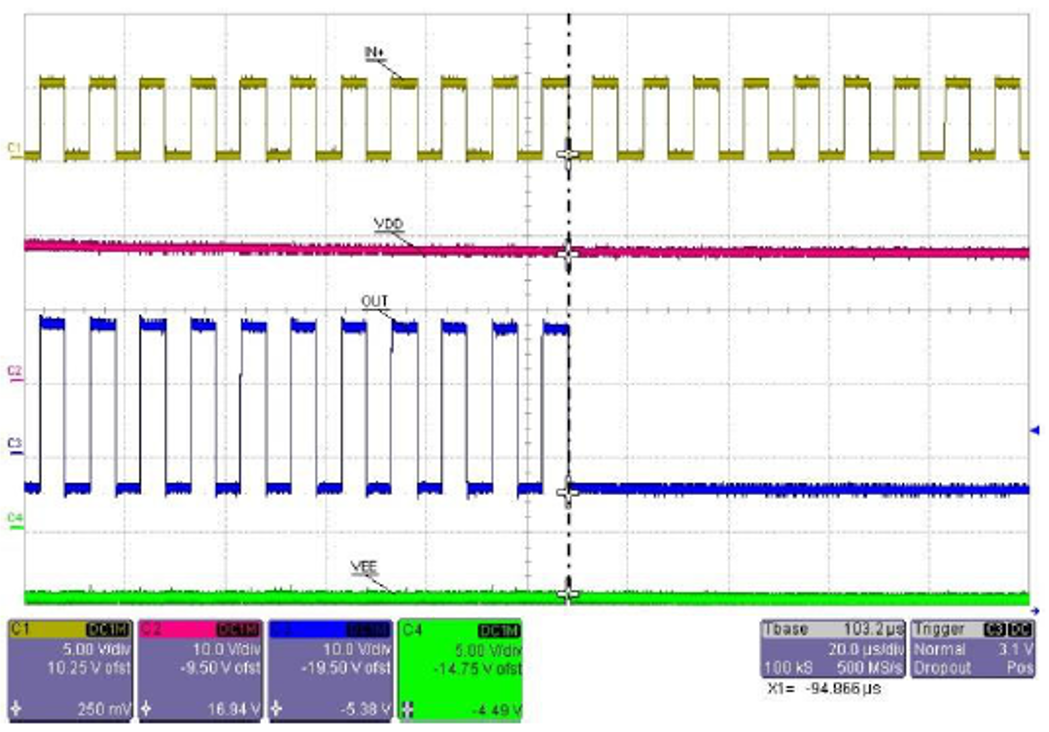

圖21顯示了圖20中時(shí)間基準(zhǔn)的放大圖。UVSET被配置為3V(VDD(UVLO)=18V),內(nèi)部VDD UVLO遲滯在內(nèi)部固定為1V。當(dāng)輸出被禁用時(shí),光標(biāo)位置顯示VDD=17V(18V?1V滯后),此時(shí)VEE=?4.5V(VEESET=V5V),并且根據(jù)其?4V UVLO仍處于有效電壓范圍。盡管VDD的衰減很慢,但在UVLO_OFF之后,也可以看到最后一個(gè)輸出脈沖的終止很干凈,沒(méi)有雜散脈沖或毛刺。

圖21.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

關(guān)閉,VDD_UVLO(OFF)=17V

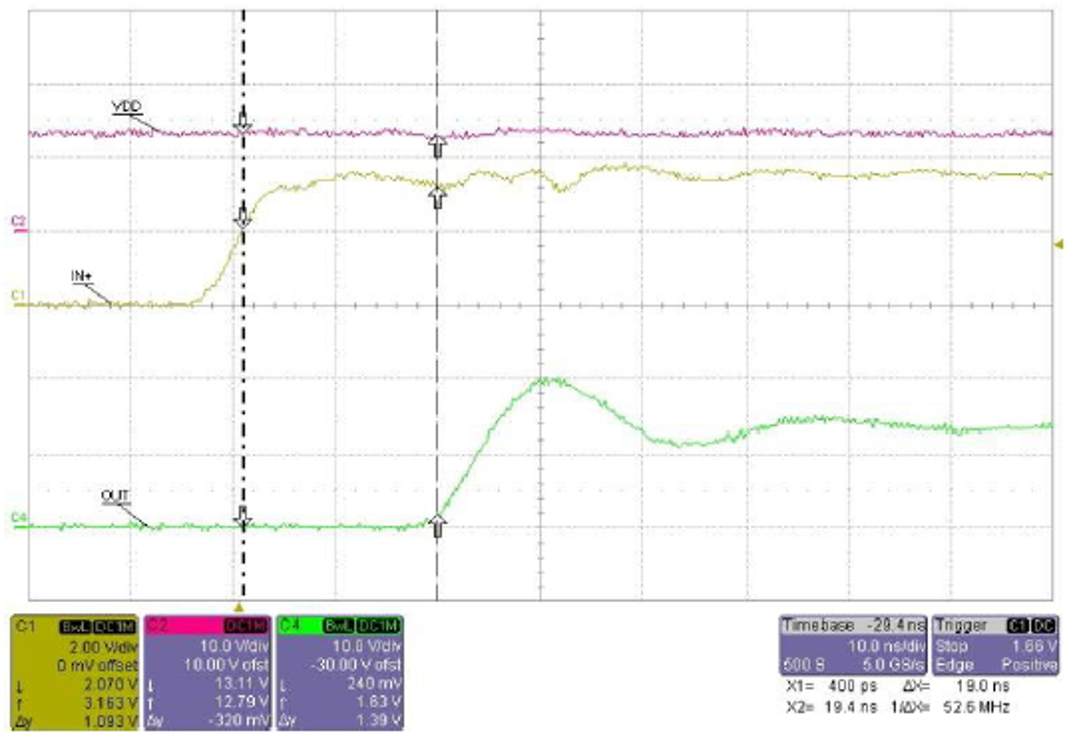

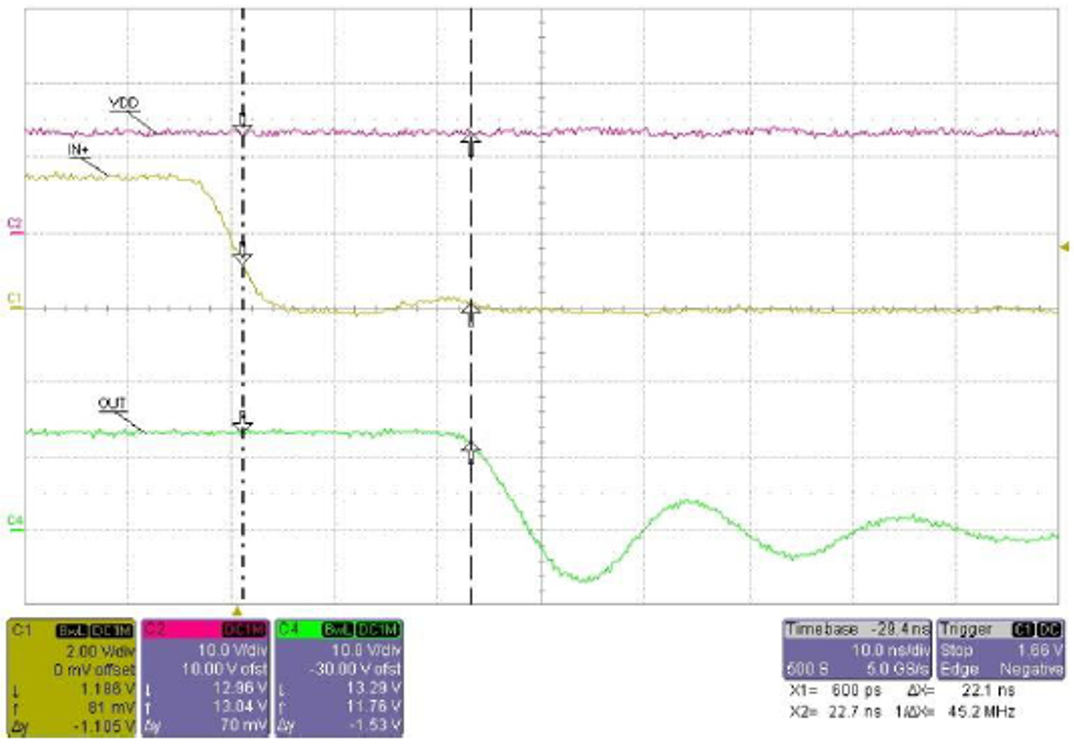

導(dǎo)通傳播延遲的測(cè)量范圍從90%IN+上升至10%OUT上升。通常SiC 驅(qū)動(dòng)器將在更高的VDD下工作,但大多數(shù)SiC MOSFET傳播延遲被指定為VDD=12V,1nF負(fù)載條件下的測(cè)得。圖22顯示了在這些標(biāo)準(zhǔn)測(cè)試條件下測(cè)得的導(dǎo)通傳播延遲為19ns。

圖22.CH1-IN+、CH2-VDD、CH4-OUT;上升沿傳播延遲

同樣,關(guān)斷傳播延遲的測(cè)量范圍從10%IN+下降至90%OUT下降。圖23顯示了在相同標(biāo)準(zhǔn)測(cè)試條件下測(cè)得的關(guān)斷傳播延遲為22ns。每個(gè)邊緣的輸出上升和下降時(shí)間約為5ns。

圖23.CH1-IN+、CH2-VDD、CH4-OUT;下降沿傳播延遲

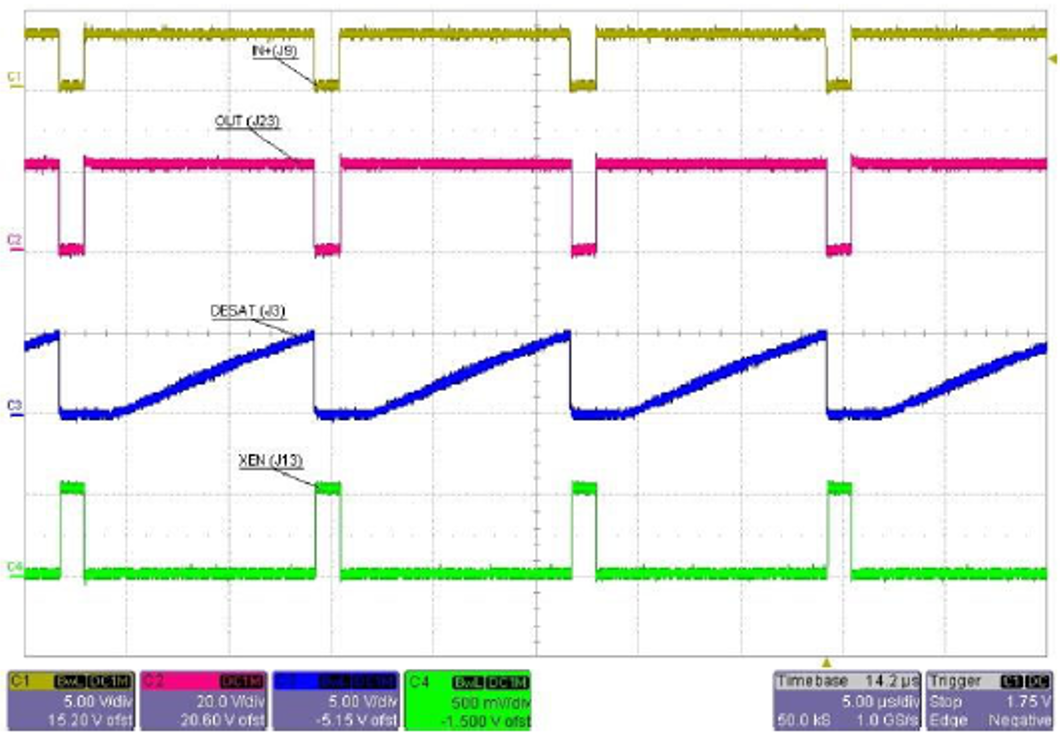

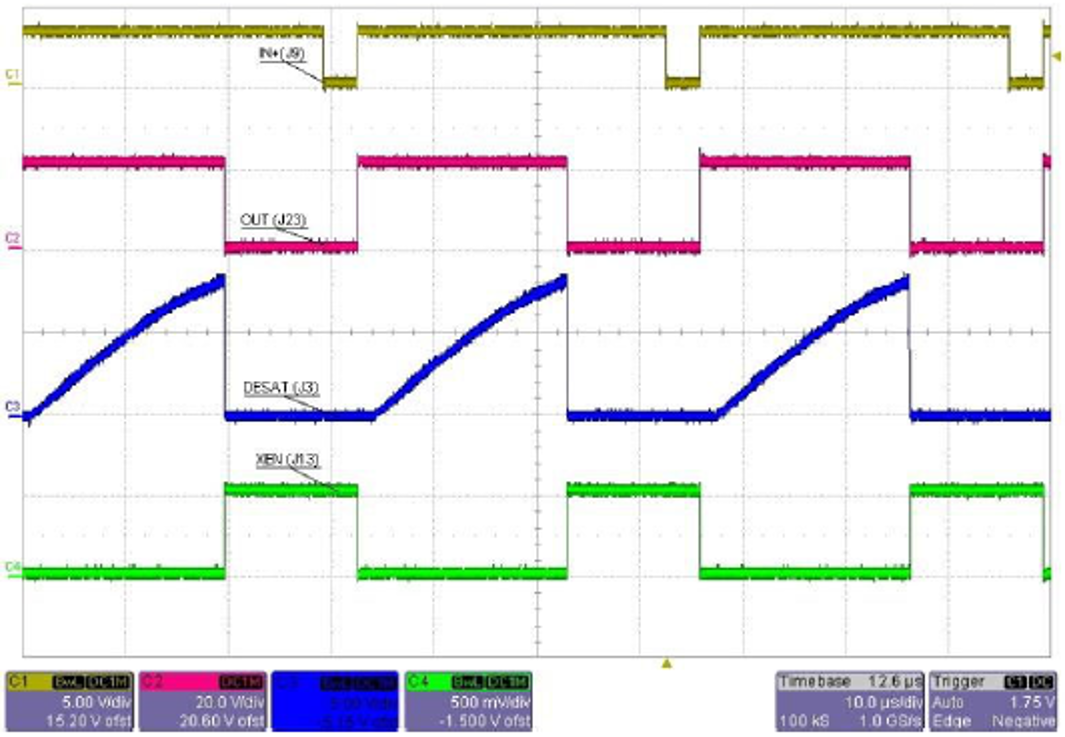

DESAT和XEN波形分別如圖24和圖25所示。由于測(cè)試僅用于IC驗(yàn)證(無(wú)功率器件級(jí)),因此將100pF固定電容連接到DESAT引腳。圖24所示的波形表明DESAT低于7.5V閾值,輸出在正常操作下切換。如果IN+頻率降低(導(dǎo)通時(shí)間增加),則100pF DESAT電容將可以充電至更高的電壓。如圖25所示,DESAT電壓已達(dá)到7.5閾值。輸出后沿在輸入電壓切換為低之前終止。DESAT小斜坡用于強(qiáng)調(diào)終止的OUT脈沖上沒(méi)有出現(xiàn)毛刺的事實(shí)。在開(kāi)關(guān)電源應(yīng)用中,DESAT引腳上可以使用小型(<100pF)外部電容進(jìn)行高頻噪聲濾波。

XEN信號(hào)與OUT信號(hào)相反。無(wú)論驅(qū)動(dòng)器是正常運(yùn)行還是面臨DESAT故障,XEN信號(hào)都能準(zhǔn)確跟蹤任一情況下的反向OUT信號(hào)。

圖24.CH1-IN+、CH2-OUT、CH3-DESAT、CH4-XEN;VDESAT<7.5V

圖25.CH1-IN+、CH2-OUT、CH3-DESAT、CH4-XEN;VDESAT=7.5V

應(yīng)用

SiC MOSFET可以適用于目前使用IGBT的各種應(yīng)用場(chǎng)景。一些較常見(jiàn)的用途包括高壓開(kāi)關(guān)電源、混合動(dòng)力和電動(dòng)汽車(chē)充電器、電氣化鐵路運(yùn)輸、焊機(jī)、激光器、工業(yè)設(shè)備及其他注重高溫操作的環(huán)境。尤其值得一提的兩個(gè)領(lǐng)域是太陽(yáng)能逆變器和高壓數(shù)據(jù)中心。更高的直流電壓有利于減小線(xiàn)規(guī)厚度、接線(xiàn)盒、互連,并最終最大限度地減少導(dǎo)通損耗,從而提高效率。目前,大多數(shù)大型光伏系統(tǒng)均采用1kV直流母線(xiàn),未來(lái)趨向于采用1.5kV總線(xiàn)。同樣,使用380V配電網(wǎng)絡(luò)的數(shù)據(jù)中心可以將直流電壓提升至800V。

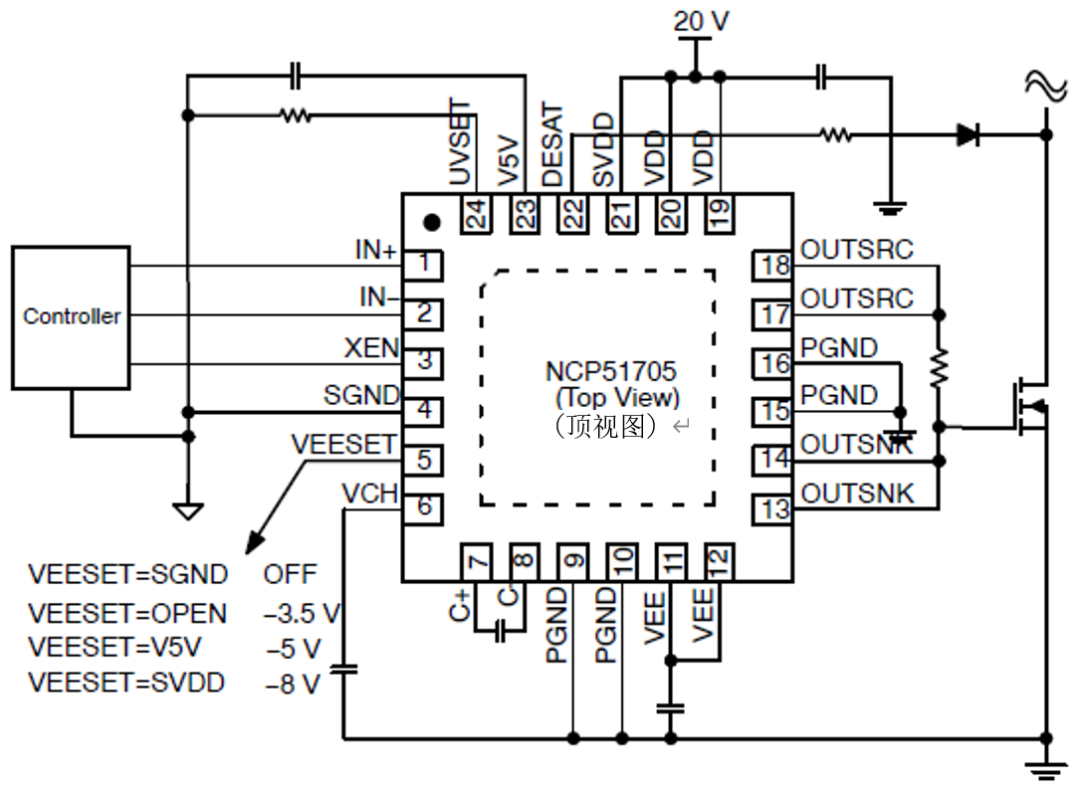

NCP51705的幾個(gè)基本應(yīng)用示例如下所示。

低邊開(kāi)關(guān)圖26顯示了用于低邊開(kāi)關(guān)應(yīng)用的NCP51705的頂層原理圖。未顯示隔離,因此控制器和驅(qū)動(dòng)器之間為直連接口,不是所有應(yīng)用都是非隔離架構(gòu)。此原理圖旨在說(shuō)明,要提供全功能、可靠和穩(wěn)健的SiC柵極驅(qū)動(dòng)電路,只需甚少的外部組件。還應(yīng)提及,盡管只需要單一VDD電壓軌,但其共模瞬態(tài)抗擾度額定值應(yīng)至少為50V/ns,以防止分立式SiC柵極驅(qū)動(dòng)部分中的分立式柵極驅(qū)動(dòng)說(shuō)明所述的雜散電流脈沖。如果 VDD電壓軌由專(zhuān)用輔助電源提供,則應(yīng)特別注意設(shè)計(jì)具有超低原-副邊 雜散電容的變壓器。

圖26.低邊開(kāi)關(guān)示例

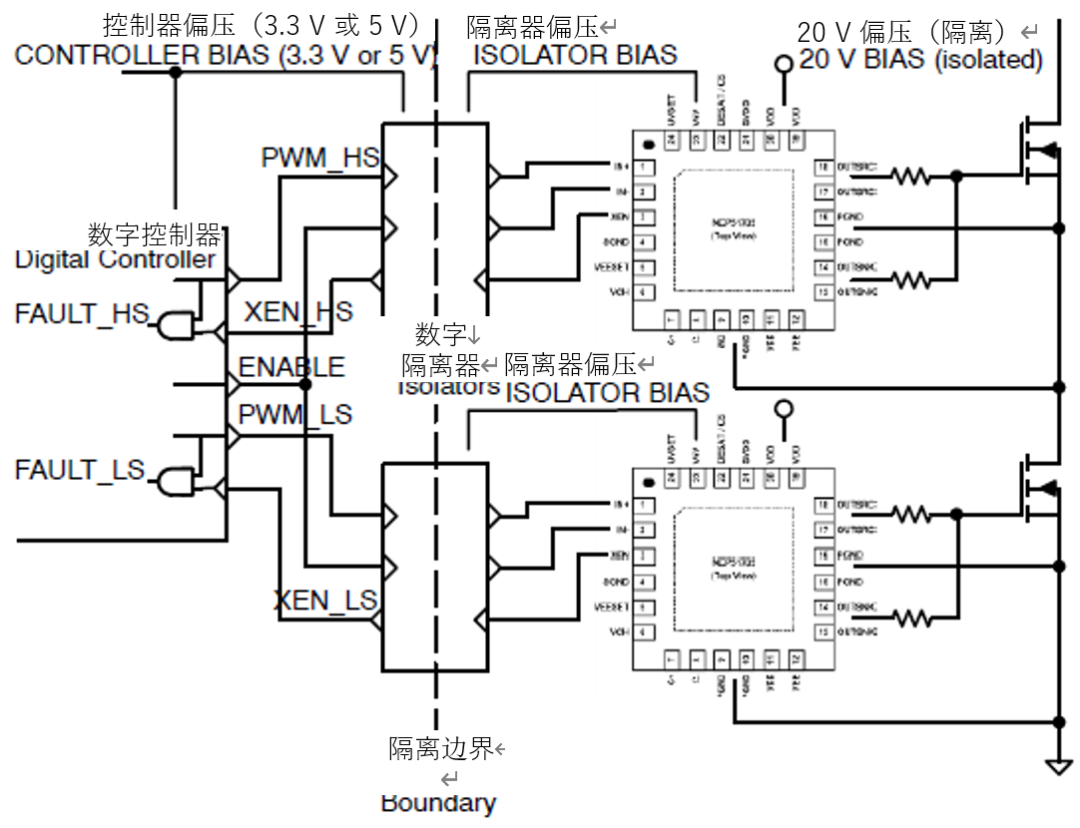

半橋概念

在半橋電源拓?fù)渲锌梢哉业絊iC MOSFET更普遍的用途,如圖27所示。高功率應(yīng)用傾向于在高邊和低邊都使用隔離驅(qū)動(dòng)器。這意味著需要兩個(gè)數(shù)字隔離器。根據(jù)跨越隔離邊界的IO接口的數(shù)量,此類(lèi)應(yīng)用的次級(jí)側(cè)控制可能存在很大爭(zhēng)議。在這個(gè)簡(jiǎn)化示例中,In+和In-(使能)是來(lái)自數(shù)字控制器的僅有的兩個(gè)信號(hào),XEN從NCP51705讀取。XEN可以作為開(kāi)發(fā)柵極驅(qū)動(dòng)時(shí)序、交叉導(dǎo)通預(yù)防、死區(qū)時(shí)間調(diào)整和故障檢測(cè)的時(shí)序信息基準(zhǔn)。此外,溫度感測(cè)、熱管理(風(fēng)扇控制)和更高級(jí)別的故障響應(yīng)也可以由數(shù)字控制器完成。NCP51705的V5V可用于為每個(gè)數(shù)字隔離器的次級(jí)側(cè)供電,如圖27所示。

圖27.半橋概念

準(zhǔn)諧振(QR)反激式

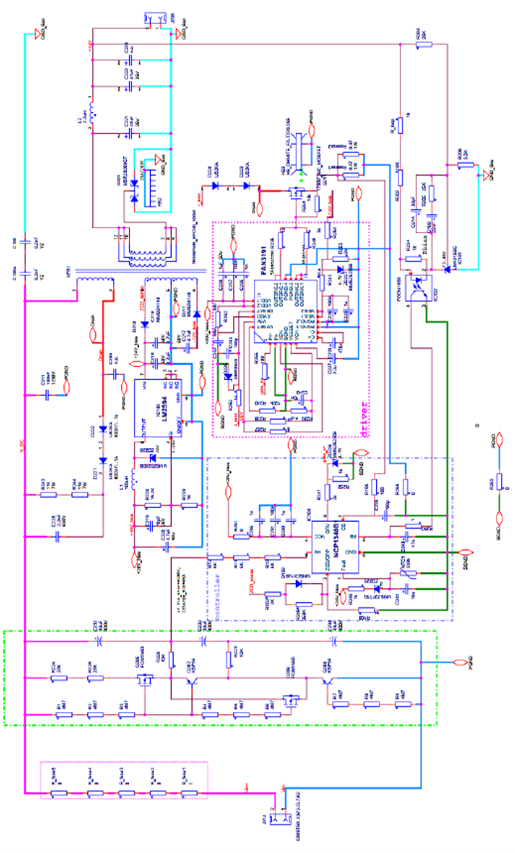

使用NCP1340B1控制器和NCP51705 SiC驅(qū)動(dòng)器設(shè)計(jì)了一個(gè)100W的QR反激式轉(zhuǎn)換器,可在300V

圖28.1000V至24V、100W、400kHz、QR反激式

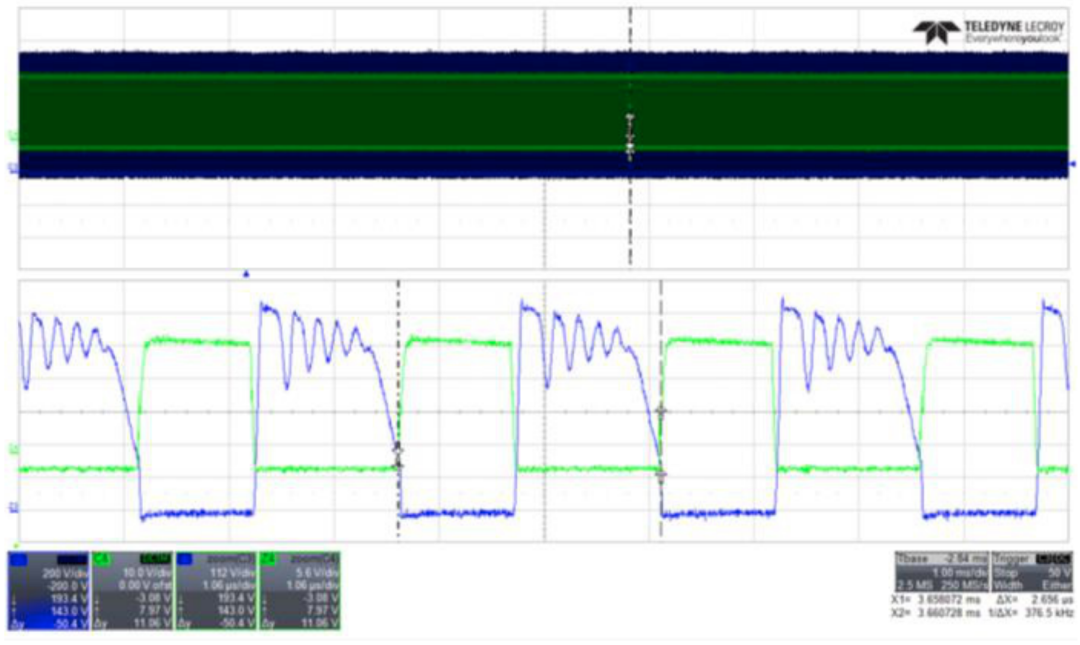

對(duì)于VIN=300V,漏極-源極電壓波形是輸入電壓和反射輸出電壓之和。圖29所示的波形突出顯示了在全占空比操作(VIN=300V)下運(yùn)行的轉(zhuǎn)換器,其中SiC MOSFET的漏極-源極電壓為720V。VDS上升過(guò)渡約為30ns,相當(dāng)于dVDS/dt=24V/ns。NCP1340B1 QR控制在VDS下降沿實(shí)現(xiàn)軟諧振過(guò)渡和谷底開(kāi)關(guān)(在VDS諧振到最小值時(shí)“接近 ZVS”導(dǎo)通),可以在藍(lán)色波形上清晰看到這一操作過(guò)程。由于QR反激式是僅限低邊開(kāi)關(guān)的應(yīng)用,并且dVDS/dt下降沿為諧振,因此SiC MOSFET可能在0V

圖29.CH3=VDS,CH4=VGS;VIN=300V,VOUT=24V,

IOUT=4A,F(xiàn)S=377kHz

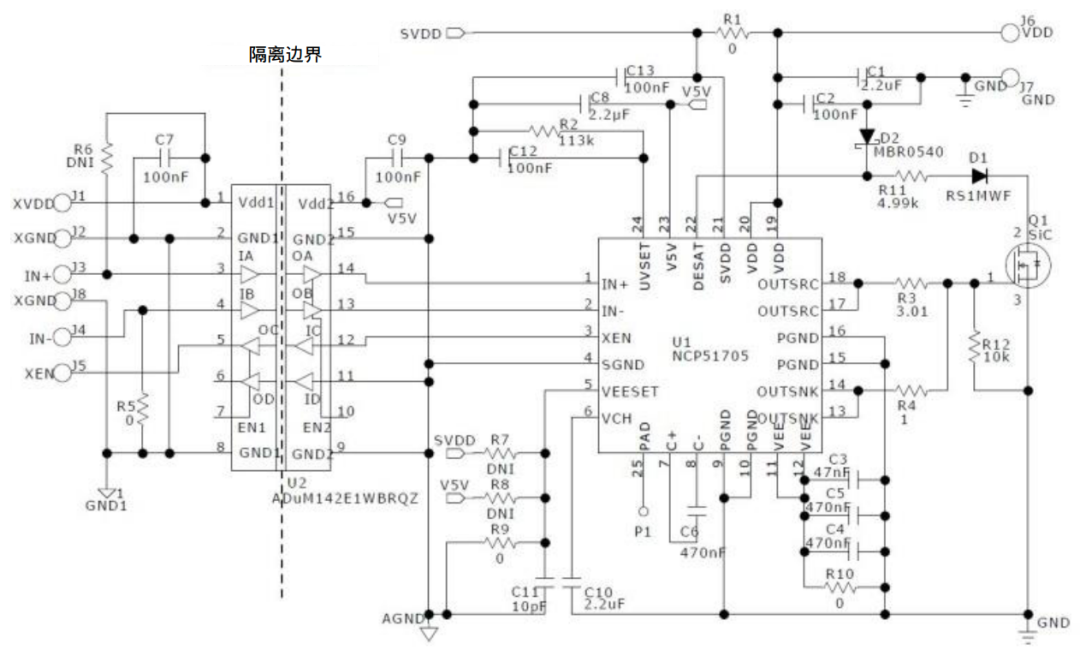

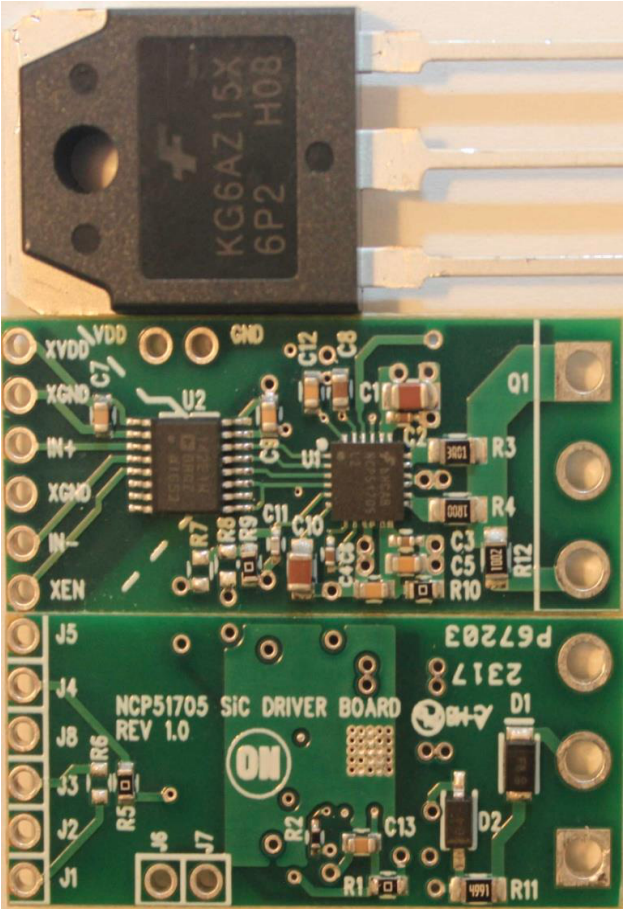

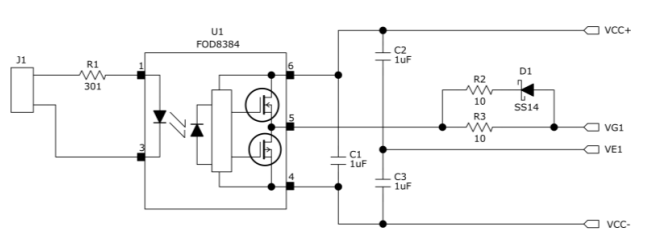

通用NCP51705客戶(hù)EVB通用評(píng)估板(EVB)旨在評(píng)估NCP51705在新設(shè)計(jì)或現(xiàn)有設(shè)計(jì)中的性能。EVB不包括功率級(jí),不專(zhuān)用于任何特定拓?fù)洌纱丝梢?jiàn)它是通用的。它可用于任何低邊或高邊電源開(kāi)關(guān)應(yīng)用。對(duì)于橋接配置,可以用兩個(gè)或者多個(gè)EVB組成圖騰柱結(jié)構(gòu)來(lái)驅(qū)動(dòng)每個(gè)SiC MOSFET。EVB可被視為隔離器+驅(qū)動(dòng)器+TO-247分立模塊。EVB原理圖如圖30所示。

重點(diǎn)是提供一種超緊湊的設(shè)計(jì),其中TO-247 SiC MOSFET的引線(xiàn)可以直接連接到印刷電路板(PCB)。圖31同時(shí)顯示了相鄰TO-247封裝旁邊的EVB的頂視圖和底視圖進(jìn)行尺寸縮放。

圖30.NCP51705 Mini EVB原理圖

圖31.NCP51705 Mini EVB-頂視圖(35mmx15mm)

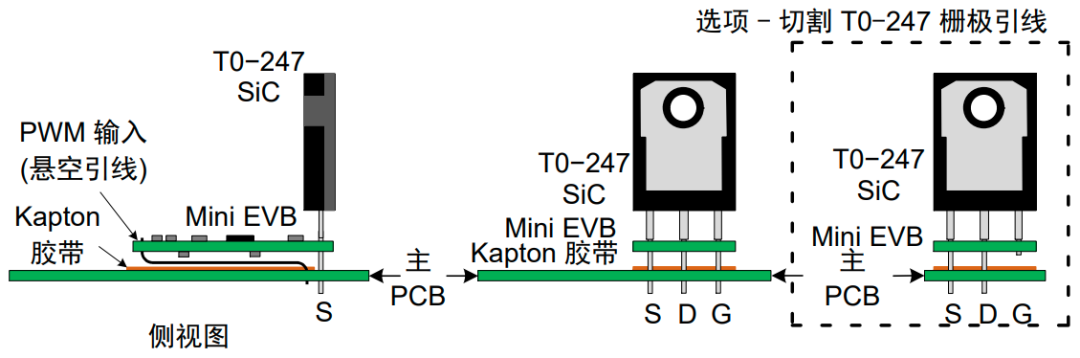

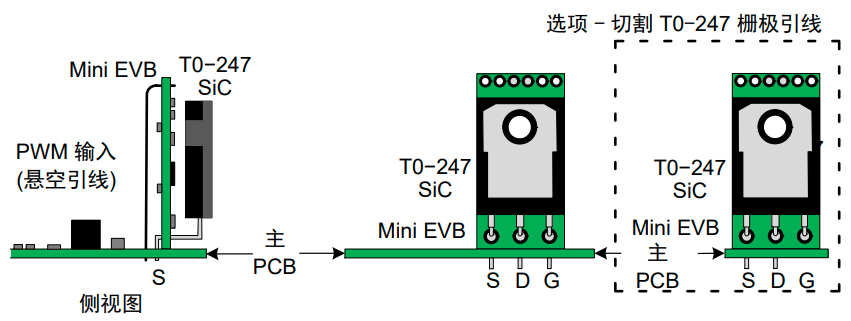

當(dāng)安裝到現(xiàn)有電源設(shè)計(jì)中,并且TO-247前面有可用的PCB區(qū)域時(shí),EVB可以水平安裝到主電源板上,如圖32所示。如果可能,這應(yīng)該是首選的安裝方法。

圖32.水平EVB安裝

如果主電源板上的大型組件妨礙水平安裝,則第二種選擇是垂直安裝EVB,使其與T0-247封裝平行或略微傾斜。由于驅(qū)動(dòng)器與TO-247漏極接頭發(fā)出的高dV/dt非常接近,因此不太傾向于采用這種方式安裝。在任何一種情況下,TO-247封裝的后接頭都保持暴露狀態(tài),如有必要,可將其連接到散熱片上。有關(guān)安裝和操作詳細(xì)信息,請(qǐng)參見(jiàn)EVB用戶(hù)指南。

圖33.垂直EVB安裝

EVB最初配置為接受正輸入邏輯的PWM信號(hào)(連接到GND1的 IN-)。但如果需要,IN-可輕松用作主動(dòng)啟用或重新配置為反相輸入邏輯。驅(qū)動(dòng)器輸出預(yù)配置為0V

參數(shù)性能

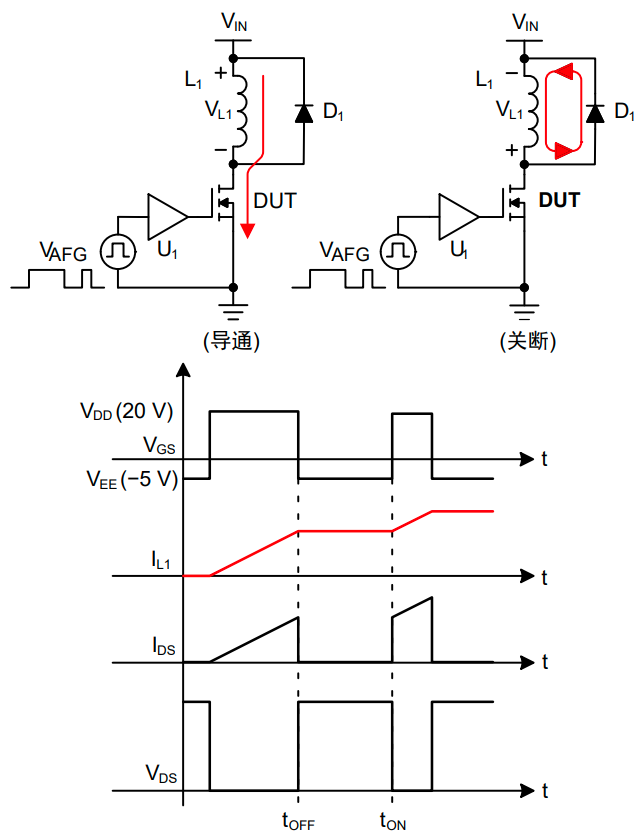

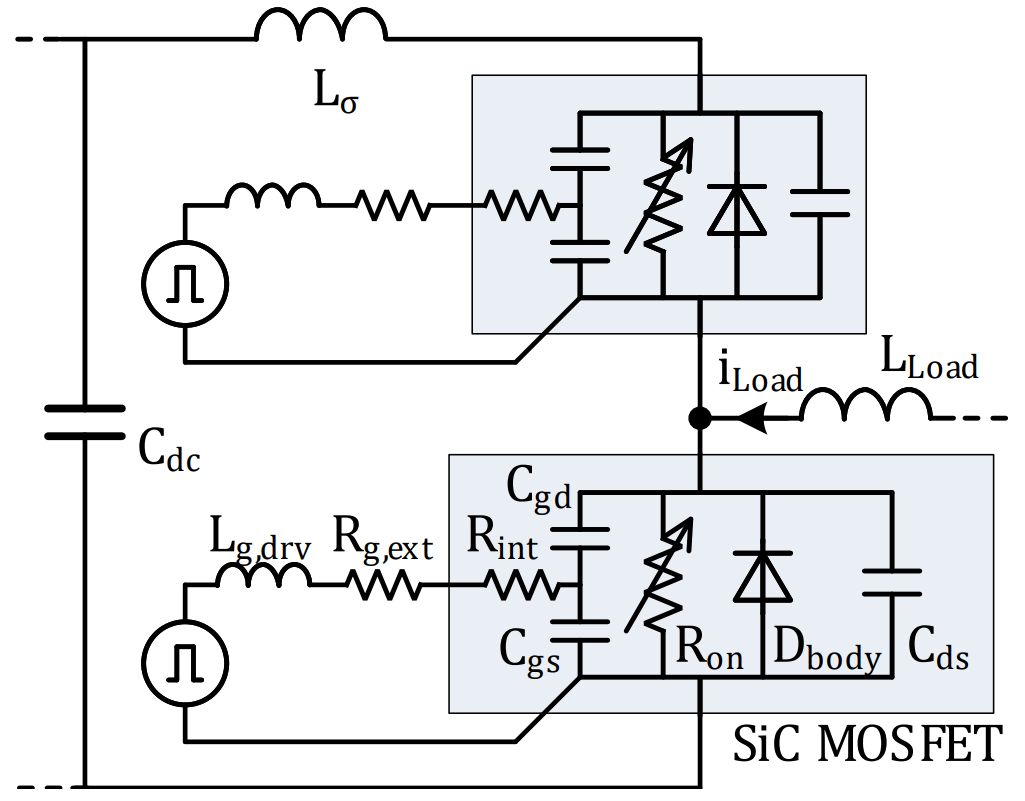

使用眾所周知的雙脈沖測(cè)試平臺(tái)對(duì)MOSFET和IGBT進(jìn)行參數(shù)化表征。雙脈沖測(cè)試方法基本會(huì)向被測(cè)器件(DUT)低邊SiC MOSFET的柵極-源極施加兩個(gè)脈沖。DUT被插入到與圖34所示的鉗位電感開(kāi)關(guān)電路相連的插座中。

圖34.雙脈沖測(cè)試電路和波形

調(diào)整第一個(gè)脈沖的導(dǎo)通時(shí)間,以獲得所需的峰值漏極-源極電流。電感器很大,關(guān)斷時(shí)間足夠短,因此IL1在關(guān)斷續(xù)流期間幾乎保持恒定。因此,第二個(gè)更短的脈沖以相同的漏極-源極電流幅度施加。該測(cè)試方法可精確控制ID和VDS,這是建立動(dòng)態(tài)開(kāi)關(guān)、參數(shù)性能以及對(duì)器件進(jìn)行對(duì)比測(cè)試所必需的。

雙脈沖測(cè)試方法也可用于表征柵極驅(qū)動(dòng)器性能。在SiC、DUT固定的情況下,可以有各種柵極驅(qū)動(dòng)電路組成U1成為新的“DUT”。在圖30和圖31所示的NCP51705 EVB和圖35所示的簡(jiǎn)單光耦合器柵極驅(qū)動(dòng)電路之間,對(duì)dV/dt和dI/dt開(kāi)關(guān)性能進(jìn)行了比較。

圖35.FOD8384 SiC光耦合器柵極驅(qū)動(dòng)電路

FOD8384光耦合器驅(qū)動(dòng)器能夠承受高達(dá)30V的VDD偏壓,因此非常適合-5V

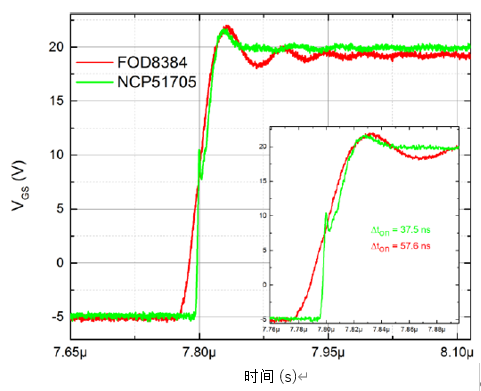

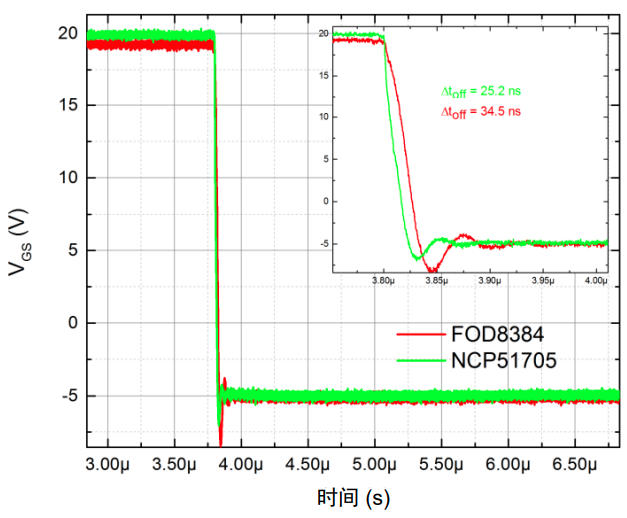

圖36和圖37分別顯示了兩種電路的上升和下降VGS波形,以供比較。兩種電路都使用了1Ω的灌和拉電阻。這些柵極驅(qū)動(dòng)邊緣被顯示為驅(qū)動(dòng)1.2kV的SiC MOSFET,VDS上電壓為600V,流過(guò)ID的電流為30A。NCP51705、VGS上升沿在?5V

圖36.VGS上升沿比較

圖37.VGS下降沿比較

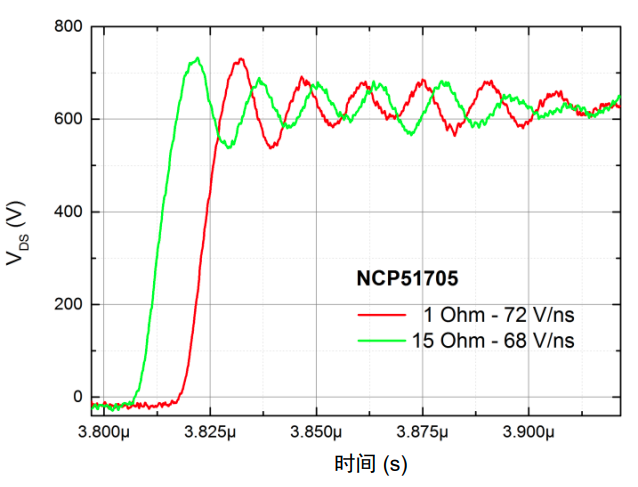

設(shè)計(jì)良好的柵極驅(qū)動(dòng)器IC包括低源極和漏極阻抗,使得SiC MOSFET漏極可以由柵極精確控制。其次,最大限度地降低驅(qū)動(dòng)器輸出阻抗對(duì)于允許SiC MOSFET達(dá)到最高自然dV/dt至關(guān)重要。SiC MOSFET的自然dV/dt限值與RLO+RGATE+RGI成反比。當(dāng)RLO高于必要值時(shí),SiC MOSFET的自然dV/dt限值降低。這使得器件更容易受到dV/dt引起的導(dǎo)通的影響,并限制了通過(guò)選擇RGATE可以實(shí)現(xiàn)的dVDS/dt控制量。圖38所示的NCP51705 VDS波形揭示了改變RGATE即可實(shí)現(xiàn)的高度dVDS/dt控制。對(duì)于RGATE=1Ω,dVDS/dt=72V/ns。將RGATE從1Ω增加到15Ω會(huì)使dVDS/dt從72V/ns降低到68V/ns。這表明,如果需要,可以使用高得多的RGATE來(lái)逐步降低dVDS/dt。

圖38.NCP51705 VDS上升沿,可變柵極電阻

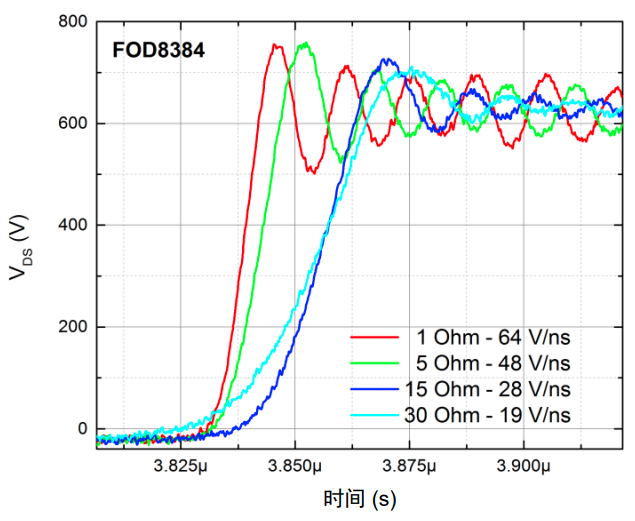

使用FOD8384光耦合器柵極驅(qū)動(dòng)器完成了相同的實(shí)驗(yàn)。從圖39所示的波形中發(fā)現(xiàn),RGATE從1Ω變成15Ω導(dǎo)致dVDS/dt速率變化超過(guò)2:1。由于FOD8384驅(qū)動(dòng)器輸出阻抗更高,dVDS/dt控制更受RGATE較小變化的影響。此外請(qǐng)注意,NCP51705的dVDS/dt上升相對(duì)而言更為線(xiàn)性。

圖39.FOD8384 VDS上升沿,可變柵極電阻

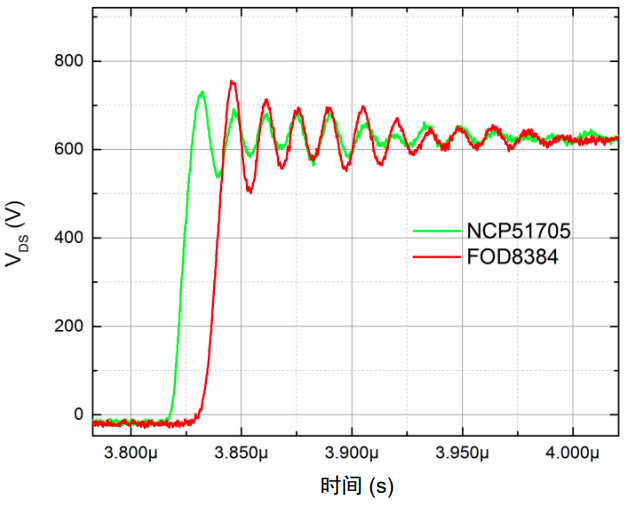

圖40所示的波形比較了在RGATE=1Ω的情況下,從?5V

圖40.VDS上升沿比較,1Ω柵極電阻

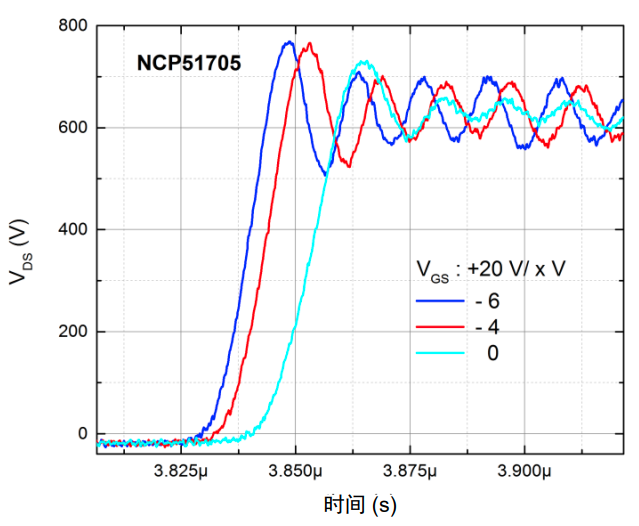

NCP51705實(shí)現(xiàn)dVDS/dt控制的另一種方式是通過(guò)改變VEE的負(fù)振幅電平。這可以通過(guò)根據(jù)表3配置VEESET引腳或使用施加到VEE的外部負(fù) DC 電源來(lái)實(shí)現(xiàn)。圖 41 中的波形顯示了當(dāng)VEE在?6V

圖41.NCP51705 VDS上升沿,可變VEE

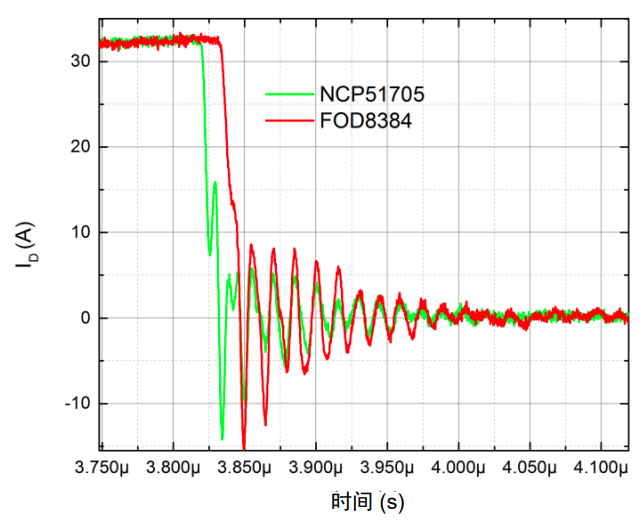

圖42所示的漏極電流測(cè)量是使用Pearson電流探頭進(jìn)行的。NCP51705電流在dID/dt=3.2A/ns時(shí)下降,但與FOD8384驅(qū)動(dòng)電路相比,表現(xiàn)出的振鈴較少。NCP51705更快的dID/dt與圖37所示的VGS下降沿波形密切相關(guān)。

圖42.ID下降沿比較

雙脈沖測(cè)試方法是傳統(tǒng)上用于表征分立功率半導(dǎo)體器件的動(dòng)態(tài)開(kāi)關(guān)性能的測(cè)試程序。由于在導(dǎo)通和關(guān)斷期間可以精確控制施加的VDS和初始ID,該測(cè)量技術(shù)已被證明是表征箝位電感開(kāi)關(guān)應(yīng)用電路中柵極驅(qū)動(dòng)器IC性能的可靠方法。

結(jié)論

本文重點(diǎn)介紹了在設(shè)計(jì)高性能柵極驅(qū)動(dòng)電路時(shí)必須考慮的SiC MOSFET的一些特性。對(duì)于柵極驅(qū)動(dòng)來(lái)說(shuō),與SiC MOSFET相關(guān)的低gm或不那么大的跨導(dǎo) 特性尤其棘手。通用低邊柵極驅(qū)動(dòng)器經(jīng)常被使用,但缺乏高效可靠地驅(qū)動(dòng)SiC MOSFET的必要功能。SiC MOSFET 在市場(chǎng)中的廣泛采用在某種程度上與其易用性有關(guān)。NCP51705為設(shè)計(jì)人員提供了一種簡(jiǎn)單、高性能、高速的解決方案,用于高效可靠地驅(qū)動(dòng)SiC MOSFET。

點(diǎn)個(gè)星標(biāo),茫茫人海也能一眼看到我

原文標(biāo)題:SiC MOSFET的封裝、系統(tǒng)性能和應(yīng)用

文章出處:【微信公眾號(hào):安森美】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

安森美

+關(guān)注

關(guān)注

32文章

1648瀏覽量

91937

原文標(biāo)題:SiC MOSFET的封裝、系統(tǒng)性能和應(yīng)用

文章出處:【微信號(hào):onsemi-china,微信公眾號(hào):安森美】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SiC MOSFET模塊封裝技術(shù)及驅(qū)動(dòng)設(shè)計(jì)

SiC MOSFET和SiC SBD的區(qū)別

SemiQ 1200V SiC MOSFET Module說(shuō)明介紹

碳化硅模塊(SiC模塊/MODULE)大電流下的驅(qū)動(dòng)器研究

如何更好地驅(qū)動(dòng)SiC MOSFET器件?

基于NX封裝的低雜感SiC MOSFET模塊設(shè)計(jì)

溝槽當(dāng)?shù)溃矫嫘?b class='flag-5'>SiC MOSFET尚能飯否?

SIC MOSFET在電路中的作用是什么?

怎么提高SIC MOSFET的動(dòng)態(tài)響應(yīng)?

SIC MOSFET對(duì)驅(qū)動(dòng)電路的基本要求

半導(dǎo)體王炸——碳化硅(SiC)全球市場(chǎng)規(guī)模究竟有多大? #SiC銀燒結(jié)設(shè)備 #SiC封裝設(shè)備 #ZR電機(jī)

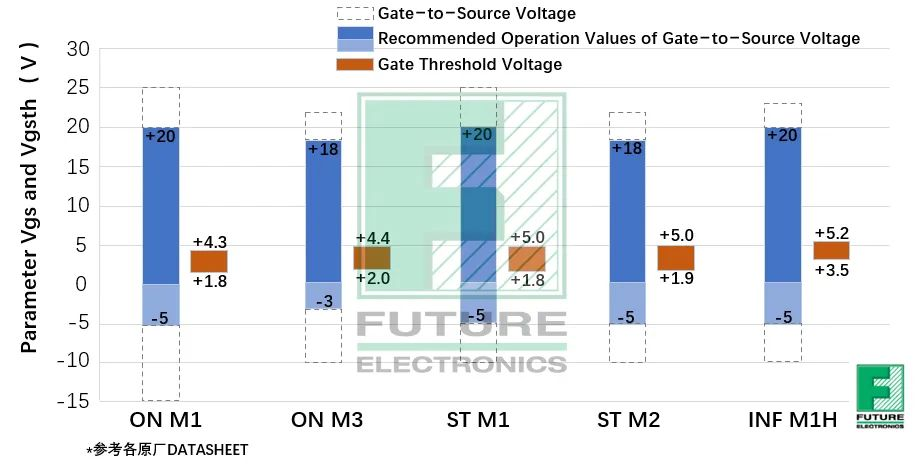

SiC設(shè)計(jì)干貨分享(一):SiC MOSFET驅(qū)動(dòng)電壓的分析及探討

噪聲如何影響高速信號(hào)鏈的總動(dòng)態(tài)系統(tǒng)性能

SiC MOSFET的封裝、系統(tǒng)性能和應(yīng)用

SiC MOSFET的封裝、系統(tǒng)性能和應(yīng)用

評(píng)論