針對DFX設(shè)計(jì),Vivado提供了命令report_pr_configuration_analysis,該命令會(huì)從設(shè)計(jì)復(fù)雜度、時(shí)鐘和時(shí)序等方面對其進(jìn)行分析。使用該命令時(shí),我們主要會(huì)用到其中3個(gè)選項(xiàng):-complexity、-clocking和-timing。

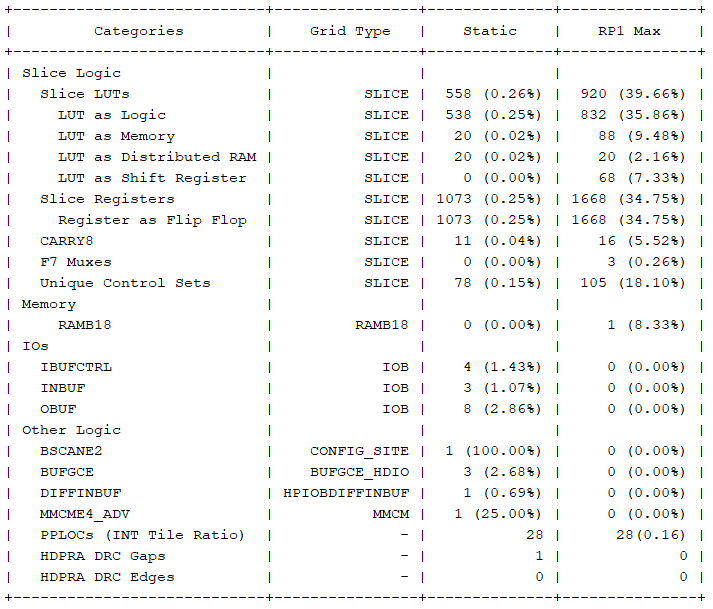

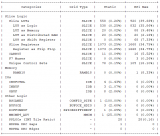

選項(xiàng)-complexity聚焦在設(shè)計(jì)的資源使用情況,會(huì)給出指定RP下各RM的資源使用情況,同時(shí)給出各RM之間相比各種資源使用量的最大值,這需要用到選項(xiàng)-cells和-dcps。其中-cells指定RP的名字,而-dcps則會(huì)列出各RM所在的dcp文件。如下圖所示,Static列顯示了靜態(tài)區(qū)的資源利用情況,RP1 Max給出了RP1各RM相比各種資源使用量的最大值。這一點(diǎn)可從報(bào)告的第二部分進(jìn)行驗(yàn)證。報(bào)告的第二部分是對各RM資源利用情況的比較。

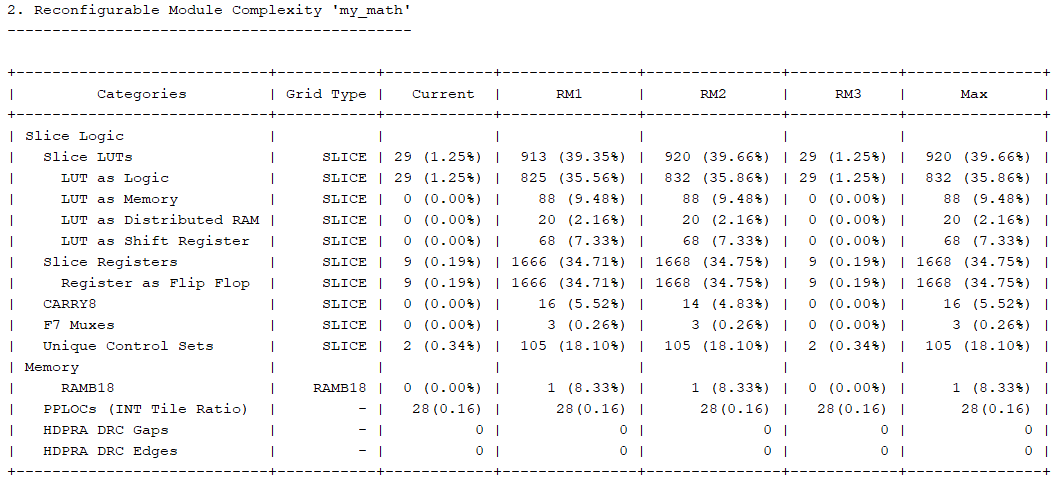

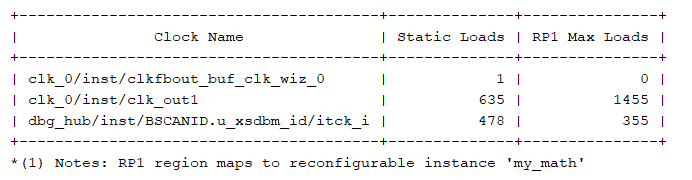

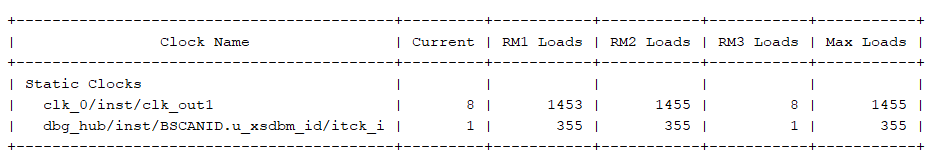

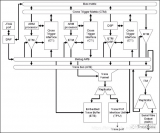

選項(xiàng)-clocking聚焦在時(shí)鐘的使用情況上。會(huì)給出各時(shí)鐘在靜態(tài)區(qū)和每個(gè)RM的負(fù)載個(gè)數(shù),如下圖所示。

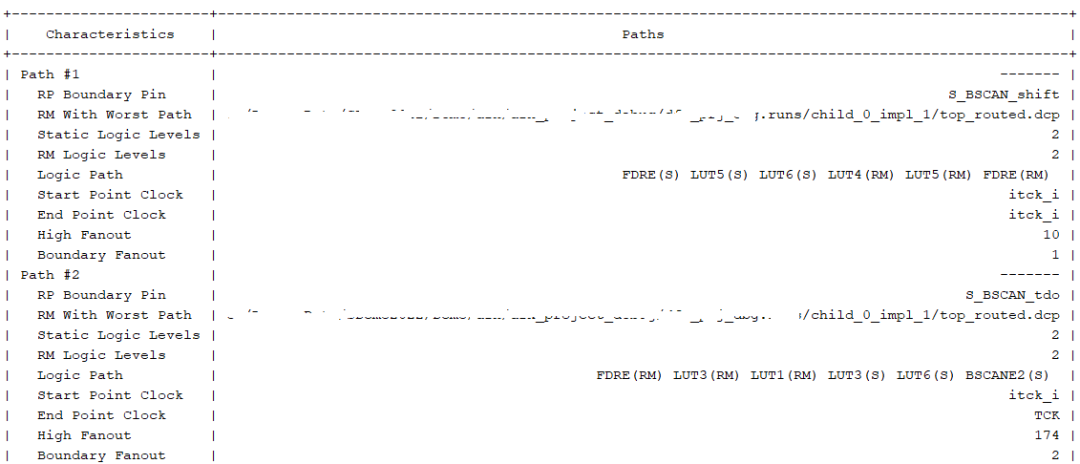

選項(xiàng)-timing聚焦在時(shí)序上,給出各RM和靜態(tài)區(qū)接口關(guān)鍵路徑時(shí)序,如下圖所示。

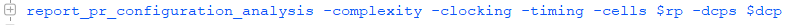

為了對各RM進(jìn)行比較,使用report_pr_configuration_analysis時(shí),要添加選項(xiàng)-cells和-dcps。由于該命令會(huì)逐次打開所有指定的dcp文件,所以會(huì)比較耗時(shí),為此,確保每打開一個(gè)dcp,所要分析的條目全部執(zhí)行。這里給出該命令的最佳使用方式,如下圖所示,即同時(shí)添加-complexity、-clocking和-timing這3個(gè)選項(xiàng)。

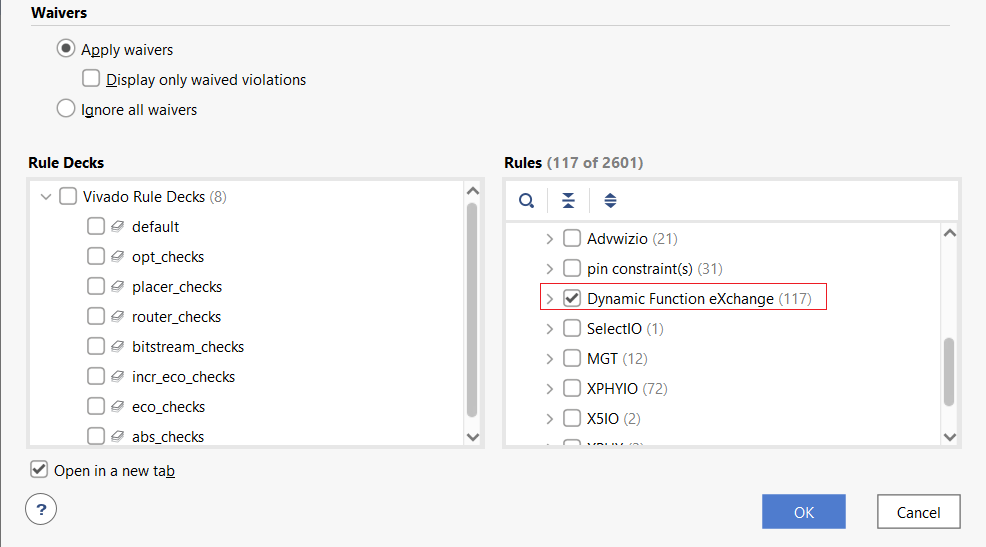

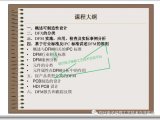

我們還可以用report_drc對DFX設(shè)計(jì)進(jìn)行分析,如下圖所示,點(diǎn)擊Vivado左側(cè)導(dǎo)航欄的Report DRC后會(huì)彈出如下圖所示界面,確定勾選DFX。建議在綜合之后執(zhí)行該命令,這樣可以盡早發(fā)現(xiàn)設(shè)計(jì)存在的問題。

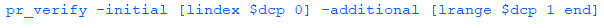

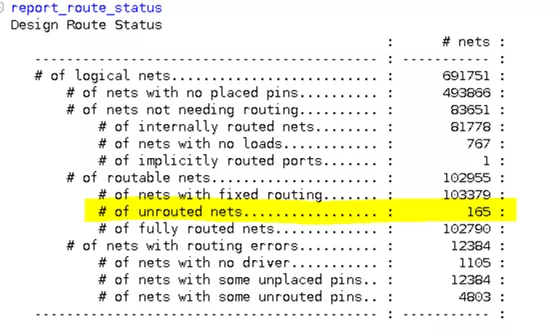

對于DFX設(shè)計(jì),所有configuration的靜態(tài)區(qū)應(yīng)該是完全一致的,因?yàn)镻arent Run一旦執(zhí)行完畢,工具就會(huì)在布線層面鎖定靜態(tài)區(qū)供后續(xù)childrun使用。我們可借助命令pr_verify來驗(yàn)證各configuration對應(yīng)的靜態(tài)區(qū)是完全一致的,具體命令如下:

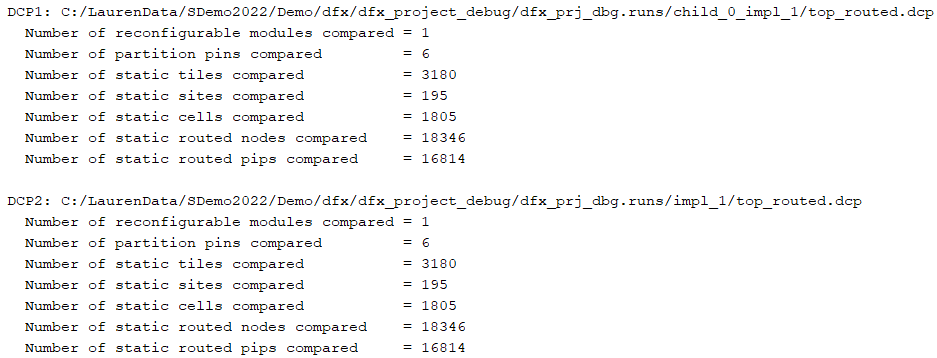

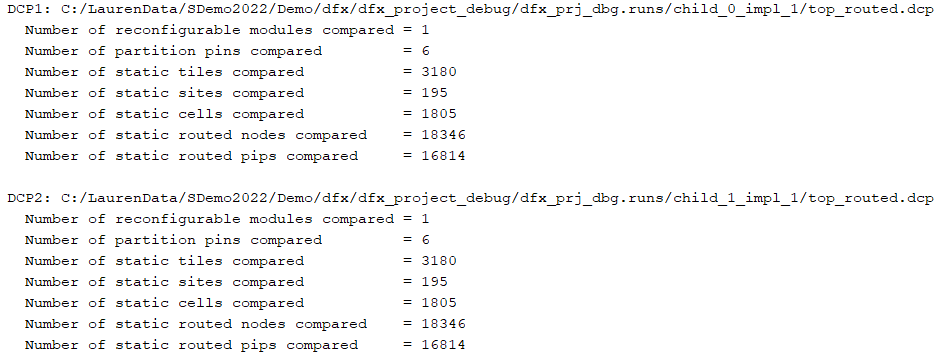

該命令生成報(bào)告如下:

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602043 -

命令

+關(guān)注

關(guān)注

5文章

678瀏覽量

21987 -

時(shí)序

+關(guān)注

關(guān)注

5文章

386瀏覽量

37290 -

dfx設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

6瀏覽量

92

原文標(biāo)題:DFX設(shè)計(jì)如何分析

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何對傳統(tǒng)的非DFX設(shè)計(jì)進(jìn)行調(diào)試呢?

什么是DFX技術(shù)?DFX設(shè)計(jì)一定要執(zhí)行設(shè)計(jì)規(guī)則檢查嗎?

采用UltraScale/UltraScale+芯片的DFX設(shè)計(jì)注意事項(xiàng)

招兼職dfx、dfm培訓(xùn)講師

硬件電路設(shè)計(jì)中常見的DFX

簡述DFX理念與產(chǎn)品研發(fā)(一)

簡要分析DFX實(shí)施流程

HarmonyOS對DFX能力的要求

DFX設(shè)計(jì)無法連貫布線的根本原因及修護(hù)

物聯(lián)網(wǎng)系統(tǒng)設(shè)計(jì)如何發(fā)揮作用

DFX設(shè)計(jì)如何分析

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

DFX設(shè)計(jì)如何分析

DFX設(shè)計(jì)如何分析

評論