前言

數字IC設計中為什么要避免鎖存器(Latches)?

上學時,老師說判斷語句要把條件寫全, 不然會生成鎖存器,做項目時又說多比特寄存器信號的賦值一定要加if條件,不讓出現else的賦值 。就很矛盾,本文主要講下什么是鎖存器,什么情況下會出現鎖存器,以及鎖存器的危害。

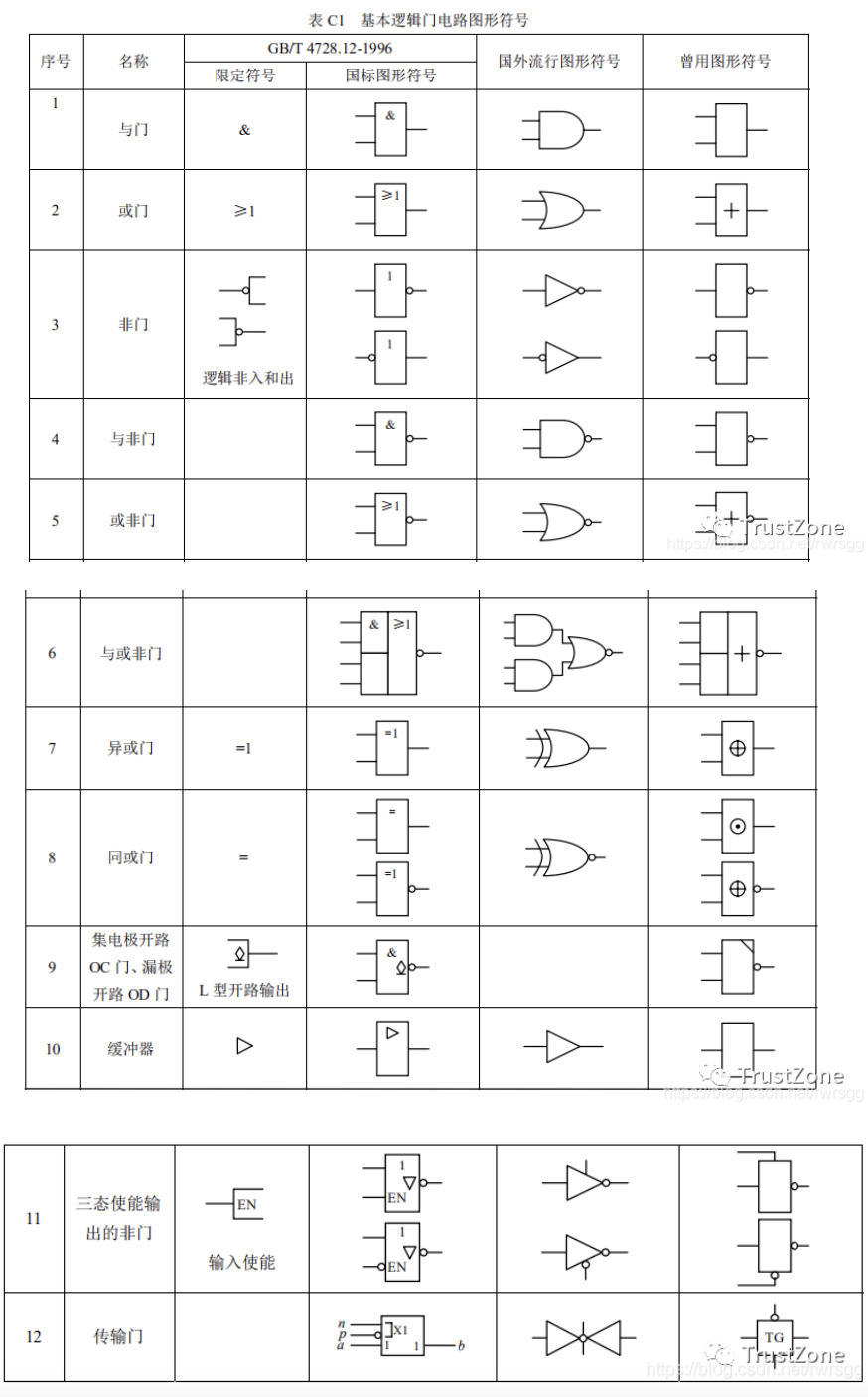

基本邏輯門電路圖形符號

零、鎖存器,D觸發器和寄存器的關系與區別

前言

數字IC設計里,常會出現鎖存器,D觸發器和寄存器,很多人(比如我)老傻傻分不清,搞不懂他們的區別是什么。這篇博客主要解釋鎖存器,D觸發器和寄存器的工作原理以及他們的關系和區別。

一、鎖存器

鎖存器(Latch)是一種對脈沖電平敏感的存儲單元電路,它們可以在特定輸入脈沖電平作用下改變狀態【1】。換句話說,如果一個模塊的只有在特定電平的作用下,才會將輸入信息更新到他的輸出引腳,否則該模塊的輸出將保持不變,那么這個模塊就可以被看成是一個鎖存器。

舉個例子:

二、鎖存器構建D觸發器

如圖是一個D觸發器的示意圖,當CLK輸入一個上升沿時,D端的輸入被傳輸到Q。而CLK未輸入上升沿時,Q保持不變。

如圖所示,當CLK = 0時,Q1=D;當CLK=1時,Q=Q1;也就是說,當CLK上升沿來臨時,D信號被傳輸到Q端,因此這兩個鎖存器組成了一個D觸發器;

三、什么是寄存器?

寄存器,是集成電路中非常重要的一種存儲單元,通常由觸發器組成 , 寄存器是有限存貯容量的高速存貯部件 ,它們可用來暫存指令、數據和地址【2】。也就是說, 擁有緩存數據功能的,都可以被稱為寄存器 ,而寄存器常被用于CPU中,因此屬于邊沿信號敏感器件。

D觸發器具有緩存數據的功能 ,當CLK輸入上升沿時,D被傳輸到Q,之后Q將在CLK下一個上升沿到來前保持不變。因此D觸發器可以作為寄存器使用,即(D觸發器∈寄存器),鎖存器狀態的變化和特定電平有關(高電平和低電平),而寄存器的狀態變化往往需要邊沿信號(上升沿和下降沿),因此鎖存器notin寄存器,由于兩個鎖存器可以構建一個邊沿信號敏感的觸發器(如上節所示),因此鎖存器可以搭建寄存器。

四、總結

- 鎖存器為電平敏感器件,而D觸發器和寄存器為邊沿信號敏感器件;

- 兩個鎖存器可以搭建一個D觸發器;

- D觸發器屬于寄存器;

一、什么是鎖存器?

鎖存器(Latch)是一種對脈沖電平敏感的存儲單元電路 ,它們可以在特定輸入脈沖電平作用下改變狀態【1】。

換句話說, 如果一個模塊的只有在特定電平的作用下,才會將輸入信息更新到他的輸出引腳 ,否則該模塊的輸出將保持不變,那么這個模塊就可以被看成是一個鎖存器。

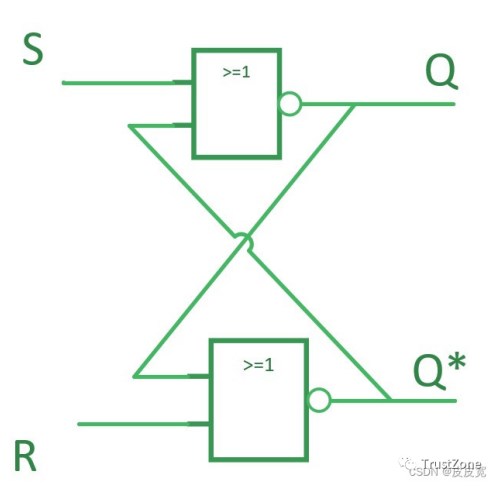

常見的S-R寄存器的結構如下所示:

真值表為

由于S,R為00時,可以使輸出Q保持不變,從而達到用組合邏輯來實現存儲的目的;

二、什么情況下會出現鎖存器?

時序邏輯由于寄存器的存在 ,因此不需要鎖存器來存儲數據; 而組合邏輯的條件未給全時則會出現鎖存器 ;

always@(*) if(vld) a = b;

這時由于沒有寫vld為0的情況,因此不會例化成二選一的選擇器,而是會例化出鎖存器,達到當vld為0時,保持數據不變的存儲功能;

三、為什么要避免出現鎖存器?

鎖存器有以下缺點:

- 不能異步復位,在上電后處于不確定的狀態。

- 鎖存器會使靜態時序分析變得非常復雜;

- 如果是FPGA上的搭建電路的話,由于FPGA中基本的單元是由查找表和觸發器組成的,若生成鎖存器反而需要更多的資源;

- 鎖存器對毛刺敏感,會造成電路的不穩定

例化成選擇器就能解決這個問題嗎?

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828 -

IC設計

+關注

關注

37文章

1291瀏覽量

103763 -

鎖存器

+關注

關注

8文章

904瀏覽量

41444 -

D觸發器

+關注

關注

3文章

164瀏覽量

47862 -

CLK

+關注

關注

0文章

127瀏覽量

17125

發布評論請先 登錄

相關推薦

數字IC設計中為什么要避免鎖存器呢?

數字IC設計中為什么要避免鎖存器呢?

評論