作為一個資深的FPGA工作者,相信大家對于IBIS模型并不陌生;IBIS模型在進行系統設計時節省時間和降低成本是很關鍵的。在原型制作之前,系統設計人員可以用模型來進行設計仿真。在高速系統設計中正是如此,進行信號完整性仿真來分析不同條件下傳輸線中的電路行為,在設計初期就能預防并檢測出典型的問題,例如過沖、欠沖、阻抗不匹配、串擾、地彈等。然而,可用的數字IC模型非常少。

當半導體廠商被索要SPICE模型時,他們并不愿意提供,因為這些模型會包含有專有工藝和電路信息。這個問題已經通過采用IBIS模型來(輸入/輸出緩沖器信息規范)解決。IBIS是一個行為模型,通過V/I和V/T數據,描述器件數字輸入和輸出的電氣特性,而不會泄露任何元器件專有的信息。

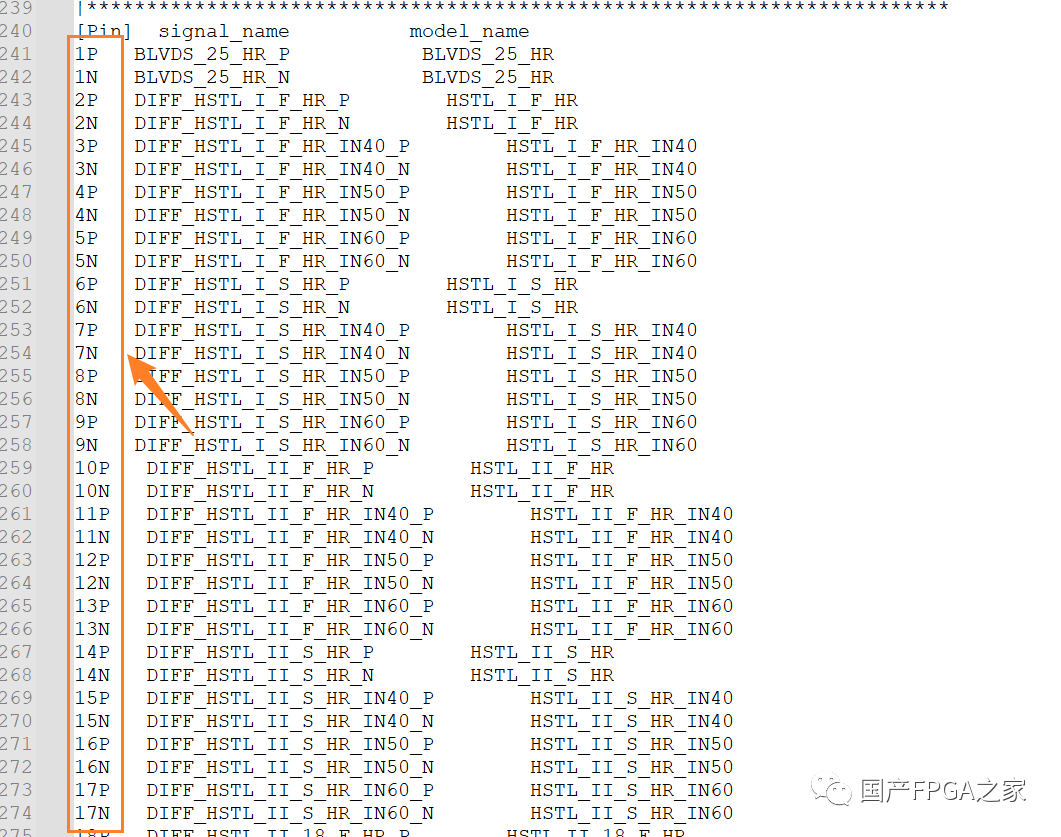

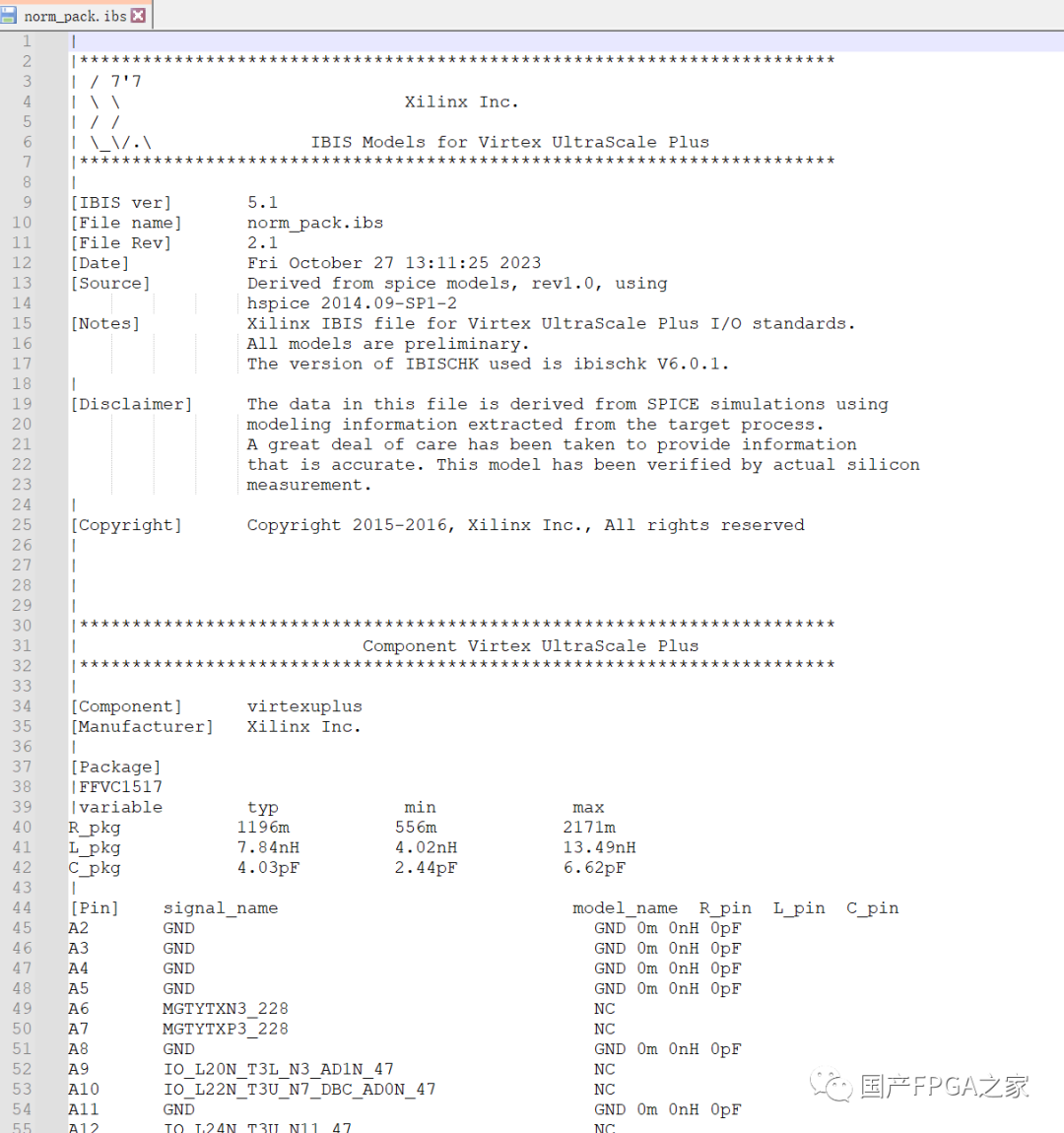

FPGA器件作為高靈活度器件,其管腳屬性可以根據用戶需求自行設定。FPGA廠商提供一般提供通用IBIS模型,通用IBIS模型文件包含所選系列支持的所有IO標準的模型,模型與具體的芯片封裝以及die的尺寸無關,通常這類模型為每個可用的IO設置一個全局RLC參數。在進行少數幾個信號的原理圖級仿真中,該類IBIS模型是滿足需求的,但是在更進一步的PCB仿真中,需要導出自定義的IBIS模型庫。 然而在通用IBIS模型中,管腳不是實際封裝使用管腳,無法直接使用。

今天我們主要來介紹基于Vivado如何導出FPGA的IBIS文件。

1 IBIS文件生成方法 定義管腳的IBIS文件生成有兩種方法。 1)在通用IBIS文件基礎上進行編輯。該方法需要一定的IBIS語法基礎,需要更新IBIS文件中[Package]、[Pin]、[Diff Pin]、[Model Selector]字段內容。具體操作方法大家可以參考下面博文內容。

Xilinx FPGA IBIS 模型的使用問題,總結+分析都在這里了~ (qq.com)

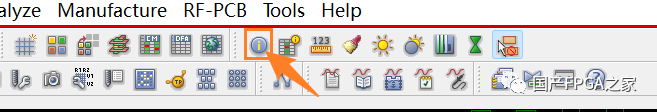

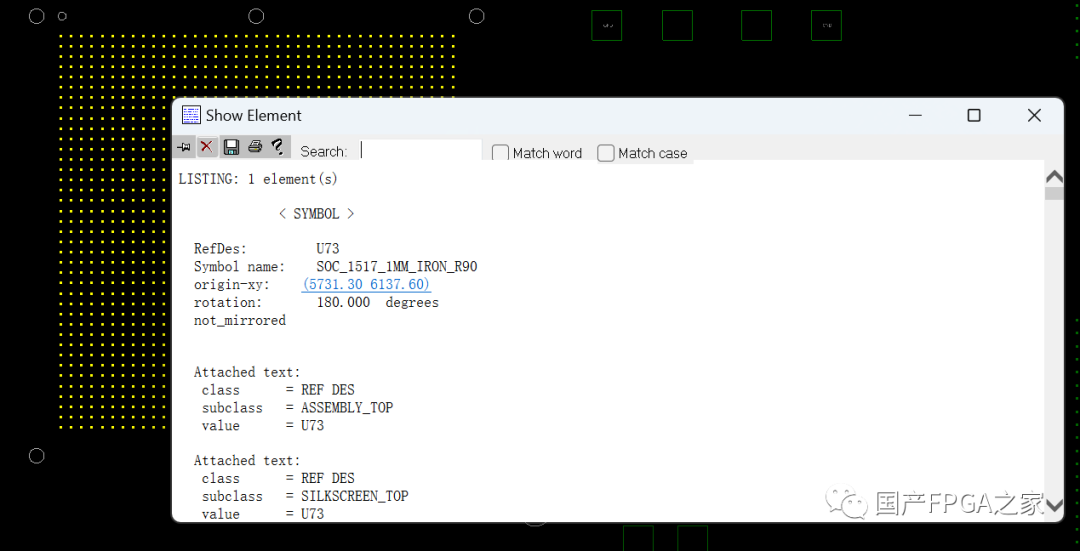

2)通過廠商提供軟件自動生成。本篇主要介紹通過vivado 自動生成IBIS軟件過程。該方法需要根據管腳與網絡映射關系編寫XDC文件,涉及4種語法約束。個人感覺更適宜仿真環境快速搭建,此外軟件中有DRC分析工具,可以幫助檢查芯片原理圖設計缺陷。 2 Allegro導出管腳映射關系 本操作從PCB文件中獲得FPGA的管腳映射關系。 打開已經導入網表的brd文件,在快捷欄中點擊Show Element 快捷鍵。

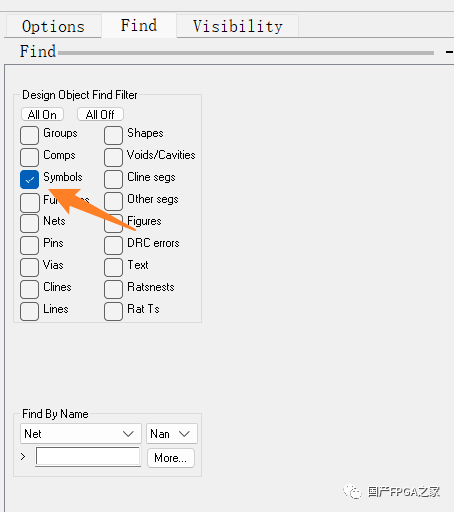

在find 菜單欄中僅勾選Symbols

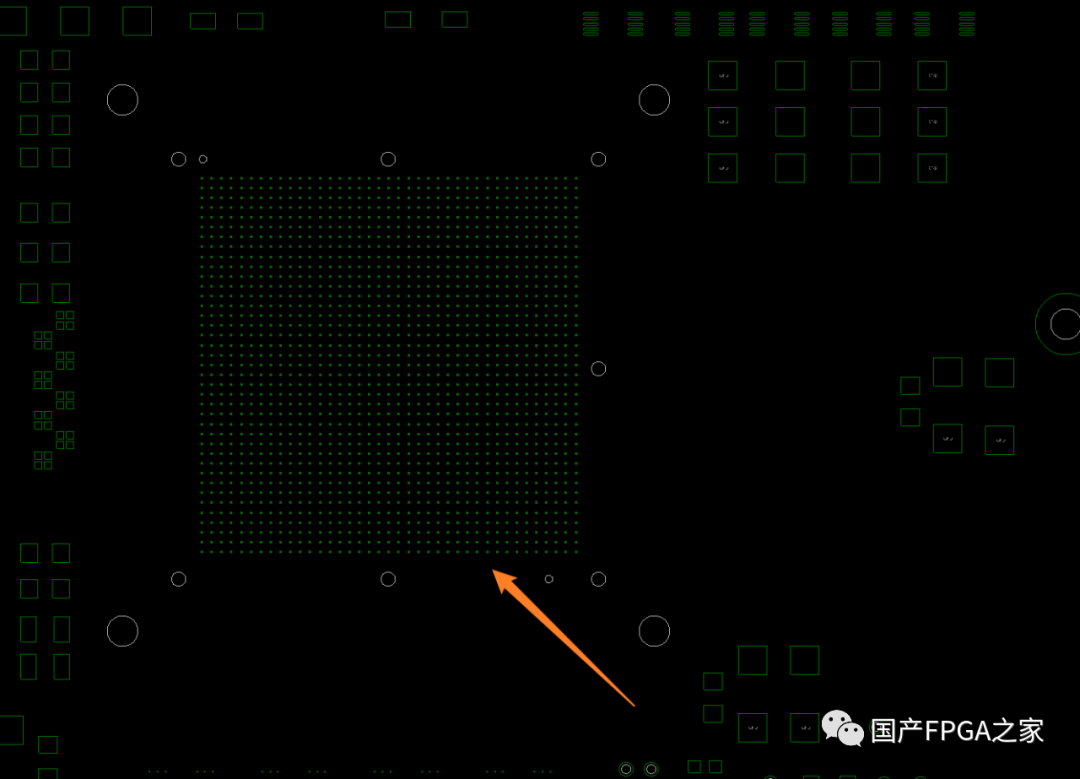

點擊PCB 中的FPGA Symbol

將會彈出fpga元件相關信息,其中包含我們需要的管腳與net的映射關系。

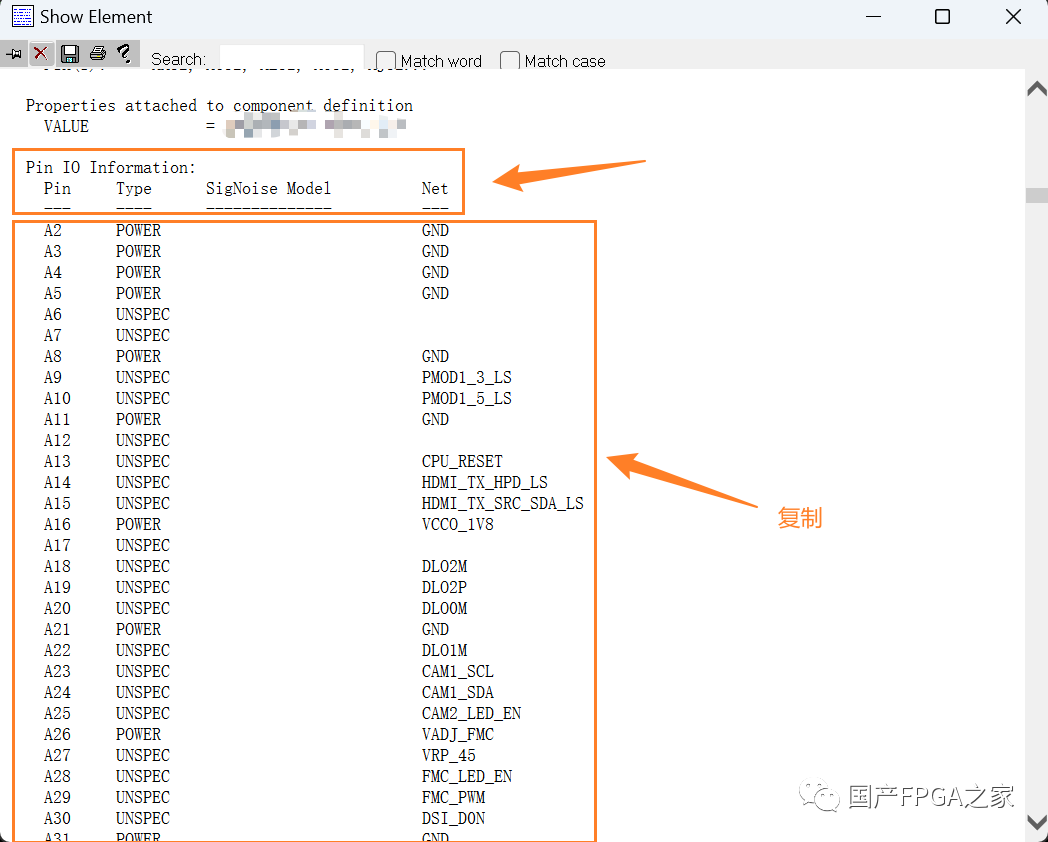

在彈窗中找到 Pin IO information的表格,表格文本信息即是我們需要的PIN與net映射關系,復制到管腳信息到外部txt。

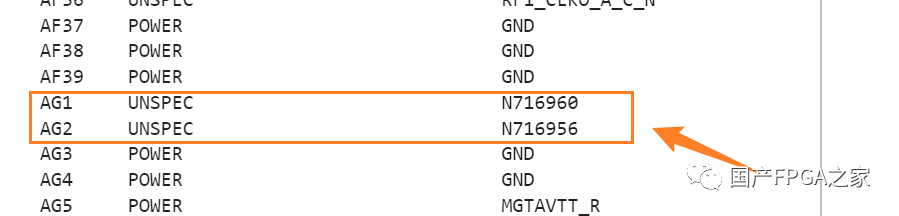

本節導出器件管腳與網絡映射關系,需要注意的是如果fpga與外部連接網絡沒有命名,軟件將自動分配網絡名。這部分管腳名稱,沒有實際意義不便理解,可根據需求手動修改。

3 管腳約束/XDC文件生成

本節內容通過上節得到1對差分信號和一個單端信號為例說明編輯過程。

編寫約束文件僅需要了解四種固定格式即可。 1、設置管腳到網絡映射關系。具體語法格式如下:

set_property PACKAGE_PIN PIN [get_ports {NET}]

將PIN位置替換我們導出文件的管腳名,NET位置填寫對應網絡名。生成管腳約束示例如下:

set_property PACKAGE_PIN AV20 [get_ports {DDR4_PARITY}]

set_property PACKAGE_PIN AV21 [get_ports {DDR4_DQS5_C}]

set_propertyPACKAGE_PINAV22[get_ports{DDR4_DQS5_T}]

2、設置網絡I/O STANDARD 屬性。具體語法格式例子如下:

set_property IOSTANDARD PIN_STANDRAD [get_ports {NET}]將PIN_STANDRAD位置替換我們需要的I/O STANDARD標準,NET位置填寫對應網絡名。生成管腳約束示例如下:

set_property IOSTANDARD SSTL12_DCI [get_ports {DDR4_PARITY}]

set_property IOSTANDARD DIFF_POD12_DCI [get_ports {DDR4_DQS5_C}]

set_propertyIOSTANDARDDIFF_POD12_DCI[get_ports{DDR4_DQS5_T}]

具體電平標準請查閱芯片手冊。 3、設置網絡輸入/輸出屬性,具體語法格式如下:

set_property DIRECTION DIR [get_ports {NET}]將DIR位置替換我們管腳屬性,可以填寫INOUT OUT IN三種,分別對應輸入輸出、輸出和輸入;NET位置填寫對應網絡名。生成管腳約束示例如下:

set_property DIRECTION OUT [get_ports {DDR4_PARITY}]

set_property DIRECTION INOUT [get_ports {DDR4_DQS5_C}]

set_propertyDIRECTIONINOUT[get_ports{DDR4_DQS5_T}]

4、設置管腳差分關系。具體語法格式如下:

make_diff_pair_ports NET1 NET2將NET1 NET2位置填寫對應差分對的網絡名。生成管腳約束示例如下:

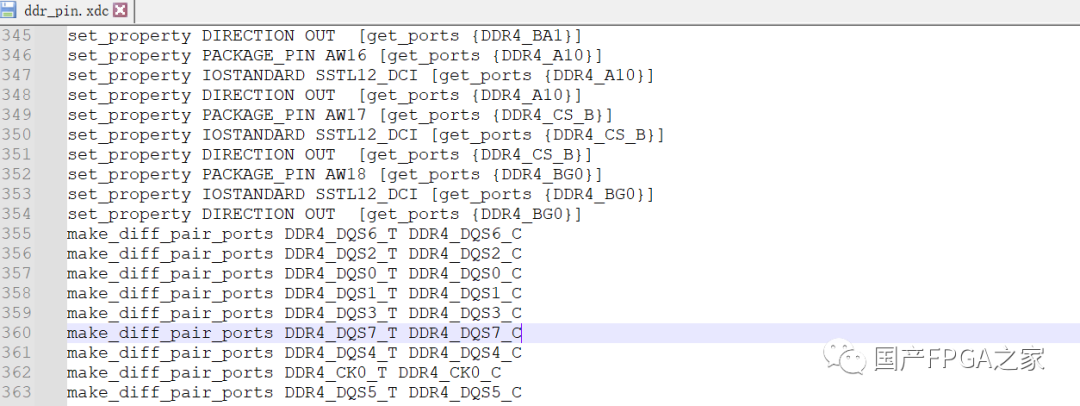

make_diff_pair_ports DDR4_DQS5_T DDR4_DQS5_C按照例子,對我們需要關注的管腳編寫約束文件,并將文件保存為.xdc格式,我這里保存是ddr_pin.xdc。

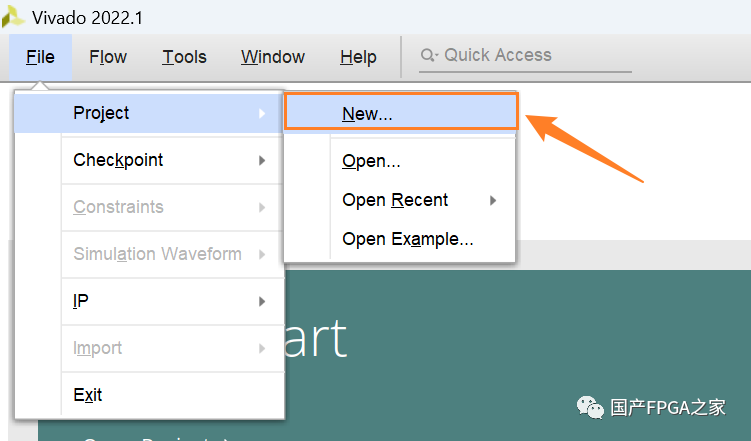

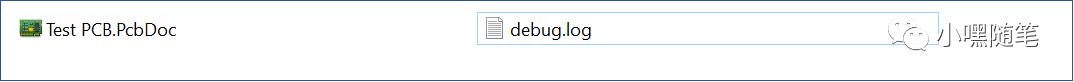

此過程流程操作流程相對簡單死板,推薦根據自己網絡命名規則編寫腳本減輕工作量。 4 I/O Planning 導出 ibis文件 Vivado 的 I/O Planning和RTL工程中均可以導出ibis 文件。RTL工程中導出方法不在此處贅述。 1)新建I/O Planning 工程

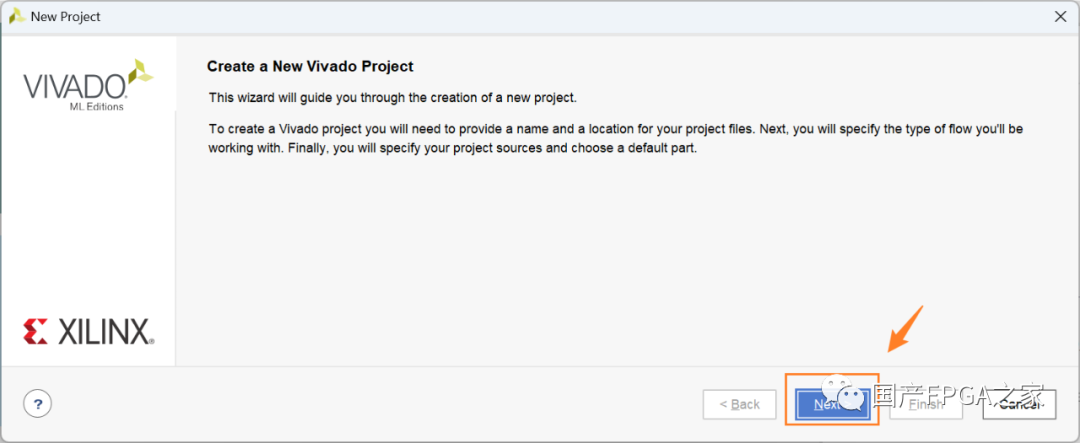

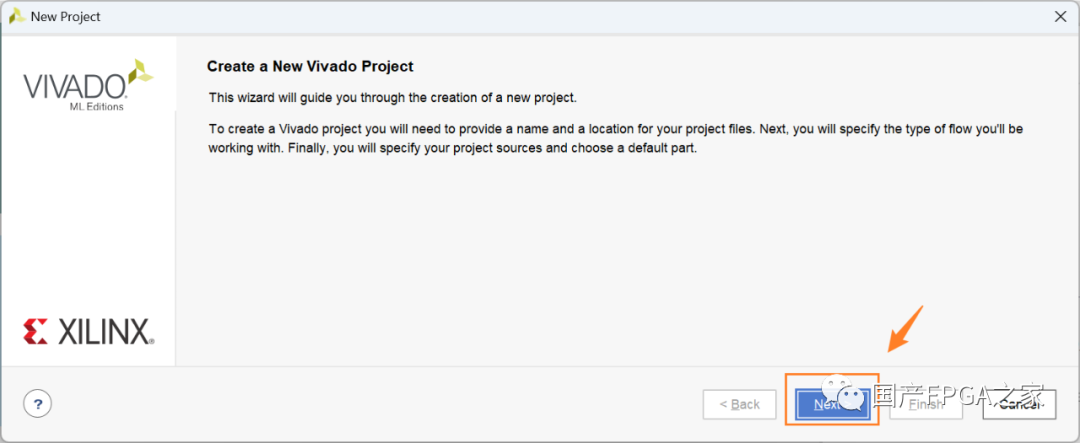

2)出現彈窗

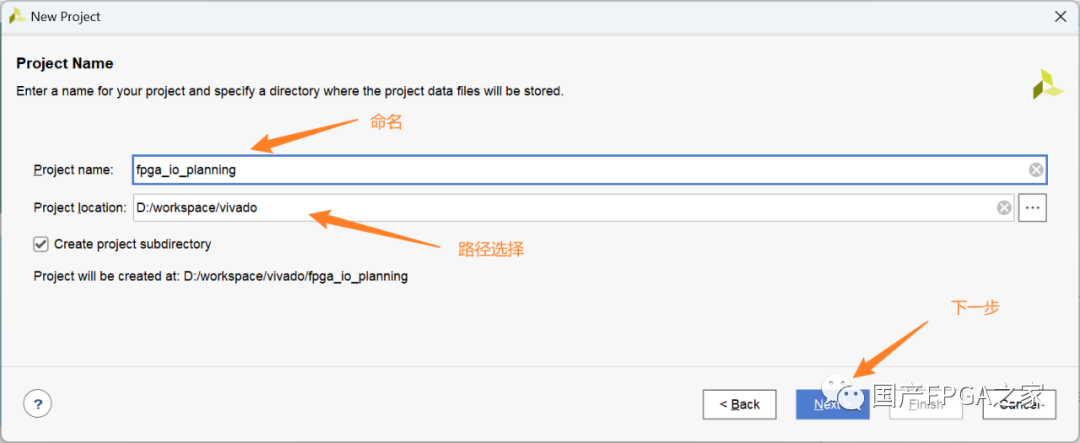

3)工程命名與路徑選擇

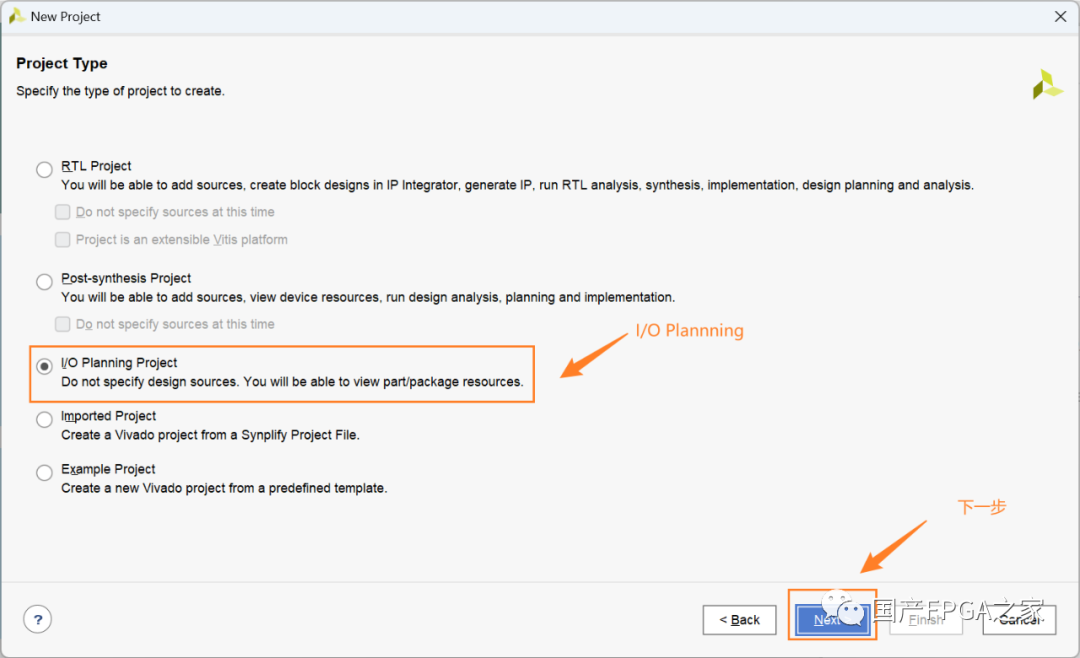

4)選擇 I/O Planning 工程類型

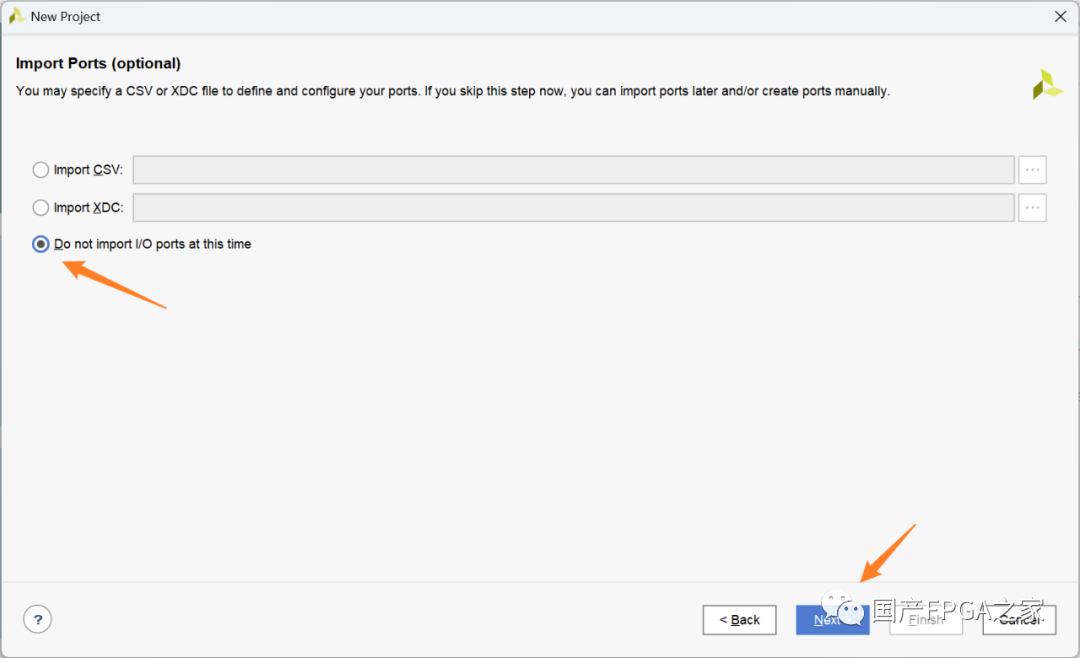

5)不導入文件,點擊下一步

6)根據需求選擇器件型號,點擊下一步后,點擊Finish 創建工程

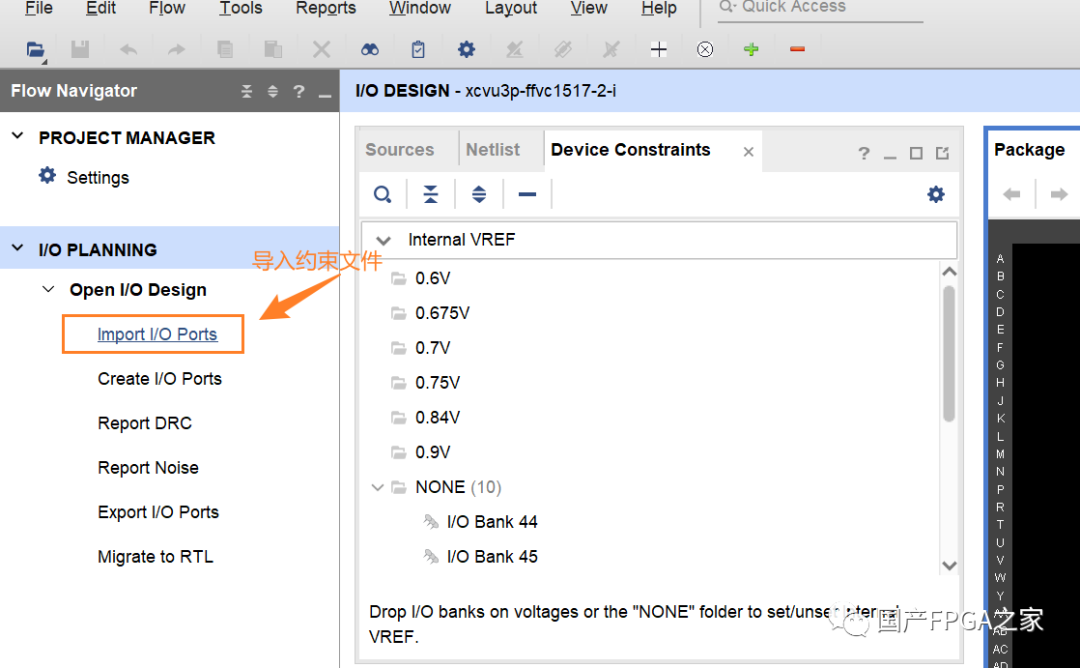

7)出現工程界面后,點擊導入I/O Ports

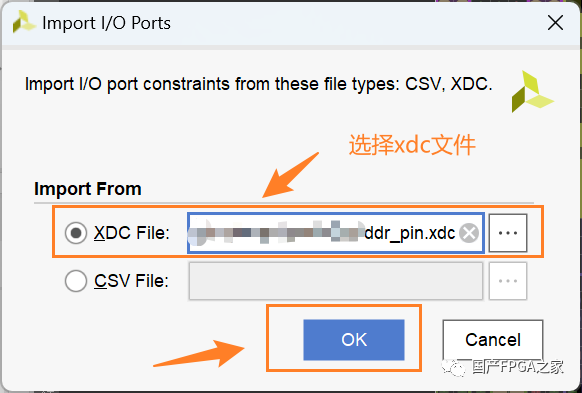

8)彈窗中選擇準備好的xdc文件,點擊OK。

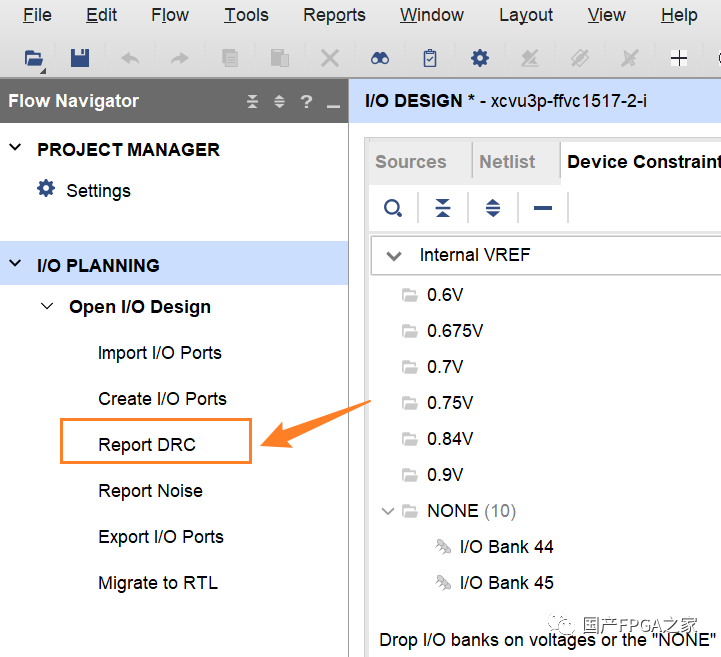

9)點擊 Report DRC進行檢查。

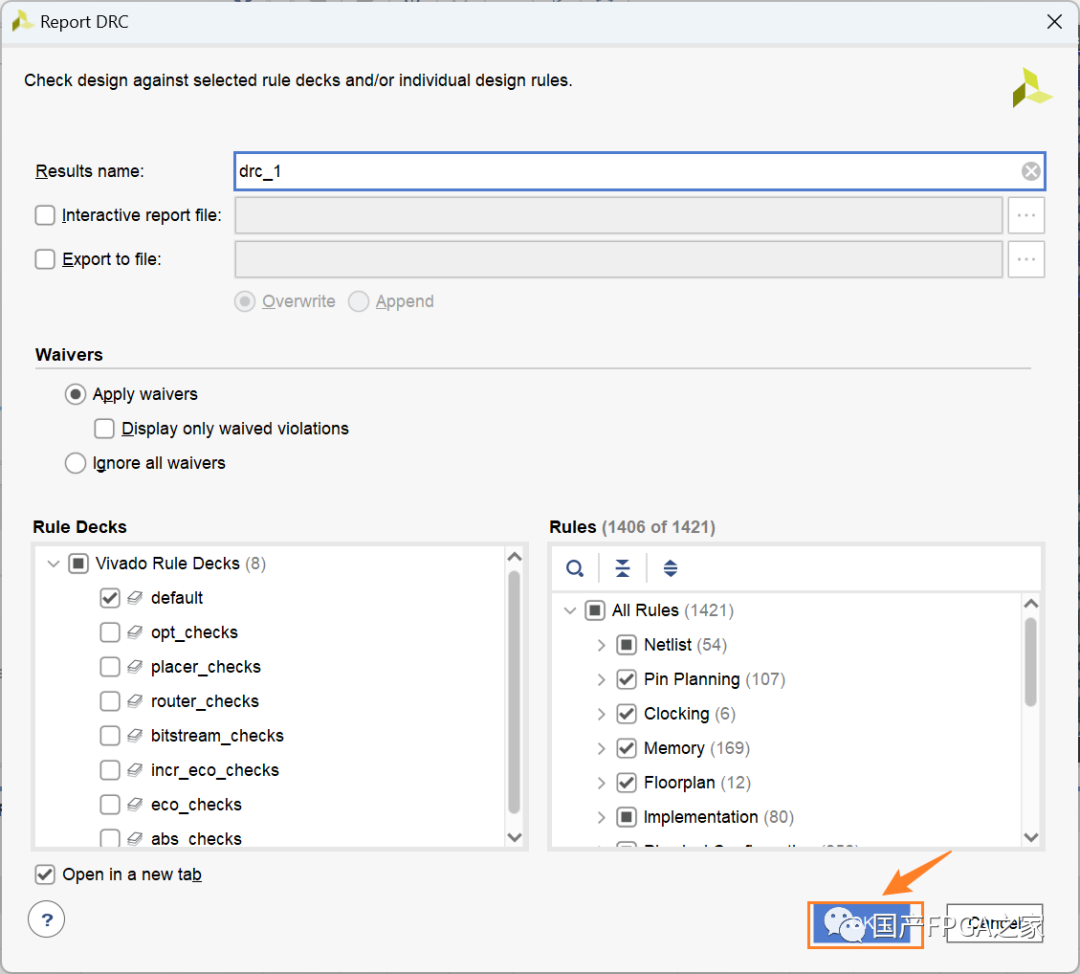

10)彈窗選擇OK,如出現DRC報錯需要復核硬件設計解決,避免導致硬件設計存在缺陷。

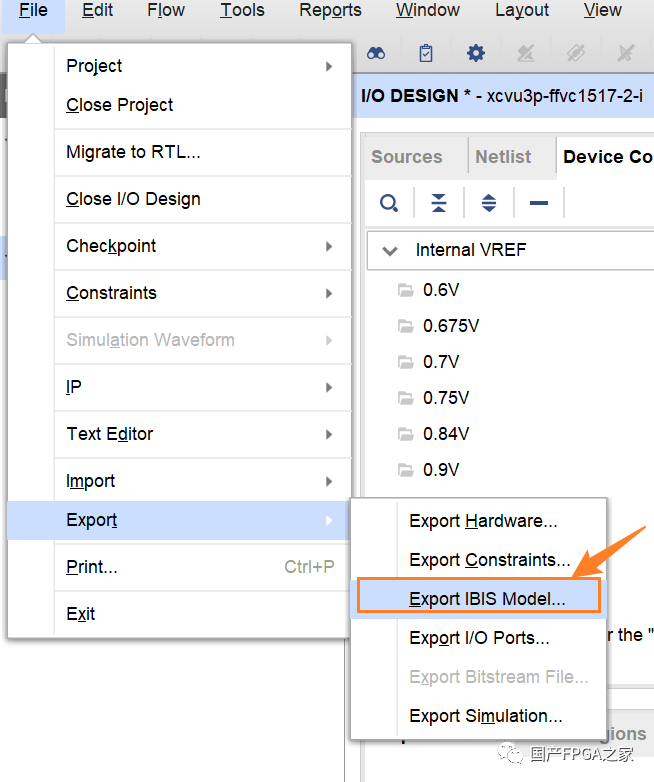

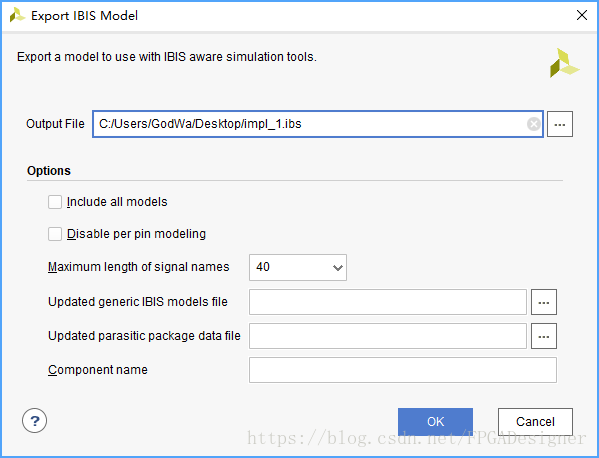

11)如DRC無報錯,點擊導出IBIS文件

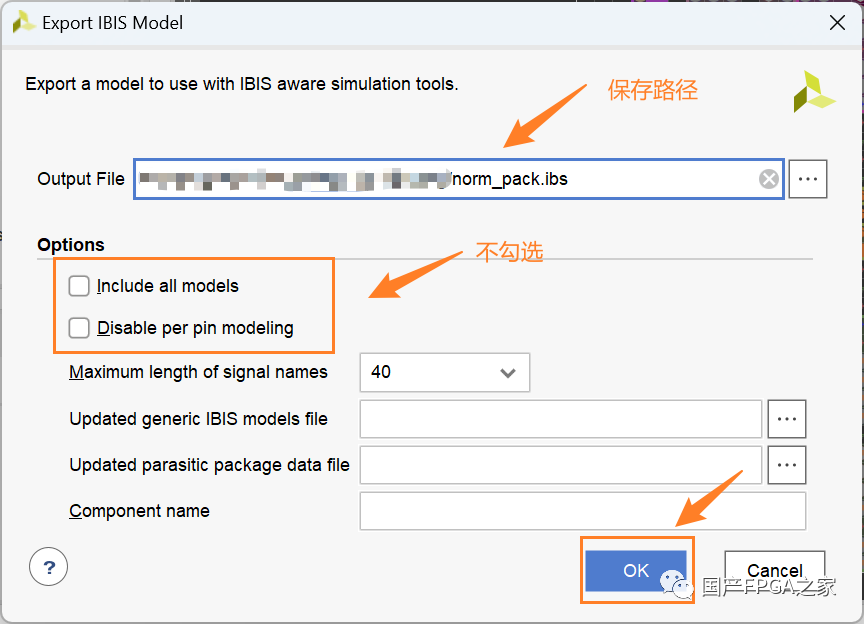

12)彈窗選擇保存路徑,完成導出。圖中兩個選項內容均不勾選。Include all models 選項勾選,在IBIS文件中增加我們沒有涉及 IO模型內容;Disable per pin modeling 會剔除IBIS文件中包含的封裝屬性文件。

13)到這里模型生成完成,可以用于實際仿真。

戰術總結

今天主要給大家簡單介紹了IBIS模型的使用方法以及Vivado如何快速導出IBIS模型進行后續仿真使用的方法,歡迎各位大師在評論區留言討論。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601807 -

傳輸線

+關注

關注

0文章

375瀏覽量

23997 -

IBIS模型

+關注

關注

8文章

15瀏覽量

17549 -

Vivado

+關注

關注

19文章

808瀏覽量

66322

原文標題:基于Vivado 的IBIS文件導出

文章出處:【微信號:國產FPGA之家,微信公眾號:國產FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么為防御等級Spartan-6生成IBIS文件

dose vivado如何將名稱導出到I/O端口列表文件?

如何從VIVADO 2014.3向系統生成器導出設計文件?

如何在IBIS文件中配置SSTL135 DCI阻抗

請問如何在Vivado中導出IO端口跟蹤長度?

pcb如何導出坐標文件

基于Vivado的IBIS文件導出

基于Vivado的IBIS文件導出

評論