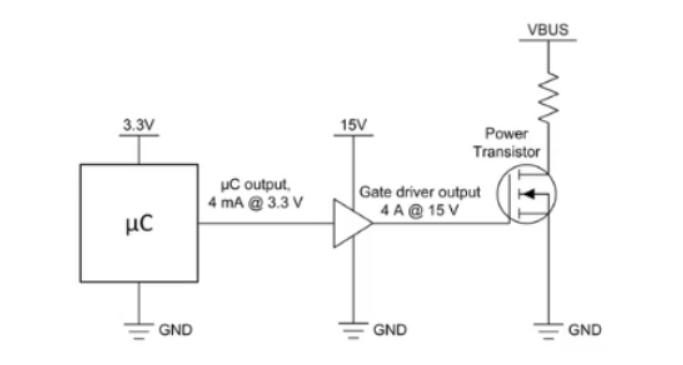

引言:在多相電源控制器里,PWM波輸出最為常見,但是HL型也使用較多,與PWM型相比,HL型控制更為獨立,更為靈活,抗干擾能力也較好,唯獨就是需要兩個控制輸出,本節簡述HL型柵極驅動器。

1.驅動結構

HL型也是以半橋配置驅動兩個N溝道MOSFET,支持電源電壓高達140V,高側和低側驅動器都可以用不同的接地參考來驅動MOSFET,從而提供出色的噪聲和瞬態抗擾性。其強大的0.8Ω下拉和1.5Ω上拉MOSFET驅動器允許使用大柵極電容的高壓MOSFET。附加功能包括UVLO、TTL/CMOS兼容輸入、可調開啟/關閉延遲和貫通保護。

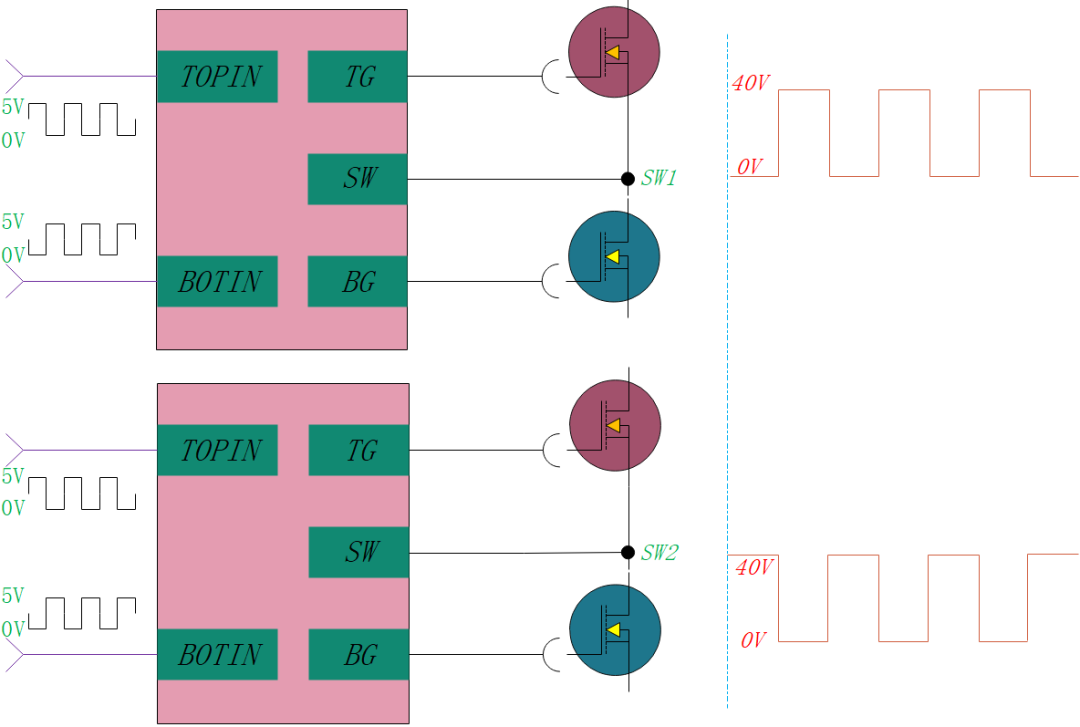

圖9-1:HL兩態驅動典型使用樣式

TOPIN:頂側驅動器的邏輯輸入,如果TOPIN是沒有偏置或浮動的,則TG保持在低位。

BOTIN:底部驅動器的邏輯輸入,如果BOTIN是沒有偏置或浮動的,則BG保持在低位。

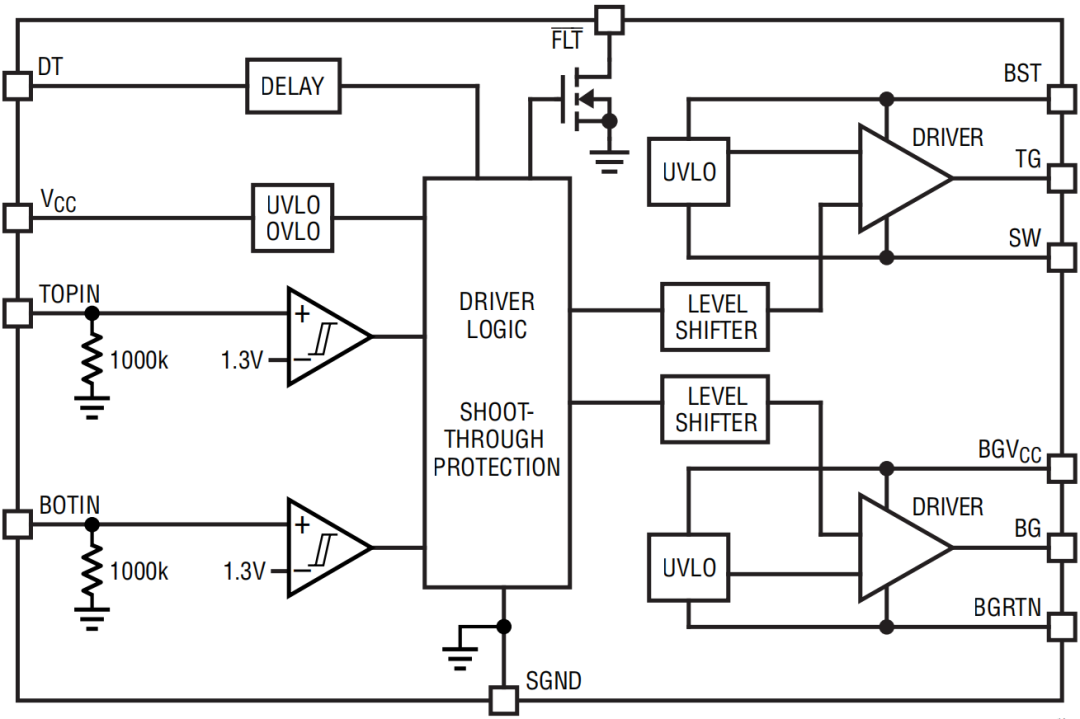

圖9-2:HL兩態柵極驅動器內部結構

HL型柵極驅動器具有兩個接地參考的低電壓數字信號輸入,用于驅動半橋配置中的兩個N溝道功率MOSFET。輸出BG被驅動為高或低,在BGVCC和BGRTN之間擺動,這取決于BOTIN引腳,類似地,輸出TG在BST和SW之間擺動。每個通道都由其輸入引腳(TOPIN和BOTIN)控制,允許獨立靈活地控制輸出的開啟和關閉狀態,但不允許TG和BG輸出同時變高。具有出色的噪聲和瞬態抗擾性,包括開關節點(SW、BGRTN)上的大負接地差容限(?10V),對稱設計允許半橋輸出是輸入邏輯的反相或非反相。

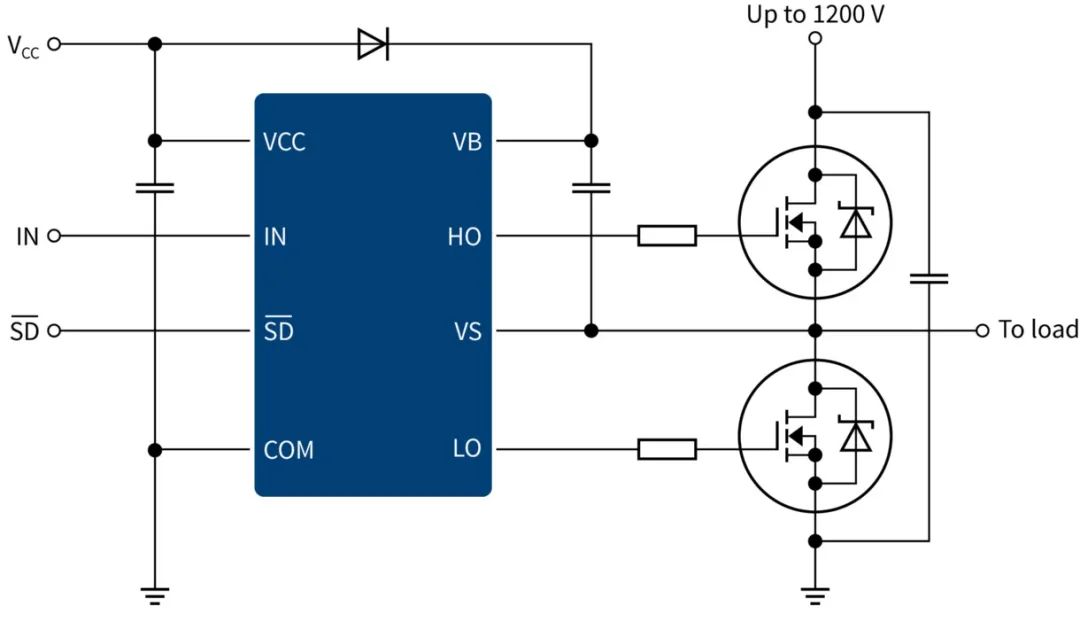

圖9-3:半橋驅動IC的基本連接形式

圖9-3的輸入和圖9-1的輸入有所不同,圖9-3將IN信號經過一個內部施密特觸發器之后進行反相,IN信號控制HS,/IN控制LS,然后中間間隔一定的死區時間,所以這種是類似HL型的柵極驅動器。

2.驅動邏輯

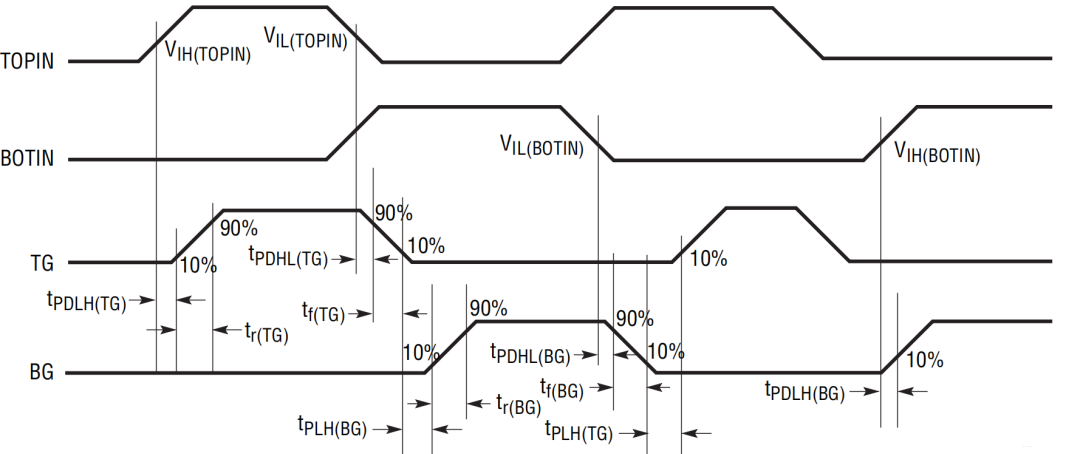

HL柵極驅動器采用兩個具有固定轉換閾值的邏輯輸入,當TOPIN上的電壓大于閾值VIH(TOPIN)時,TG被上拉到BST,使高側MOSFET導通。該MOSFET將保持導通,直到TOPIN下降到VIL(TOPIN)以下。類似地,當BOTIN大于VIH(BOTIN)時,BG被上拉到BGVCC,使低側MOSFET導通,BG將保持高電平,直到BOTIN下降到閾值VIL(BOTIN)以下。對應的VIH和VIL電壓電平之間的滯后消除了由于開關轉換期間的噪聲而引起的錯誤觸發,但是應注意防止噪聲耦合到輸入引腳(TOPIN、BOTIN),特別是在高頻和高電壓應用中。

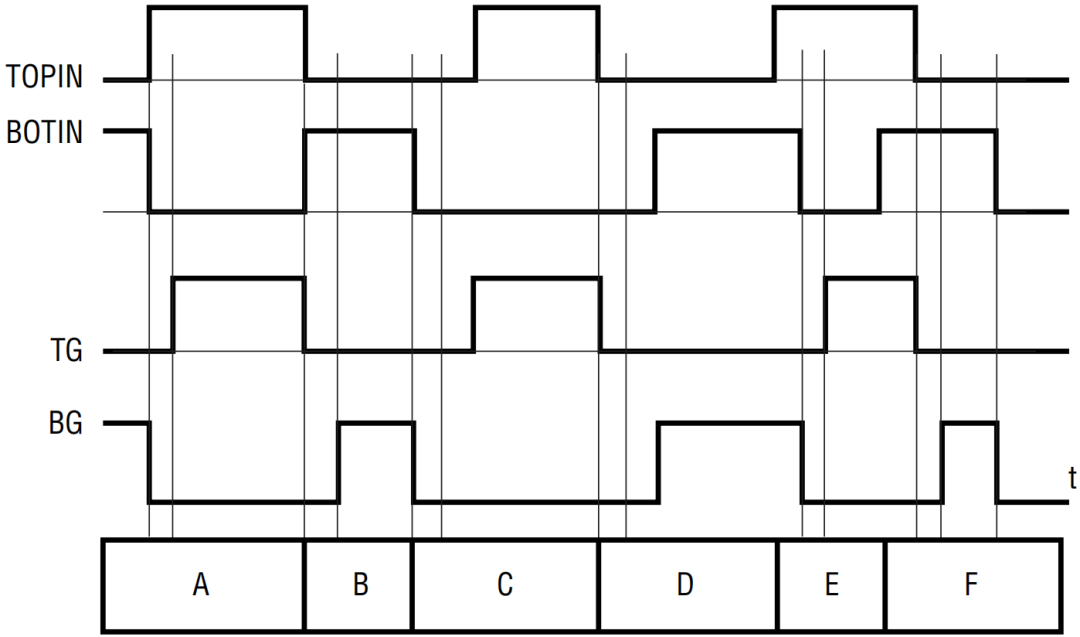

圖9-4:兩態柵極驅動器時序圖

當TOPIN/BOTIN引腳浮動時,從TOPIN/BONTIN引腳到SGND有一個內部1000kΩ下拉電阻器,如果輸入未被驅動,則保持TG/BG默認狀態為低。PWM控制器IC可以利用TOPIN和BOTIN輸入引腳來在開關調節器應用中執行不連續傳導模式(DCM)。圖9-5表示了輸入和輸出的邏輯關系:

圖9-5:輸入和輸出的邏輯關系

狀況A:TOPIN走高,BOTIN走低,BOTIN立即將BG設置為低,允許TG在tdt之后變高。

條件B:TOPIN變低,BOTIN變高,TOPIN立即將TG設置為低,允許BG在tdt之后變高。

條件C:TOPIN上升,BOTIN下降自身停滯時間大于tdt,因此當TOPIN變高時,TG立即被設置為高。

條件D:TOPIN下降和BOTIN上升自身停滯時間大于tdt,因此當BOTIN變高時,BG立即被設置為高。

條件E:TOPIN高,而BOTIN仍然高,BOTIN壓制TOPIN上升沿,在BOTIN變低加上tdt之后,允許TG變高。

條件F:BOTIN高,而TOPIN仍然高,TOPIN壓制BOTIN上升沿,在TOTIN變低加上tdt之后,允許BG變高。

注:TG指SW,BG指BGRTN。

此外,驅動器輸出上的強下拉防止了交叉傳導電流,例如,在圖9-1所示的半橋配置中,當BG關閉低側功率MOSFET,TG打開高側功率MOSFET時,SW引腳上的電壓可能會非常迅速地上升到VIN。該高頻正電壓瞬態將通過低側功率MOSFET的CGD電容耦合到BG引腳。如果BG引腳沒有被充分壓下,BG引腳上的電壓可能會上升到低側功率MOSFET的閾值電壓以上,從而瞬間使其重新導通。因此,高側和低側MOSFET都將導通,這將導致大量的交叉導通電流通過MOSFET從VIN流到地,從而導致相當大的功率損失并且可能損壞MOSFET。因此,建議使用BG和TG引腳的短PCB跡線,以最大限度地減少寄生電感。

3.功耗

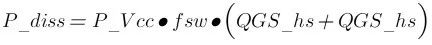

驅動器的功耗主要由外部功率MOSFET的柵極電荷提供,下列公式成立:

fsw是開關頻率,QGHS和QGLS分別是PVCC驅動電壓下的高側MOSFET的柵極電荷和低側MOSFET柵極電荷。

考慮具有一個高側MOSFET(BSC50NE2LS)和一個驅動電壓為5V和開關頻率為500KHz的低側MOSFET的降壓轉換器應用,功率耗散是:

驅動器本身也有少量功耗,在300KHz的開關頻率下,驅動器的功耗在10mW的范圍內,該功耗由IPVCC_300kHz乘以驅動電壓(5V)得出。

- layout注意事項

HL柵極驅動器需要在VCC、VBST-SW和VBGVCC-BGRTN電源上進行適當的旁路,因為它具有ns級高速開關和A級大交流電流。不小心的元件放置和PCB布線可能會導致過度振鈴和欠調/過調。并且PCB和功率器件封裝(上下MOSFET)的寄生電感會導致嚴重的振鈴,超過器件的絕對最大額定值,優秀的布局可以幫助最大限度地減少這種不必要的影響。

1:在VCC和SGND引腳、BGVCC和BGRTN引腳以及BST和SW引腳之間安裝盡可能靠近的旁路電容器,引線應盡可能縮短,以減少引線電感。保持去耦回路(PVCC-GND和BOOT-PHASE)盡可能短。

2:使用低電感、低阻抗接地平面來減少任何接地跌落和雜散電容,驅動器開關的峰值電流大于5A,任何顯著的接地壓降都會降低信號的完整性,最小化走線電感,尤其是在低阻抗線路上,所有電源走(UGATE、PHASE、LGATE、GND、PVCC)應盡可能短且寬,PHASE節點也應該是短而寬的。最小化PHASE節點與高側MOSFET源極和低側MOSFET漏極之間的距離,以避免效率損失。

3:仔細規劃電源/接地布線,了解大負載開關電流的來源和去向,為輸入引腳和輸出功率級保持單獨的接地回路。

4:Kelvin將TG引腳連接到頂部MOSFET柵極,將SW引腳連接到頂級MOSFET源極。Kelvin將BG引腳連接到底部MOSFET柵極,將BGRTN連接到底部FET的源極,保持驅動器輸出引腳和負載之間的走線短而寬。

5:確保將驅動器封裝背面的外露焊盤焊接到板上,如果暴露的背面和銅板之間沒有良好的熱接觸,將導致熱阻遠大于封裝的規定值。

6:最小化輸出和輸入傳導的電流回路,將下部MOSFET的源極連接短接至接地,盡可能靠近晶體管引腳,輸入電容器(尤其是陶瓷去耦)應盡可能靠近上部MOSFET的漏極和下部MOSFET的源極。

為了優化散熱,無論IC是否有暴露的焊盤,都應將銅皮鋪滿IC下方,銅區域可以延伸超過IC的底部區域和/或通過熱過孔連接到埋銅平面,用于垂直散熱的過孔、延伸的銅平面和用于散熱的埋平面的這種組合可以實現IC全部散熱能力。

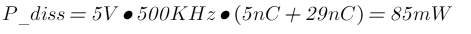

5.layout示例

在圖9-6中,示出了具有SuperSO-8高側MOSFET和低側MOSFET的局部布局示例,驅動器的相位連接盡可能靠近高側MOSFET的源極,并且為了提高連接本身的可靠性和寄生電感,過孔被加倍。

VCC和PVCC的兩個去耦電容,以及BOOT電容,都放置在驅動器所在的底部,為了與低側MOSFET具有非常好的熱耦合和非常小的寄生電感,使用多個過孔將驅動器的露焊盤連接到GND,GND最終是低側MOSFET的源極。

圖9-6:5相位電源示例

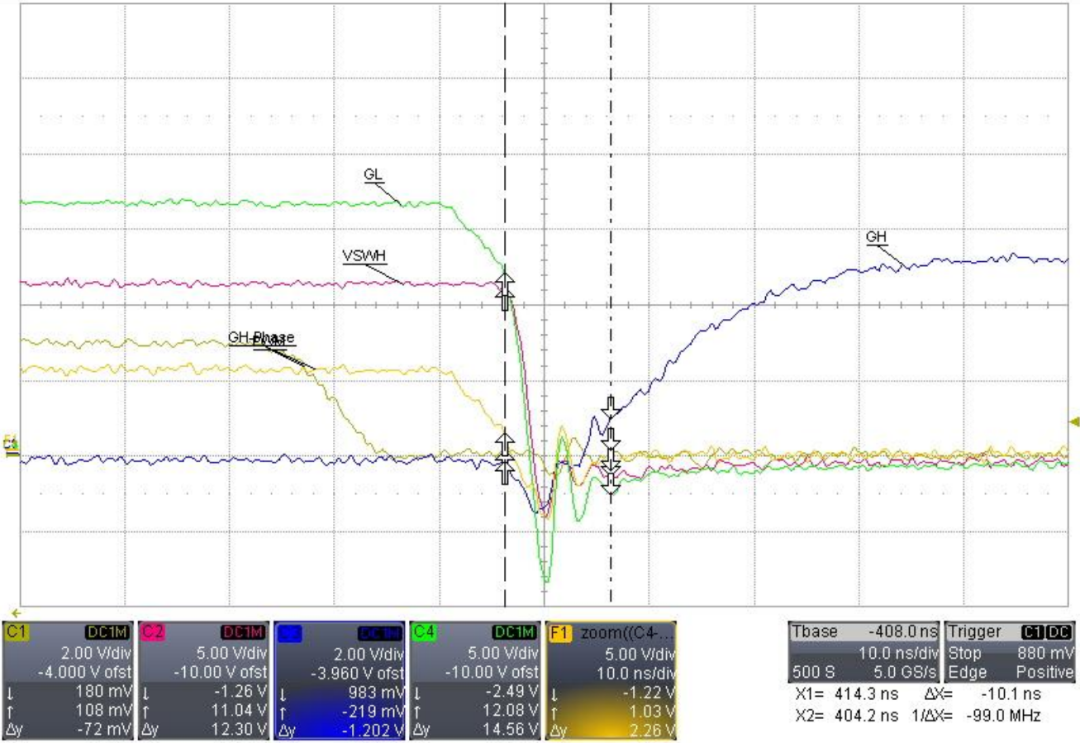

如圖9-7所示,從高側開啟到高側關閉和低側開啟的過渡時間非常小,VSW引腳的下降沿在4ns的范圍內,同時完全切換高側柵極所需的時間在6ns的范圍內。由于噪聲,從VSW/PHASE節點識別高側MOSFET關斷和低側MOSFET導通之間的死區時間可能很困難,參考由低側MOSFET柵極信號在其克服1V值時給出,在這種情況下,死區時間可以估計在6ns左右。

圖9-7:TURN OFF

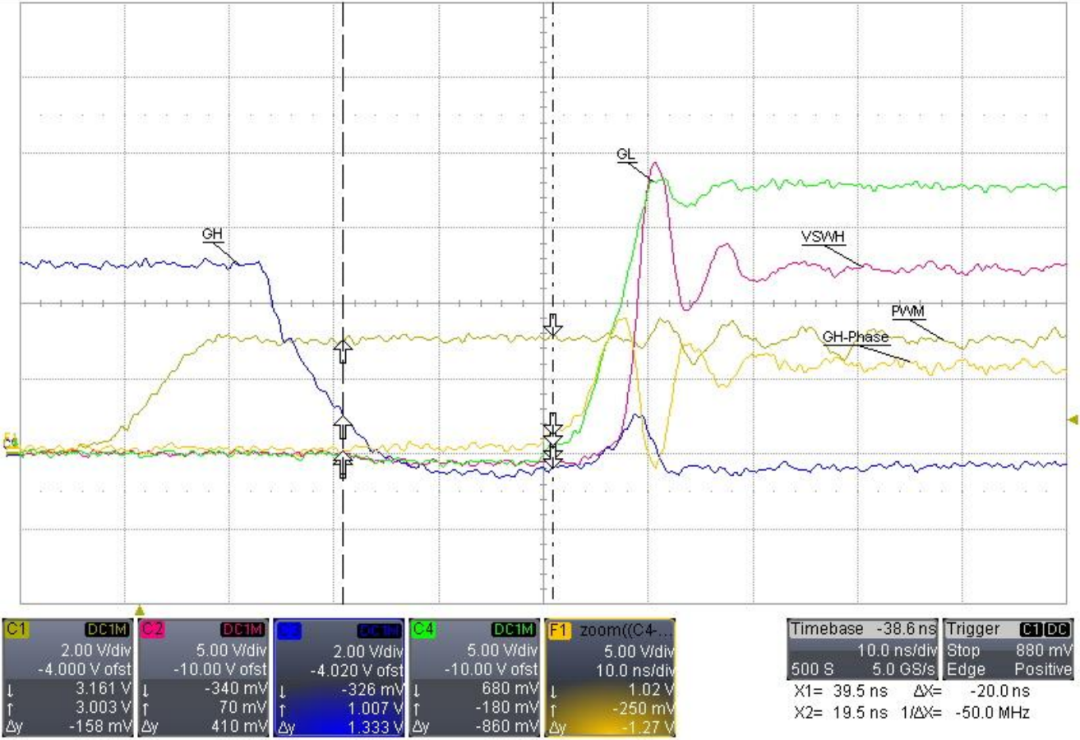

從低側MOSFET開啟到高側MOSFET打開的轉變如圖9-8所示。在這種情況下,VSW/PHASE節點的上升沿在4ns的范圍內,考慮到低側柵極何時跨過1V閾值,死區時間的持續時間更多地在10ns的范圍內。在高側MOSFET的上升沿期間,可以在低側MOSFET柵極上看到尖峰,該尖峰通常被理解為感應導通的標志(在VSW/PHASE節點)。大多數時候,由于封裝或走線連接的寄生電感,柵極上的尖峰只不過是尖峰,換句話說,尖峰不會立即轉換為在低側MOSFET的VGS上的尖峰。

圖9-8:TURN ON

-

MOSFET

+關注

關注

146文章

7101瀏覽量

212769 -

驅動器

+關注

關注

52文章

8168瀏覽量

146051 -

控制器

+關注

關注

112文章

16214瀏覽量

177478 -

PWM

+關注

關注

114文章

5153瀏覽量

213447 -

柵極驅動器

+關注

關注

8文章

732瀏覽量

38959

發布評論請先 登錄

相關推薦

HL型柵極驅動器內部結構解析

HL型柵極驅動器內部結構解析

評論