Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

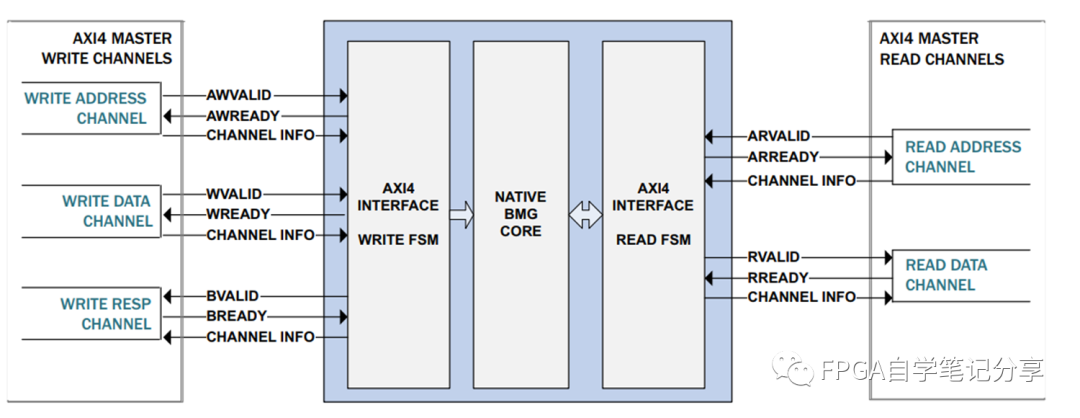

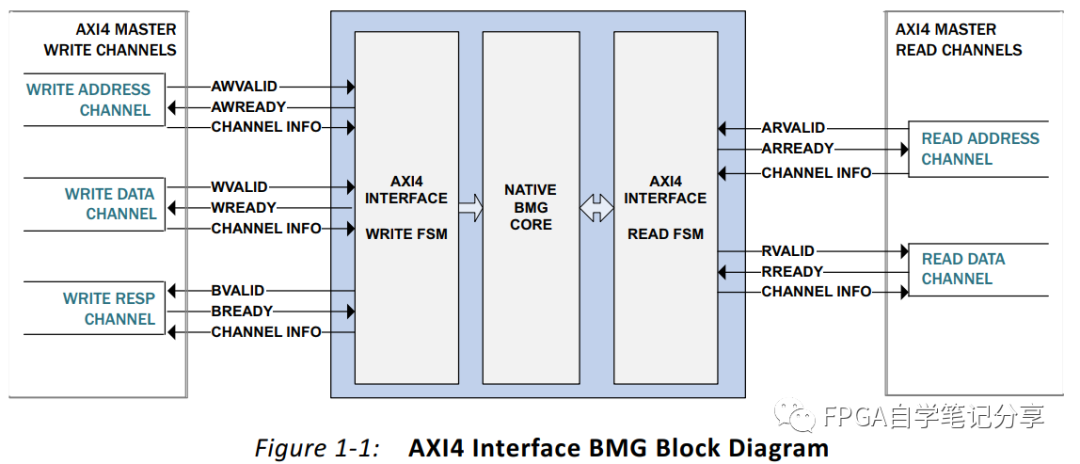

支持普通接口和AXI兩種接口。BMG IP的AXI4接口配置派生自本地接口 配置,在IP中添加了一個行業標準總線協議接口。有兩種可用的AXI4 接口樣式:AXI4和 AXI4- lite。

功能概述:

?優化算法最小塊RAM資源利用率或低功耗利用率

?可配置內存初始化

?在UltraScale?,UltraScale+?,Zynq?-7000,

Spartan?-7,Artix?-7,Kintex?-7和Virtex?-7器件上獨立的byte寫使能(帶或不帶奇偶校驗)

?優化的Verilog行為模型用于仿真提速;精確的結構仿真模型用于模擬存儲行為

?每個端口可選擇的操作模式:WRITE_FIRST, READ_FIRST或NO_CHANGE

?SDP模式下有更低的數據寬度

?標準DOUT塊RAM級聯

使用普通接口時:

?生成單端口RAM,簡單雙端口RAM,真雙端口RAM,單端口

ROM和雙口ROM

?支持最大16M bytes的內存大小(字節大小8或9)(僅受選定部分的內存資源限制)

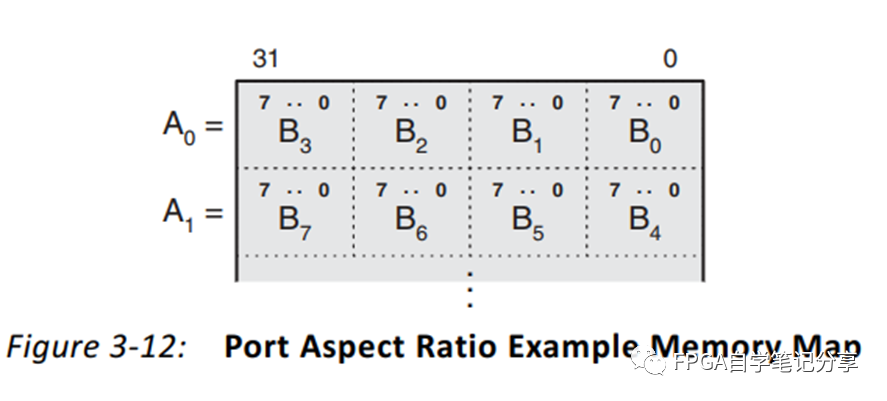

?可配置端口輸入輸出比

?支持內置ECC (Hamming Error Correction Capability)。錯誤注入引腳允許插入單位和雙位錯誤

?支持數據寬度小于64位的軟ECC (soft Hamming Error Correction)

?可選擇流水線DOUT總線,以提高特定配置的性能

?在SR (Set reset)或CE的優先級之間選擇輸出寄存器的復位優先級

?性能高達450 MHz

使用AXI4接口時:

?支持AXI4和AXI4- lite接口協議

?符合AXI4的內存和外設從屬類型

?獨立的讀寫通道

?零延遲數據路徑

?支持握手信號的寄存器輸出

?INCR突發大小高達256個數據傳輸

?WRAP突發大小為2、4、8和16

?AXI非對齊的突發傳輸

?簡單的雙端口RAM的配置

?性能高達300Mhz

?支持數據寬度高達256位和內存深度從1到1M字(僅受選定部分的內存資源限制)

?對稱輸入輸出

?異步active-Low復位

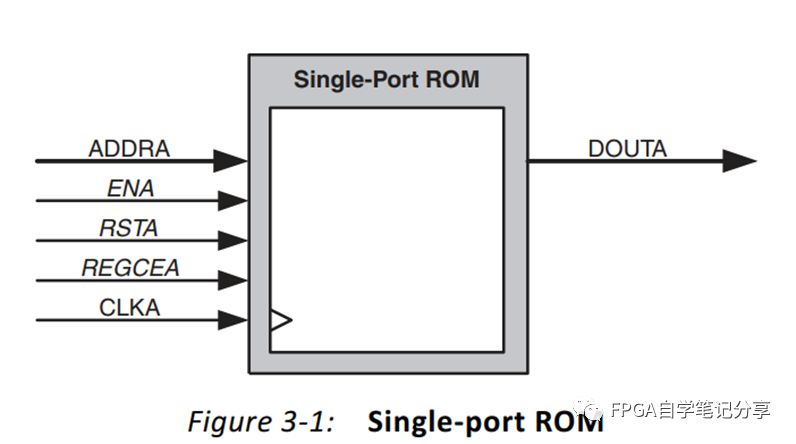

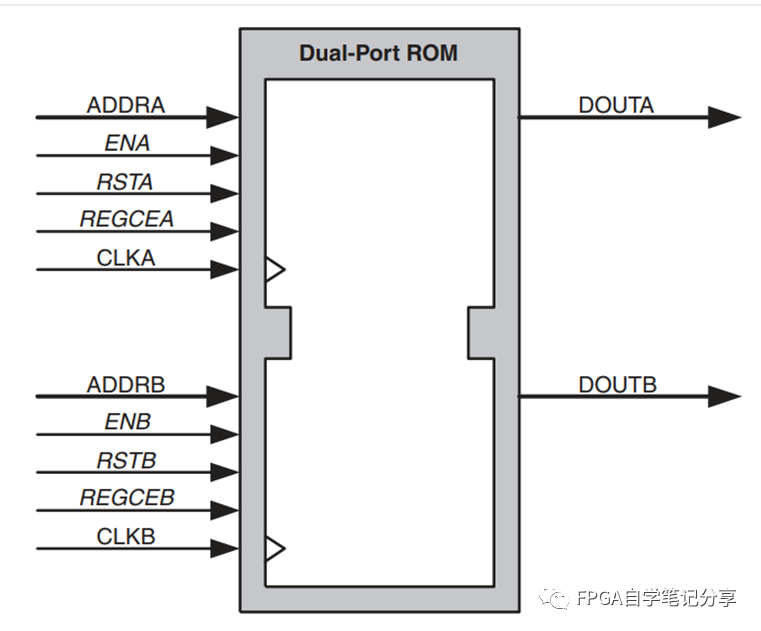

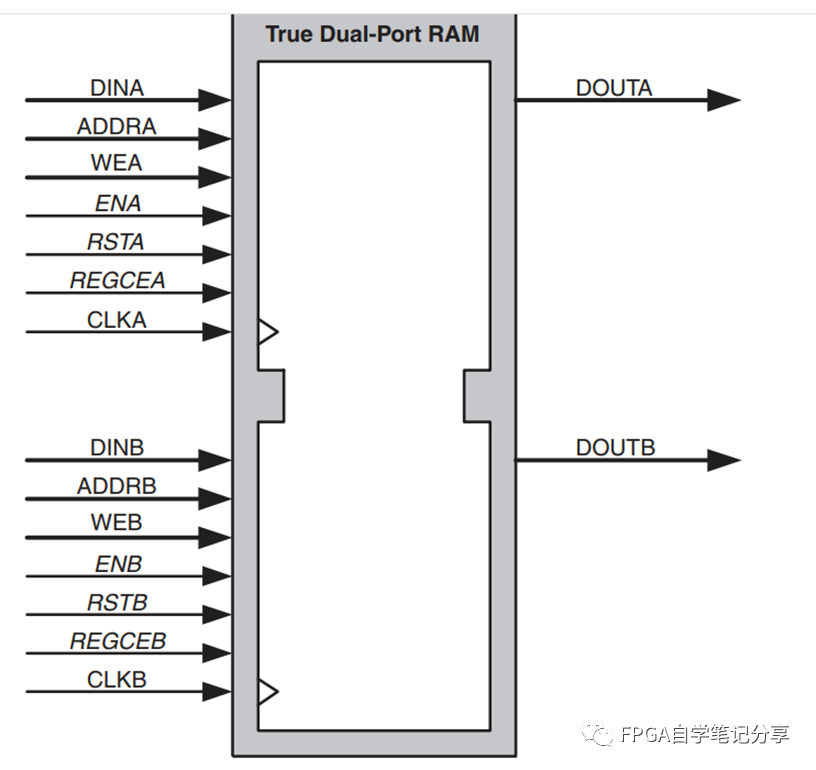

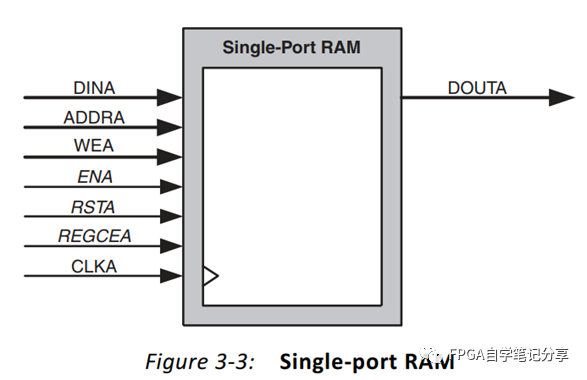

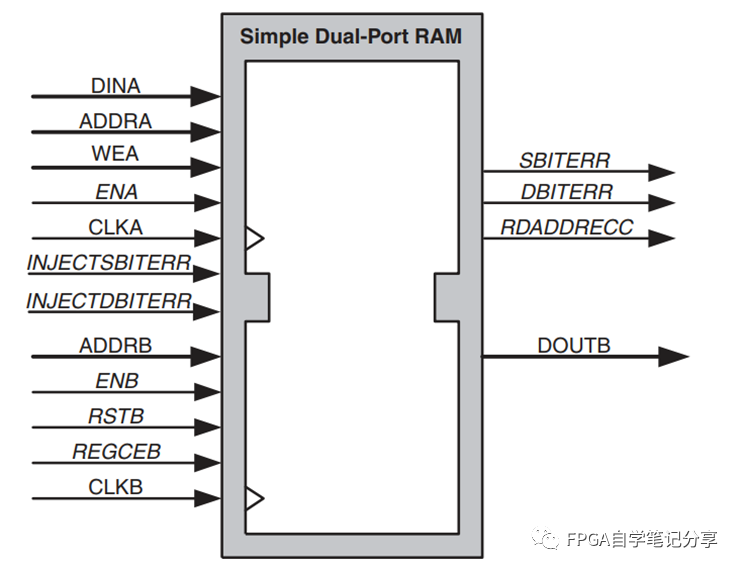

使用默認接口時,支持的工作模式:

?單端口RAM

?簡單的雙端口RAM

?真正的雙端口RAM

?單端口ROM

?雙端口ROM

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602004 -

嵌入式

+關注

關注

5071文章

19026瀏覽量

303492 -

Xilinx

+關注

關注

71文章

2164瀏覽量

121036 -

內存

+關注

關注

8文章

3004瀏覽量

73900

發布評論請先 登錄

相關推薦

XILINX FPGA IP之Clocking Wizard詳解

XILINX FPGA IP之MMCM PLL DRP時鐘動態重配詳解

Xilinx FPGA IP之Block Memory Generator AXI接口說明

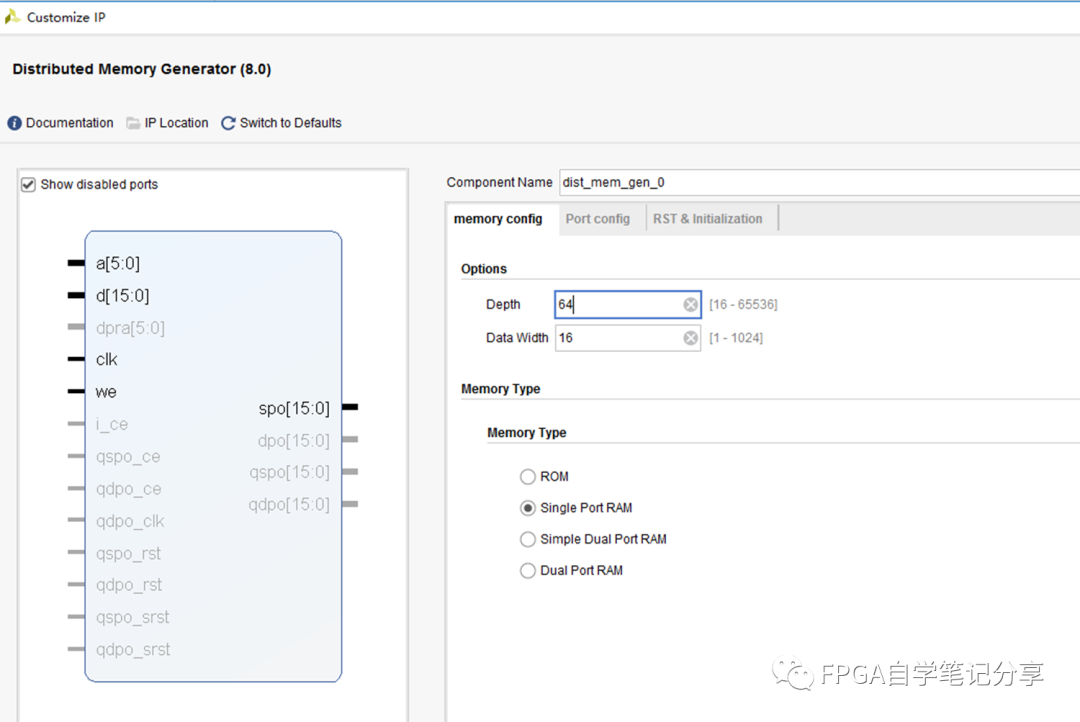

Distributed Memory Generator IP核簡介

XILINX FPGA IP之AXI Traffic Generator

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx FPGA IP之Block Memory Generator功能概述

評論