之前的文章對Block Memory Generator的原生接口做了說明和仿真,本文對AXI接口進行說明。

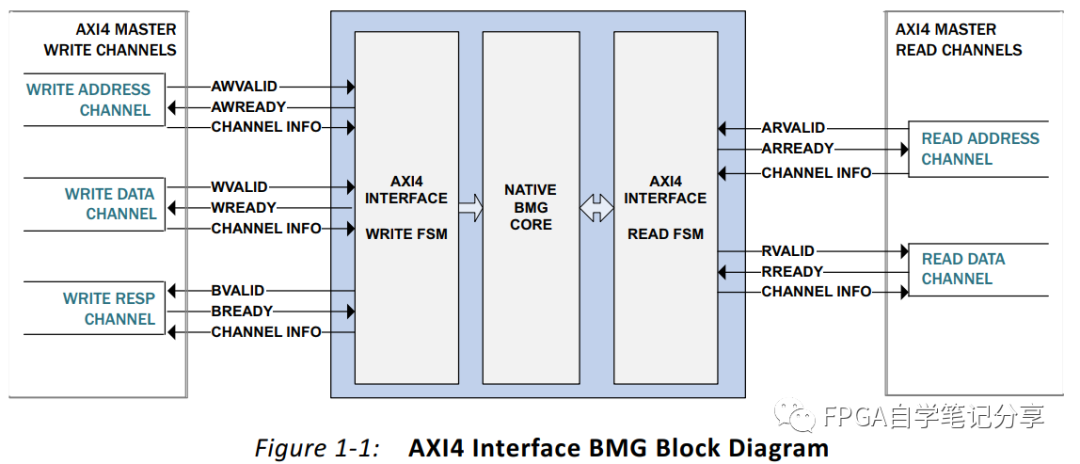

如下圖所示,AXI4接口的BMG是基于原生接口進行包裝的。有兩種可用的AXI4接口樣式:AXI4和AXI4- lite。

典型的應用場景包括:

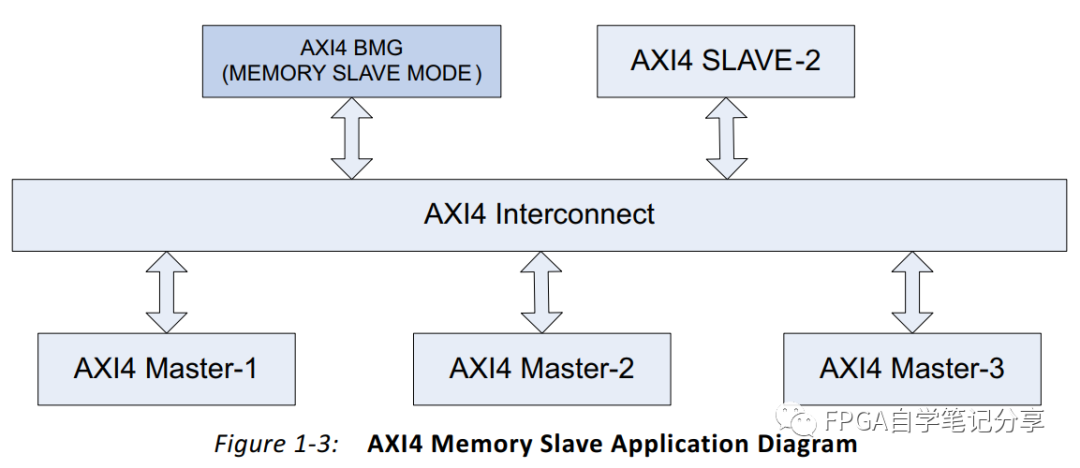

1、AXI4 Block Memories–Memory Slave Mode:內存從屬模式下的AXI4塊MEM,如下圖所示。

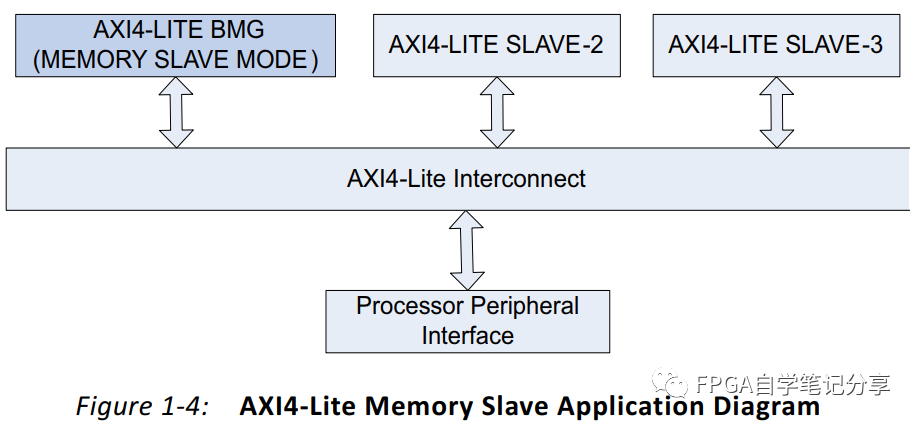

2、AXI4-Lite Block Memories–Memory Slave Mode:內存從屬模式下的AXI4-Lite塊MEM,如下圖所示。

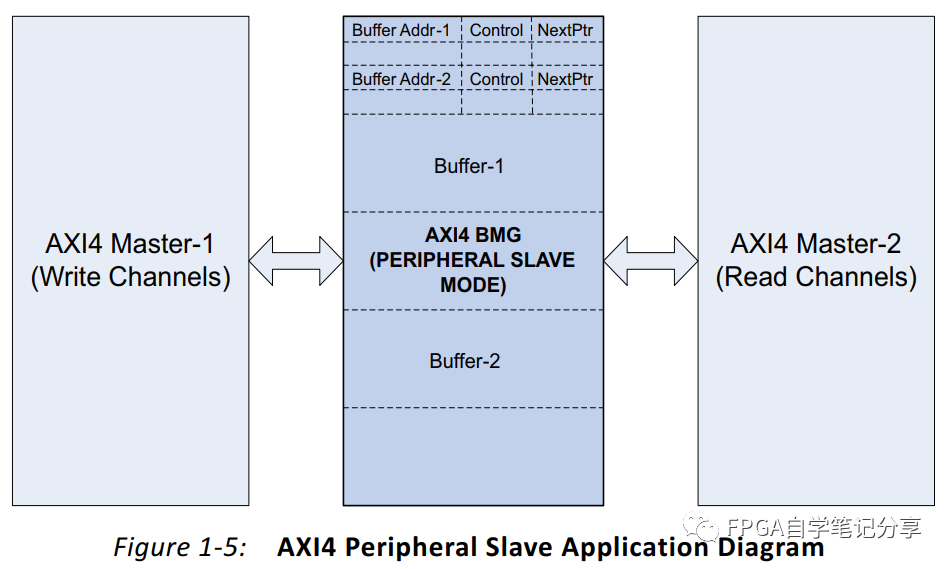

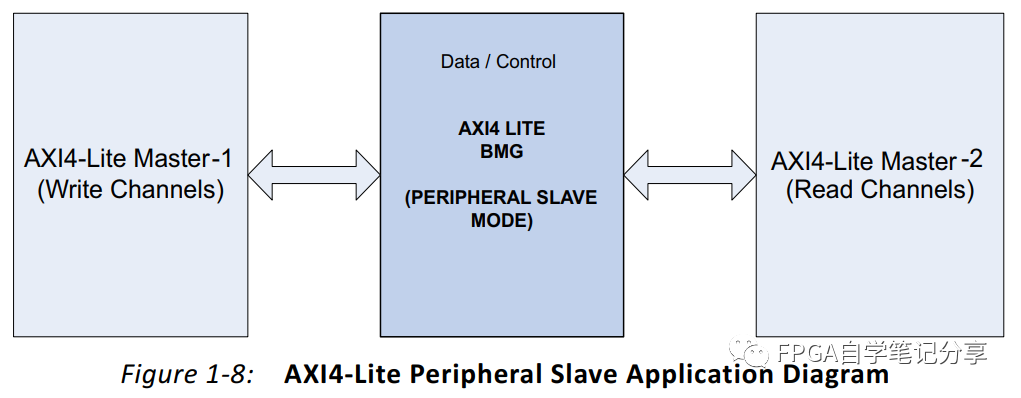

3、AXI4 Block Memories–Peripheral Slave Mode:外設從屬模式下的AXI4塊MEM,如下圖所示。

4、AXI4-Lite Block Memories–Peripheral Slave Mode:外設從屬模式下的AXI4-Lite塊MEM,如下圖所示。

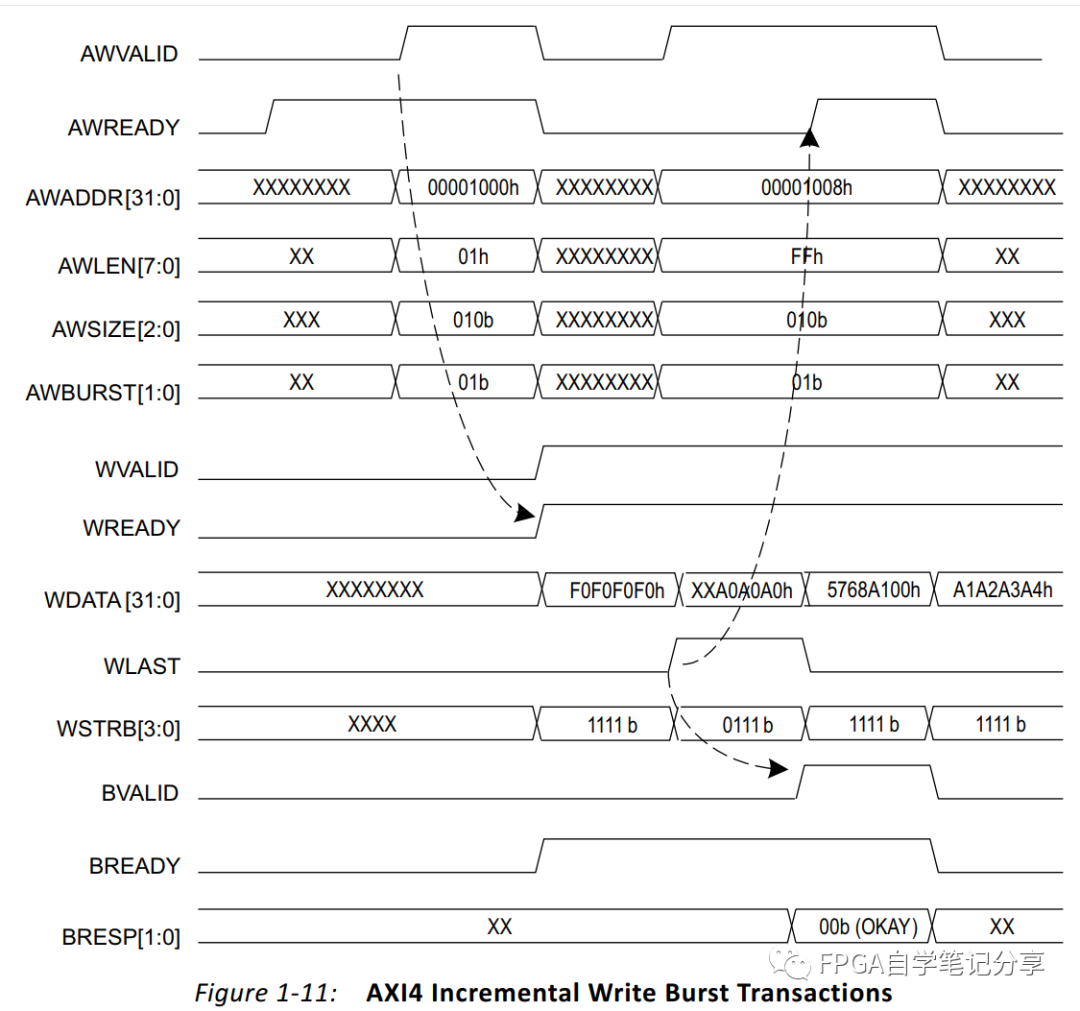

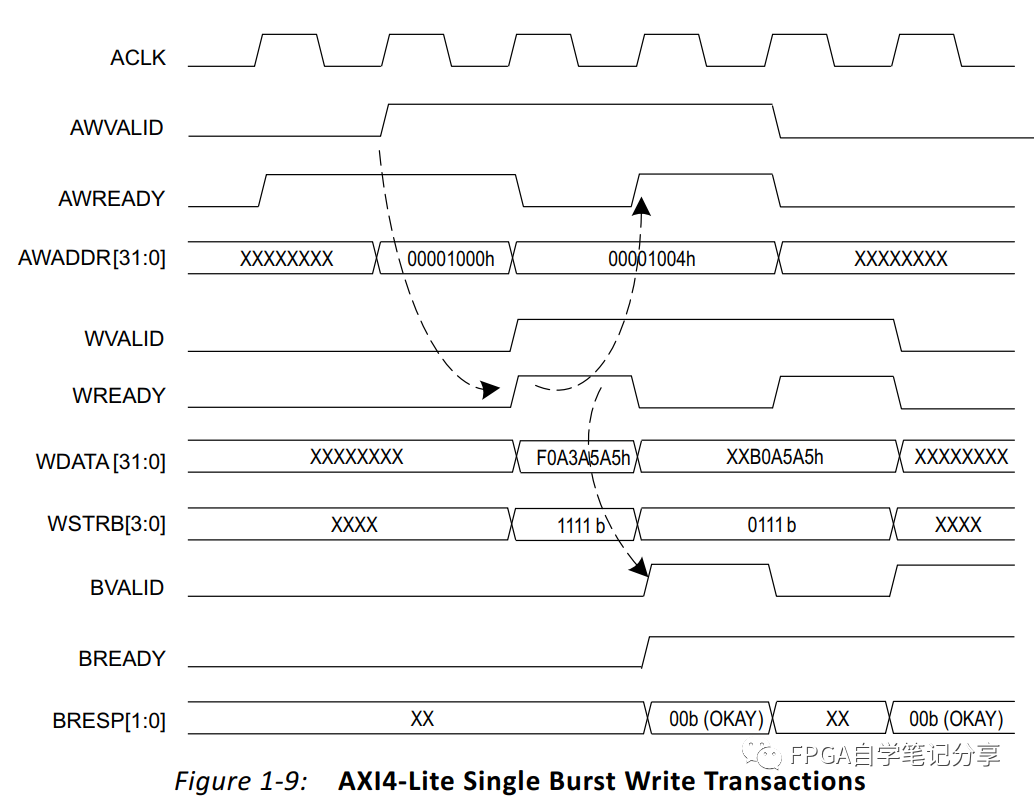

對于AXI4和AXI4-Lite接口的讀寫,就是標準的AXI4協議,AXI4和AXI4-Lite的寫操作如下圖所示。整個流程為:主端準備好寫地址(AXI4還有AWLEN、AWSIZE、AWSIZE、AWBURST信息)然后拉高AWVALID信號,當AWREADY拉高后表示地址被接受。同時主端準備好寫數據并拉高AVALID信號(不用等待從端拉高AWREADY),當WREADY拉高后表示數據被接受。在AXI4模式下,BURST的最后一個輸出傳輸時要拉高WLAST信號。最后從端返回響應信號。詳細的依賴關系可參考FPGA IP之AXI4協議3_通道間的依賴關系。

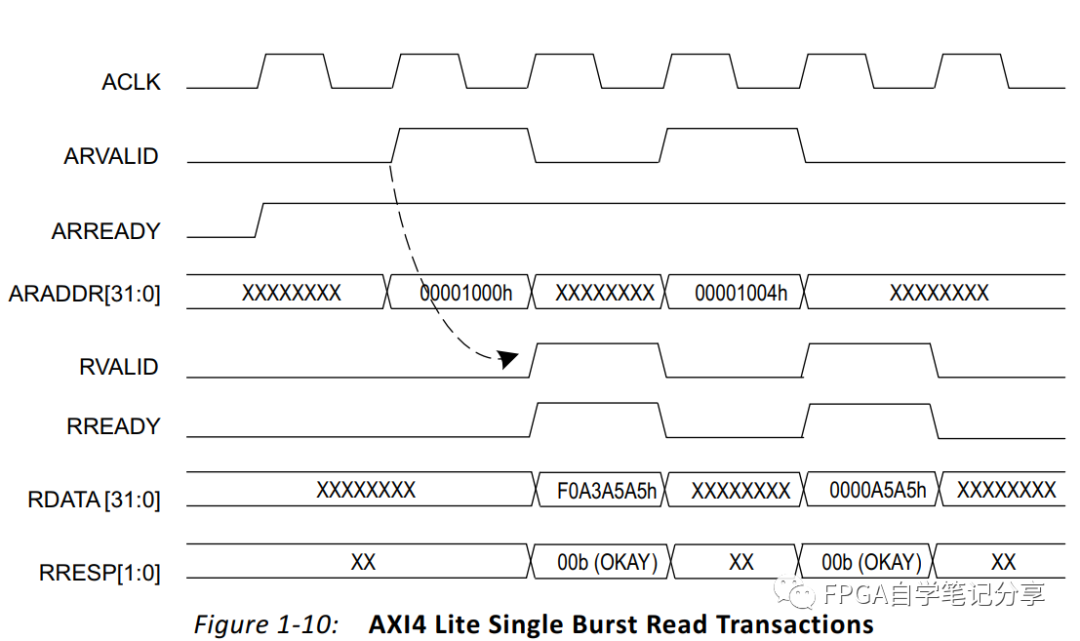

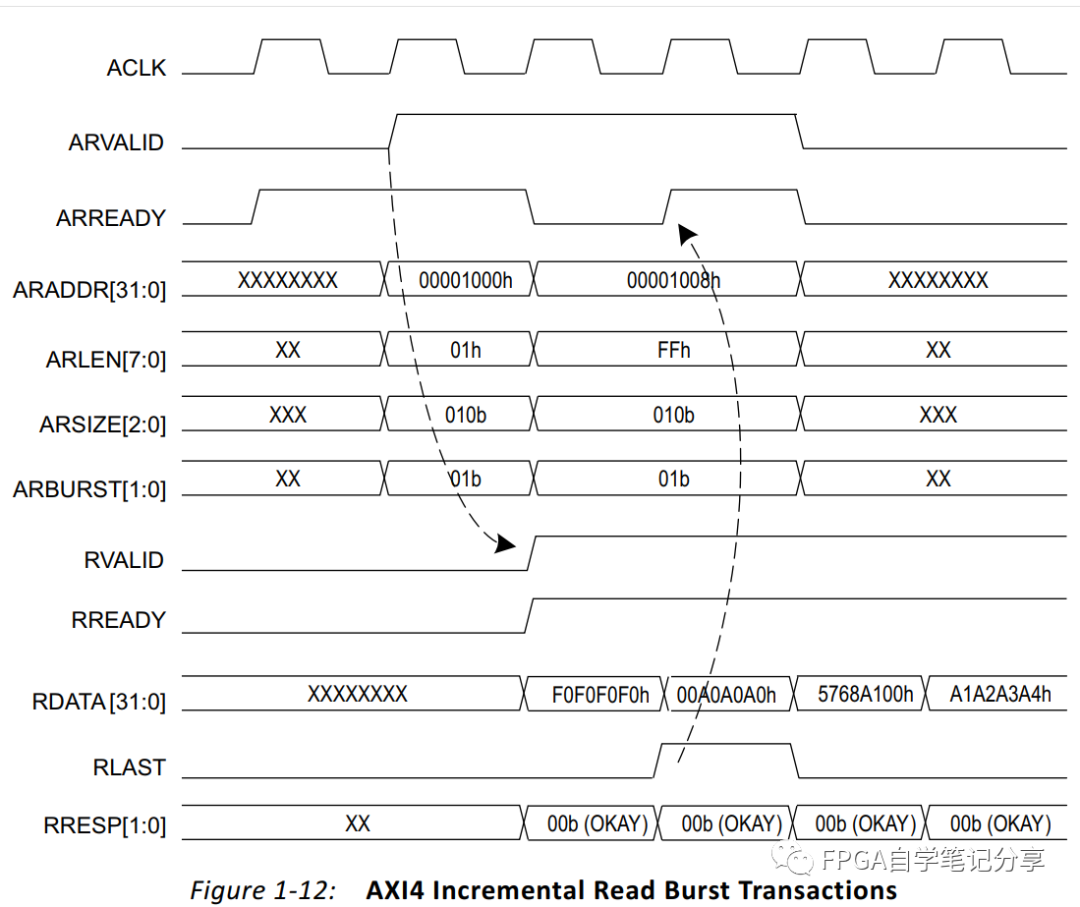

AXI4和AXI4-Lite的讀操作如下圖所示。整個流程為:主端準備好寫地址(AXI4還有ARLEN、ARSIZE、ARBURST信息)然后拉高ARVALID信號,當ARREADY拉高后表示地址被接受。同時從端準備好寫數據并拉高RVALID信號,當RREADY拉高后表示數據被接受。在AXI4模式下,BURST的最后一個輸出傳輸時要拉高RLAST信號。最后從端返回響應信號。詳細的依賴關系可參考FPGA IP之AXI4協議3_通道間的依賴關系

當然AXI4接口除了支持上圖中的Incremental Burst(增量突發)模式外,還支持Wrap Burst、Narrow Transactions 、Unaligned Transactions 模式,這些僅是接口方式的差異,主要是對AXI4協議的支持上,和Block Memory關系不大,這里不再詳細描述。

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598921 -

接口

+關注

關注

33文章

8257瀏覽量

149956 -

Xilinx

+關注

關注

70文章

2137瀏覽量

120394 -

仿真

+關注

關注

50文章

3972瀏覽量

132961 -

AXI

+關注

關注

1文章

127瀏覽量

16514

發布評論請先 登錄

相關推薦

Xilinx zynq AXI總線全面解讀

XILINX FPGA IP之Clocking Wizard詳解

AXI VIP當作master時如何使用

Xilinx FPGA片內ROM實例之ROM配置

如何使用Xilinx AXI VIP對自己的設計搭建仿真驗證環境的方法

如何使用Xilinx AXI進行驗證和調試

基于Xilinx FPGA AXI-EMC IP的EMIF通信測試

Xilinx FPGA IP之Block Memory Generator AXI接口說明

Xilinx FPGA IP之Block Memory Generator AXI接口說明

評論