關鍵觀點

MOSFET由門(G)、漏極(D)、源極(S)和體(B)組成,有截止區、線性區和飽和區。

本文摘要

本文介紹了MOSFET的物理實現和操作理論。MOSFET由NMOS和PMOS構成,有截止區、線性區和飽和區。圖示了NMOS和PMOS的物理結構,以及針對不同驅動電壓的電流-電壓曲線。還討論了飽和區的細節,展示了NMOS和PMOS的漏極電流與漏極-源極電壓之間的關系。

晶體管是將輸入電壓轉換為輸出電流(或反之亦然)的器件,使模擬集成電路 (IC) 設計成為可能。如今,模擬 IC 主要使用金屬氧化物半導體場效應晶體管,即 MOS 晶體管或 MOSFET。在本文中,我們將介紹 MOSFET 的物理實現及其工作原理。

MOSFET結構

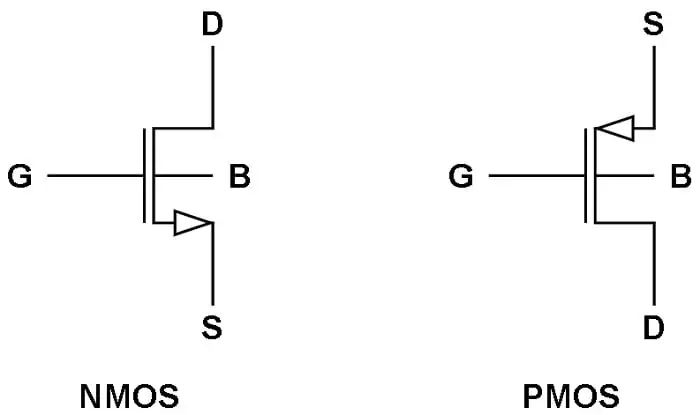

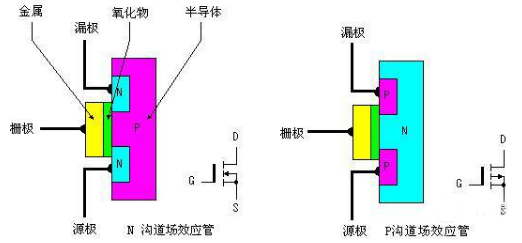

MOS 晶體管是一種四端器件,由柵極 (G)、漏極 (D)、源極 (S) 和體 (B) 組成。圖 1 顯示了兩種類型的 MOS 晶體管:N 溝道 MOSFET (NMOS) 和 P 溝道 MOSFET (PMOS)。一般來說,這兩種通道類型的行為是相反的。

圖 1.NMOS 和 PMOS 原理圖符號。圖片由尼古拉斯·圣約翰提供

輸入電壓連接至柵極端子。電壓電平決定漏極電流,即從漏極流向源極端子的電流。在NMOS晶體管中,漏極的電壓通常高于源極的電壓;PMOS 的情況正好相反。

最后,我們有體端子,它連接到晶體管所在的基板。NMOS 晶體管的體端子連接到電路中盡可能低的電壓(單電源系統中的接地),而 PMOS 體端子連接到最高電壓電平(電路的 VDD)。

在數字電路中,源極和體端子通常連接在一起。因此,您可能會看到示意圖將 MOSFET 顯示為僅具有柵極、源極和漏極的三端器件。

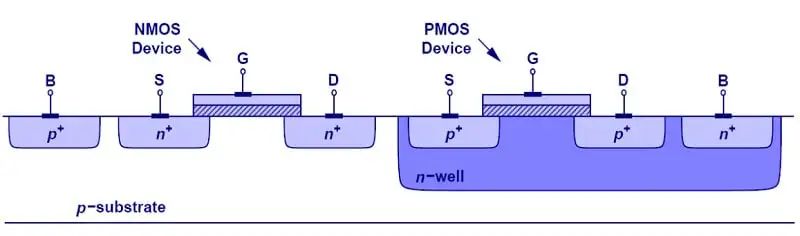

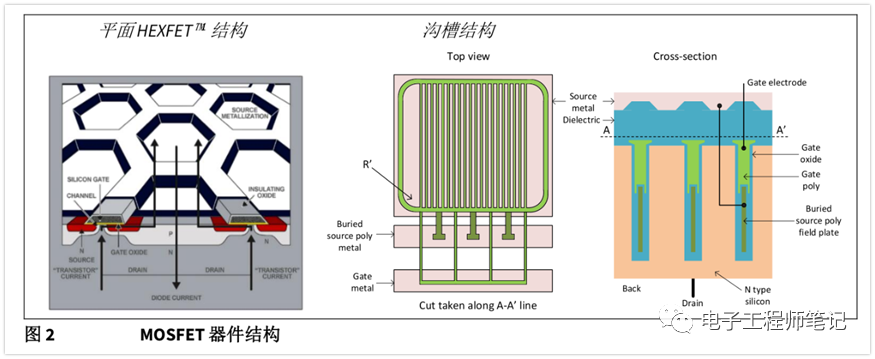

圖 2 比較了左側 NMOS 晶體管與右側 PMOS 晶體管的基本物理結構。兩個晶體管均構建在輕摻雜 P 的硅襯底之上。這對于集成電路內的任何晶體管都是如此。

圖 2.NMOS 和 PMOS 晶體管的物理結構。圖片由UT 達拉斯分校提供

絕緣體(通常是二氧化硅)放置在硅襯底的頂部,并且由多晶硅或金屬制成的柵極端子放置在絕緣體的頂部。這是為了防止從柵極端子到源極、漏極和/或體端子的泄漏。

對于 NMOS,源極端子和漏極端子是通過在襯底內創建高 N 摻雜區域來實現的。請注意,源極端子和漏極端子之間沒有物理差異,因此它們可以互換。這將我們帶到了身體終端。為了提供良好的電連接,它被重摻雜,極性與基板相同。

PMOS器件具有與NMOS相同的結構,但摻雜極性相反。PMOS 主體是整個 P 型襯底內的輕 N 摻雜區域,形成所謂的 N 阱。

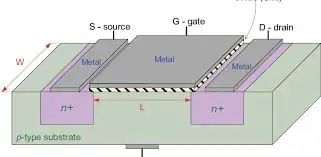

晶體管的寬度 (W) 和長度 (L) 會影響其其他特性。這在二維圖中很難看到,因此我添加了一個顯示三維視圖的圖(圖 3)。

圖 3.三維 NMOS 晶體管結構。圖片由尼古拉斯·圣約翰提供

MOSFET 工作區域

現在我們已經研究了 MOSFET 的基本結構,接下來讓我們深入了解其工作原理。

截止區域

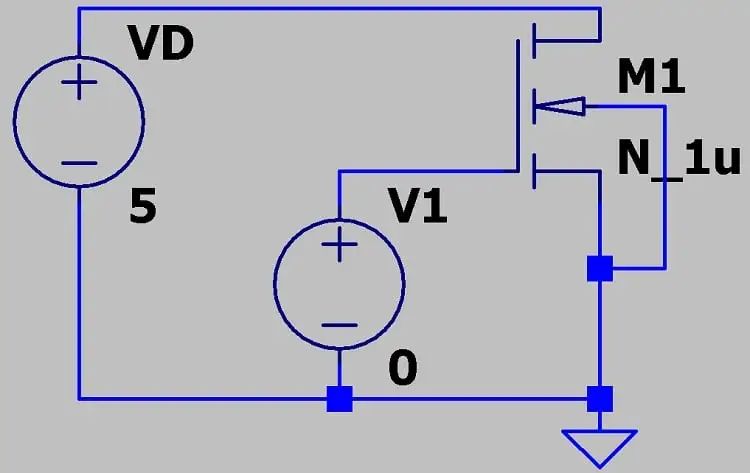

MOSFET 的電氣行為由其四個端子中每個端子的電壓電平決定。對于圖 4 中的 NMOS,柵極和漏極端子連接到獨立的電壓源。源極和主體接地。

圖 4.施加電壓源的 NMOS 晶體管。圖片由尼古拉斯·圣約翰提供

由于 NMOS 是 N 溝道器件,因此只有在源極和漏極之間形成電子溝道(因此為負摻雜)時,它才會傳導電流。當柵極處于 0 V 時,源極和漏極之間沒有溝道,因此沒有電流流動。這稱為截止區域。

隨著柵極電壓 (VGS) 增加,電子被吸引到柵極下方的區域。最終,柵極電壓變得足夠正以形成溝道,并且電流開始從漏極傳導到源極。發生這種情況的電壓稱為閾值電壓(Vth)。圖 5 顯示了漏極電流開始增加的閾值,以及隨后的指數I-V曲線。

圖 5.圖 3 中 NMOS 的漏極電流(y 軸)與柵極電壓(x 軸)。圖片由 Nicholas St. John 提供

VGS必須大于Vth晶體管才能傳導電流。當VGS小于Vth時,晶體管處于截止狀態。

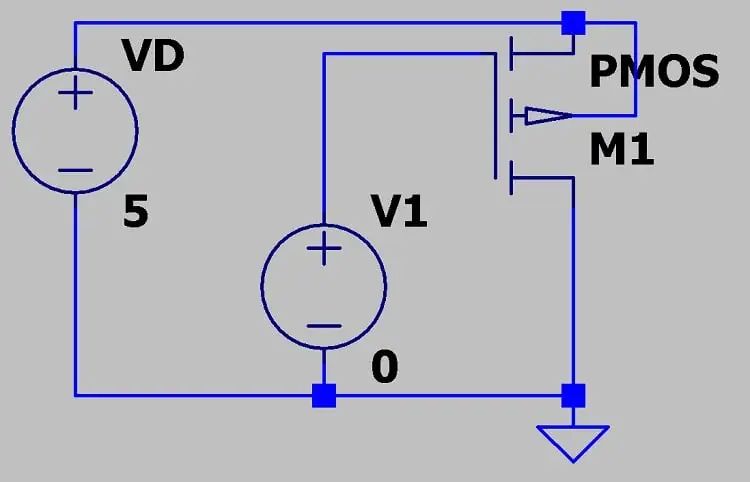

PMOS 晶體管的工作方式相同,只是源極和體與最大電源電壓相關(圖 6)。

圖 6.施加電壓源的 PMOS。圖片由尼古拉斯·圣約翰提供

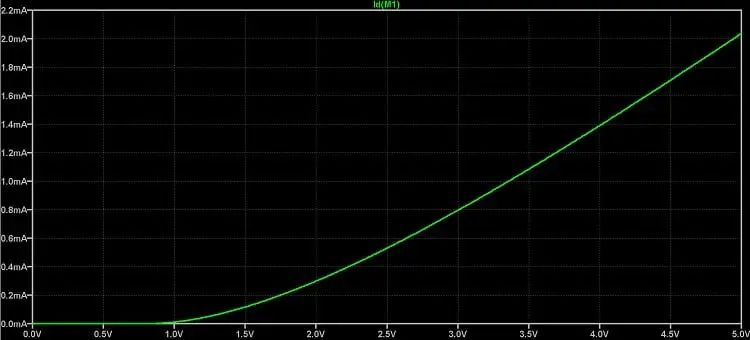

PMOS晶體管的閾值電壓為負。這意味著在晶體管開始導通之前,柵極電壓必須比源極電壓至少低閾值電壓。圖 7 繪制了圖 6 中 PMOS 的柵極電壓和漏極電流。

圖 7.PMOS 晶體管的漏極電流(y 軸)與柵極電壓(x 軸)。圖片由尼古拉斯·圣約翰提供

正如我們所看到的,當 | 時,PMOS 傳導更多電流。VGS|變得大于 |Vth|。

線性區域

現在我們已經介紹了VGS,是時候看看漏源電壓 (VDS) 如何影響晶體管的電氣行為。

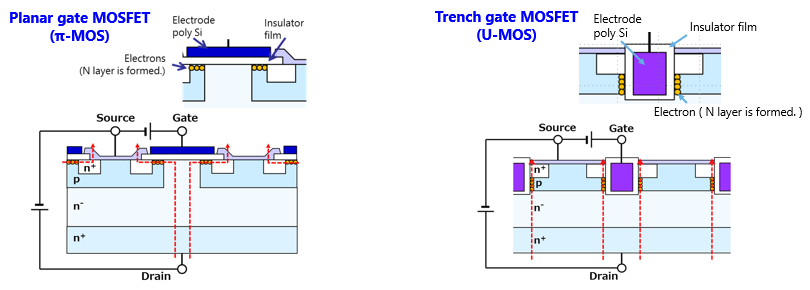

假設我們正在研究一個 NMOS,其中VGS>Vth,這意味著漏極和源極之間有一個電子通道。如果VDS大于0,電流開始流動。漏極電流將與VDS成比例增加,并且晶體管工作在線性區。該區域的其他常見名稱包括三極管、歐姆和有源。

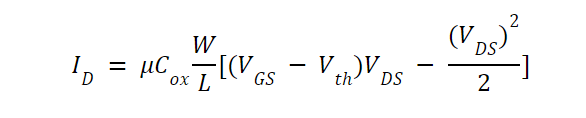

我們可以通過以下公式計算 NMOS 晶體管的漏極電流 (ID ):

等式 1。

在哪里:

μ 是襯底內少數載流子的遷移率

Cox是柵極氧化物的氧化物電容

W/L是晶體管的寬長比。

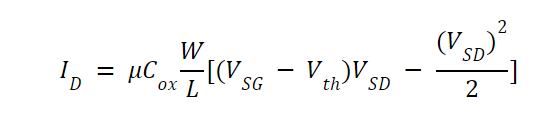

對于 PMOS,方程幾乎相同,但參考電壓被翻轉,μ 現在指的是空穴而不是電子:

等式2。

上述兩個方程均取自 Jacob Baker 博士的《CMOS 電路設計、布局和仿真》。

飽和區

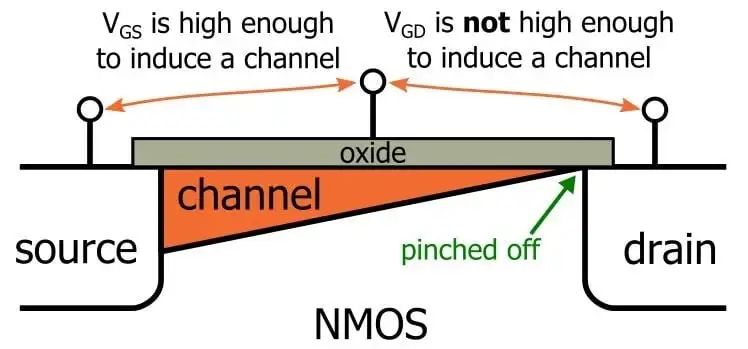

如果漏極電壓繼續增加,最終會達到漏極端子開始夾斷的點,如圖 8 所示。當發生這種情況時,漏極電流將不再像以前那樣快速增加 — 事實上,失去與VDS的所有連接。此時晶體管進入飽和區,模擬 IC 中的 MOSFET 通常在此工作。

圖 8.晶體管中的夾斷。圖片由All About Circuits提供

當 (V_{DS}~=~V_{GS}~-~V_{th}) 時發生夾斷。該值稱為過驅動電壓( V ov )。

該值被稱為voltage(Vov).

理論上,處于飽和狀態的晶體管具有無窮大的阻抗,使其成為出色的電流源。它還具有高電壓電流增益或跨導。

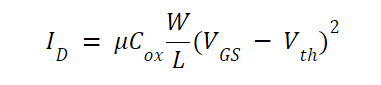

飽和狀態下的漏極電流可以使用平方律方程求得:

等式 3。

從這個方程我們可以看出,一旦晶體管進入飽和狀態,漏極電流就與漏極電壓無關。只需調整VGS和晶體管尺寸即可減少變化并簡化設計。在現實世界中,晶體管的非理想性意味著漏極電壓仍然對漏極電流有一些影響。

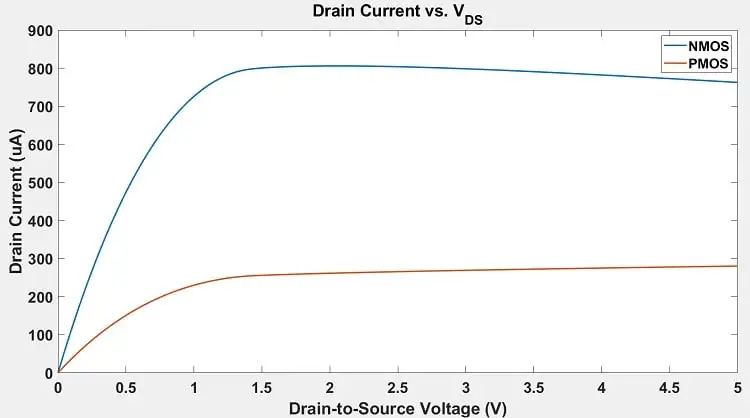

圖 9 顯示了NMOS 和 PMOS 晶體管的晶體管漏極電流與VDS(或VSD )的關系。轉入飽和區的時間約為 1.5 V。請注意,此時漏極電流曲線的斜率均為零。

圖 9.NMOS 和 PMOS 晶體管的漏極電流與VDS的關系。(寬/長)= 10 微米/2 微米。圖片由尼古拉斯·圣約翰提供

即使過驅動電壓和晶體管尺寸相同,NMOS 晶體管電流也比 PMOS 大得多。這是因為硅中空穴的遷移率比電子的遷移率慢得多——前者為450 cm2/V·s,而后者為約 1300 cm2 /V·s。結果是 PMOS 漏極電流低得多。因此,許多互補 MOSFET (CMOS) 設計使用寬長比比 NMOS 晶體管大兩到三倍的 PMOS 晶體管。

審核編輯:湯梓紅

-

集成電路

+關注

關注

5381文章

11385瀏覽量

360858 -

MOSFET

+關注

關注

144文章

7088瀏覽量

212717 -

IC設計

+關注

關注

37文章

1291瀏覽量

103765 -

晶體管

+關注

關注

77文章

9634瀏覽量

137848 -

PMOS

+關注

關注

4文章

244瀏覽量

29488

原文標題:模擬IC設計的MOSFET結構和操作

文章出處:【微信號:moorexuetang,微信公眾號:摩爾學堂】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MOSFET結構和工作原理

MOSFET的基本結構與工作原理

功率場效應管(MOSFET)的結構,工作原理及應用

功率場效應晶體管MOSFET

功率MOSFET的結構和工作原理

功率MOSFET的結構和工作原理簡述

功率MOSFET的結構和工作原理介紹

功率MOSFET的結構與工作原理

MOSFET的結構和工作原理

MOSFET的結構和工作原理

評論