引言:諸如微處理器或系統芯片(SoCs)的敏感負載需要保持穩定的輸入電壓。如果電壓軌有大量的涌流或施加高電容負載,電壓可能會下降,導致設備進入欠壓鎖定(UVLO)/復位狀態或損壞下游電路。PGOOD信號可以通過連接信號到下游負載來幫助管理沖擊電流或控制電源時序,只有當電壓軌達到足以正常運行的值時,才會發出PGOOD。將下游啟用引腳或復位監控器連接到PGOOD,以確保下游負載僅在穩定的輸入電壓下工作,PGOOD功能也適用于功率排序和功率多路復用等應用。

- PGOOD信號的使用方式

連接到下游負載

許多系統正常運行的負載需要穩定的、可調節的功率輸入,如果電源軌失調,可能導致系統故障,一些依賴于穩定的電壓軌的下游負載包括MCU、FPGA、SOC和其它敏感組件。

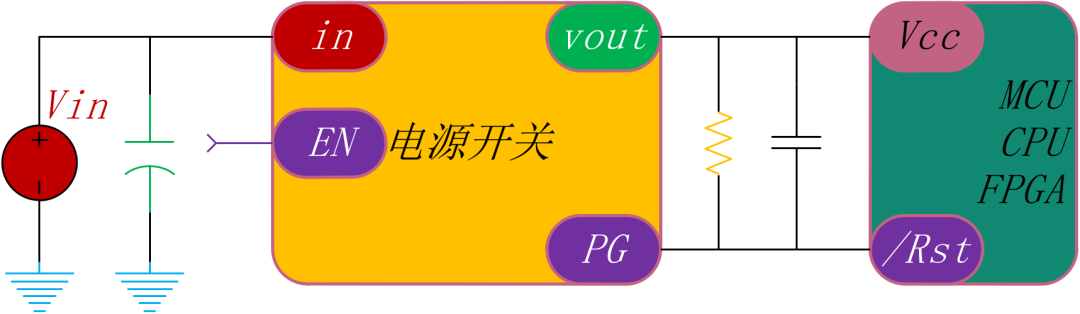

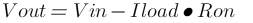

如圖10-1所示,當電源軌打開且穩定時,PGOOD信號可以向MCU提供反饋。如果電源開關的輸出包含高電容性負載,則在輸出電壓穩定時才會打開單片機,浪涌電流可以得到有效控制。換句話說,當PGOOD信號不指示時,單片機將保持關閉狀態。由于PGOOD的輸出通常是開漏,需要一個上拉電阻,以在調節期間將引腳拉高。

圖10-1:電源-PG的復位配置

電源軌邏輯

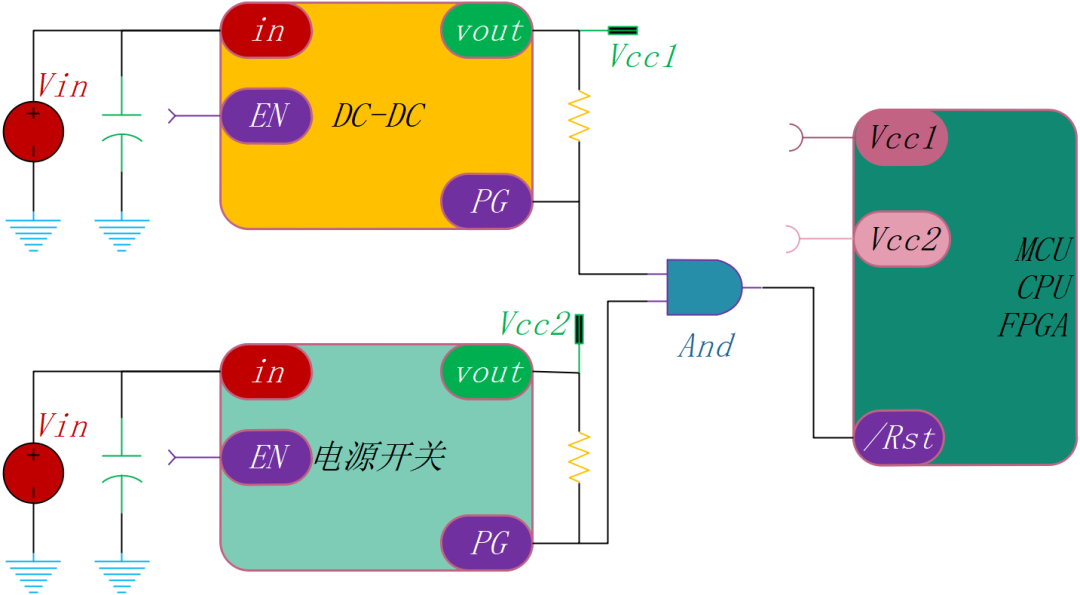

如果多個電源軌需要調節,將PGOOD信號一起連接到重置監控器或IC可確保在任何電源軌超出調節范圍時重置信號有效。圖10-2通過將DC-DC轉換器的PG和電源開關連接在一起演示了這種功能。

圖10-2:多電源PG復位配置

輸入保護

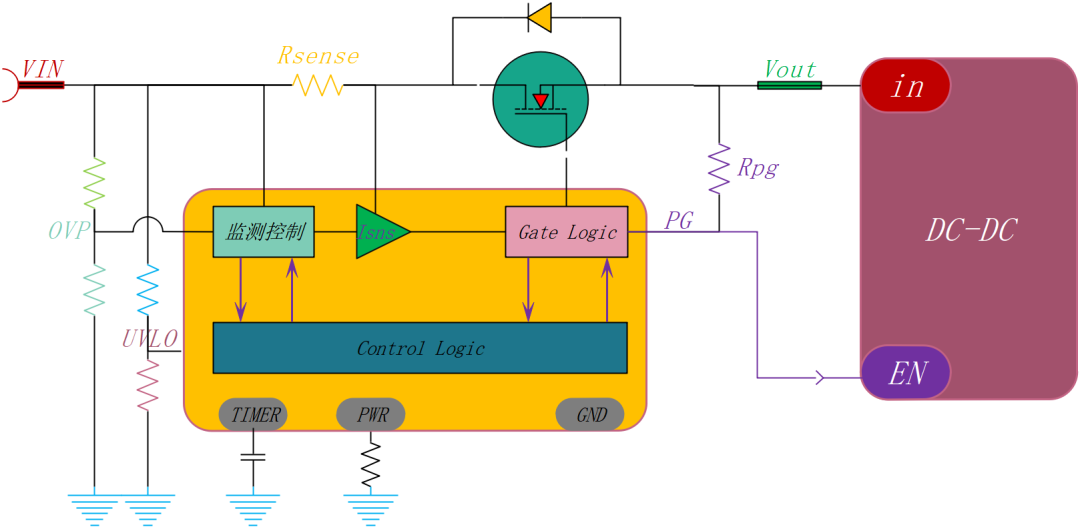

需要魯棒輸入保護的系統可以使用PGOOD信號來減少啟動期間的系統壓力,一些設備,如熱插拔控制器,監測外部FET上的應力,使其保持在安全操作區(SOA)內。在啟動期間使下游負載導通,而FET沒有完全導通可能會在外部FET和系統上增加額外的應力。將PGOOD信號連接到下游負載的使能信號,如圖10-3所示

圖10-3:熱插拔電源-PG的配置

2.電源時序

許多應用需要控制上電和斷電順序來正確操作子系統和下游組件,對于需要按特定順序開啟以確保操作安全性和可靠性的電源軌,排序至關重要。對電源軌進行排序還有助于在通電期間錯開涌入電流,從而減少系統應力和輸入電壓驟降,同時也有助于防止潛在的反向偏置狀況。

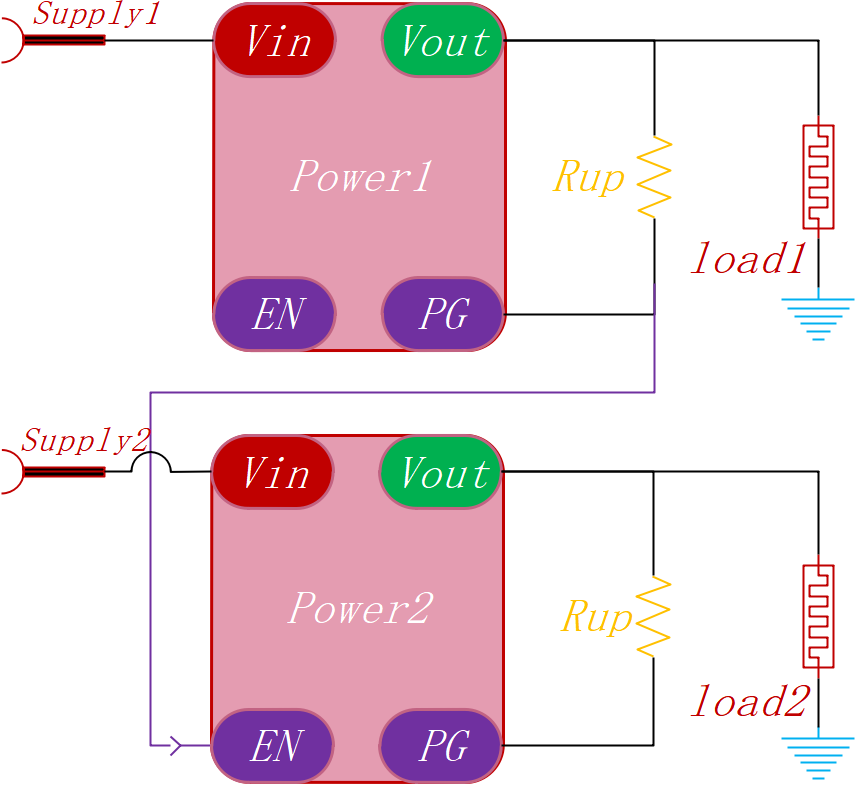

可以使用PGOOD信號對電源軌進行排序,例如,通過將負載開關的PGOOD信號連接到第二負載開關的使能引腳,只有在第一負載開關穩定之后,第二負載切換才會導通。這種情況延遲了第二負載開關的接通,有效地交錯電源軌并降低了系統上的浪涌電流應力。當第一個開關被禁用時,PGOOD信號將EN/ON引腳拉低,并阻止第二個開關接通。

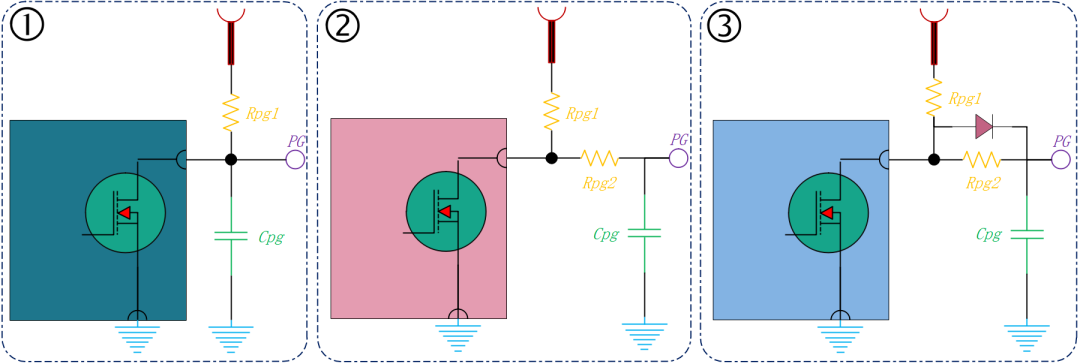

圖10-4展示了一個使用PGOOD的排序應用方式,還可以在PGOOD信號中添加延遲,以進一步延遲電源軌的開啟/關閉,如圖10-5所示。

圖10-4:電源排序

圖10-5:向電源輸出引腳添加延遲

3.電源多路復用

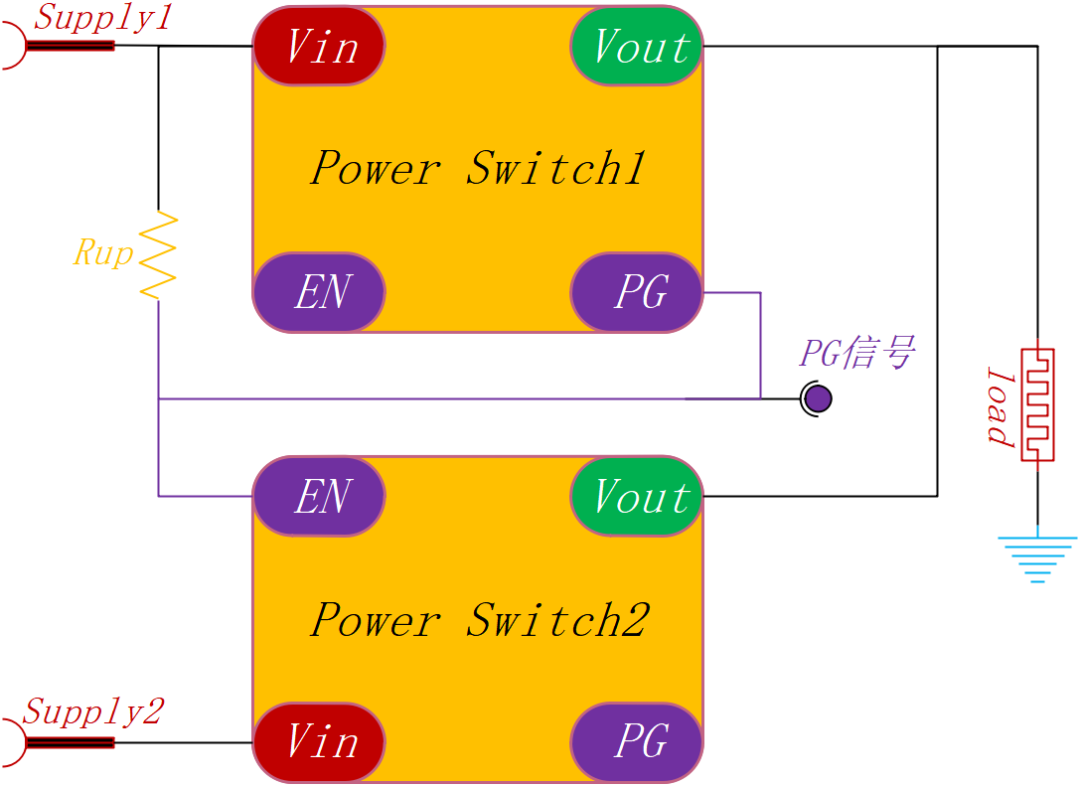

電源多路復用是一組電子開關,用于選擇多個輸入電源軌并將其轉換為單個輸出,包括備用電源軌或備用電池的系統可能需要在電源之間快速切換,以最大限度地減少輸出電壓下降并防止系統重置。為了防止出現反向電流情況,可以使用PGOOD信號切換輸入。

通過將負載開關等器件的PGOOD信號連接到外部P-FET的柵極,PGOOD信號實現了兩個電源軌之間的無縫切換,并消除了對分立時序電路的需要。如圖10-6所示,當PGOOD引腳拉高時,P-FET的柵極也拉高,從而關閉FET,當PGOOD引腳指示為低,P-FET的柵極拉低并導通P-FET時,允許電流從IN2流出。

圖10-6:先通后斷電源多路復用器示意圖

4.PGOOD信號的實現

PGOOD可以分立實現,也可以集成實現。

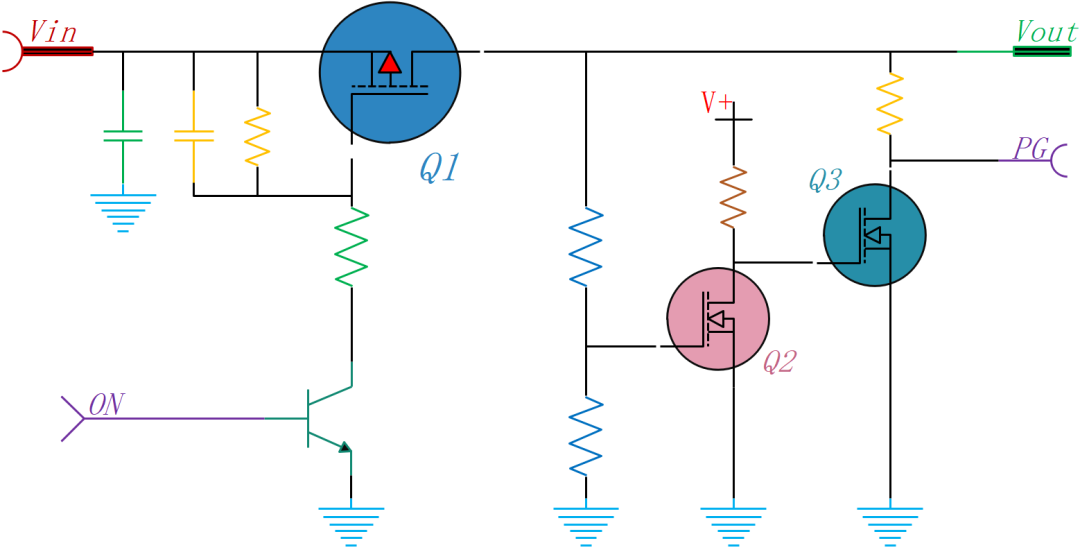

分立的PGOOD

圖10-7顯示了PGOOD信號的分立實現,在該方式中,PGOOD信號取決于輸出電壓。一旦輸出電壓達到某個閾值以偏置分立FET,則PGOOD指示。在這個例子中,當Vout為低時,FET Q2柵極的電壓拉低,使其截止,這使得Q3的柵極被拉高到V+,使其導通,并將PGOOD信號拉到地。當Vout達到電阻分壓器指定的特定電平時,Q2上的柵極指示為高,這將Q3的柵極拉低,從而關斷Q3。這將PGOOD輸出拉高到Vout,從而PGOOD正常指示。

圖10-7:分立的PG結構

該電路的一個限制是PGOOD信號僅受Vout的影響,當存在Vout時,即使Vout電壓軌波動,PGOOD信號也將指示。例如,如果Vout標稱為12V,但高電容負載連接到輸出,則輸入電壓可能下降到10V,只要左FET被偏置,PGOOD信號將保持有效。

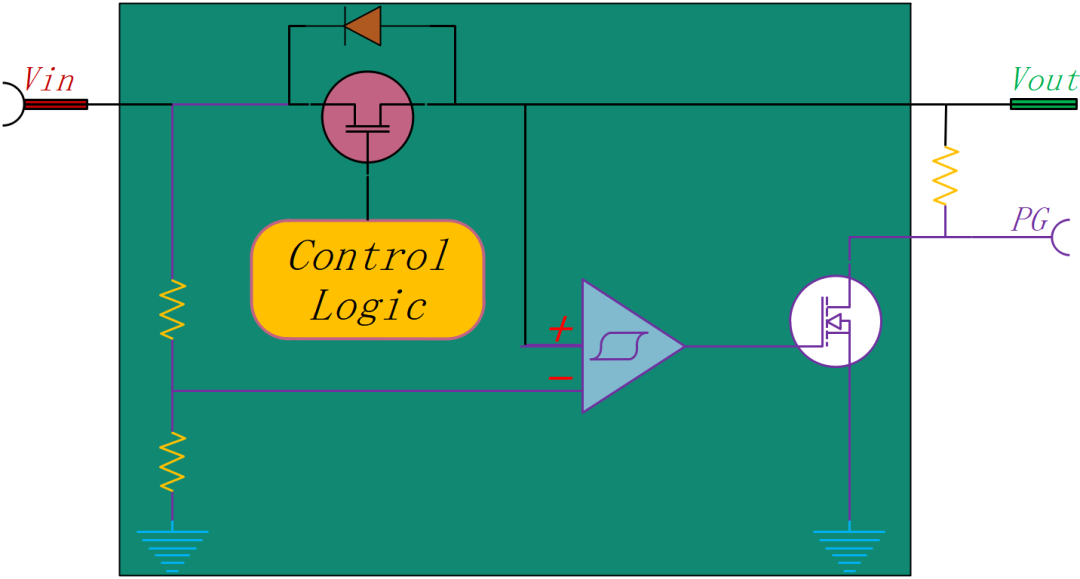

集成的PGOOD

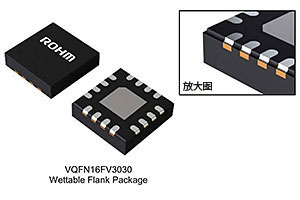

根據設備的不同,有幾種使用集成IC實現PGOOD的方法。第一種方法,Vout/Vin的PGOOD,類似于分立PGOOD的解決方案。如圖10-8所示,當輸出電壓達到Vin的某個百分比時,PGOOD信號生效。對于該示例,一旦Vout達到Vin的90%,PGOOD信號將指示。這是通過Vin和Vout之間的比較提供了PGOOD的簡單功能。

圖10-8:集成的Vout/Vin--PG

但是當接通高電容性負載時,Vout/Vin的PGOOD會受到限制,由于PGOOD信號僅取決于Vin與Vout的比率,因此即使電壓波動,PGOOD也將成立。如果下游負載由于高電容性負載而拉取大量電流,則在啟動期間可能會發生大的浪涌電流事件。對負載電容充電可能導致輸入電壓下降,由于PGOOD最終取決于Vin/Vout比率,因此如果Vin和Vout下降,則PGOOD信號仍將有效。

Vout/Vin的PGOOD在較低電壓應用中也有另一個限制,在較低的Vin下,由于導通電阻,PGOOD信號可能無法指示。例如,如果器件在0.5V、1A、導通電阻為100mΩ的條件下工作,則輸出電壓將為0.4V,這在90%Vin的范圍之外,因此,PGOOD信號可能不會指示。

實現PGOOD的一種有效方法是測量通過FET的導通電阻,這種方法有時被稱為“VGS

GOOD”,當VGS電壓上升到FET導通電阻接近其標稱值時,這種方法會觸發PGOOD。延遲也被引入到電路中,以防止任何瞬態或涌入事件意外地觸發VGS GOOD。在EN/on引腳上的電壓超過器件的VIH電平之后,器件將測量導通電阻并等待一定時間(tBLANK),然后觸發為高電平。如果EN/on引腳上的電壓降至VIL以下,或者FET的VGS降至閾值以下,則PGOOD關閉指示,圖10-9顯示了VGS

GOOD的常見實現方法。

圖10-9:集成的VGS--PG

VGS GOOD提供了在較低Vin值下工作的優點,因為導通狀態電阻波動較小,并防止瞬態或浪涌條件導致PGOOD引腳的意外觸發。VGS GOOD的一個限制是啟動期間的VBIAS和VON,如果VBIAS和VON引腳為高電平,并且Vin開始斜坡上升,則由于VGS閾值保持高電平,PGOOD將被觸發,由于VBIAS為提供給柵極的電壓供電,因此VGS閾值將保持高電平。

5.小結

需要穩定輸入電壓的敏感應用可以使用PGOOD信號來保持電源軌在調節范圍內,PGOOD信號可以幫助管理涌入電流或控制電源軌時序,這在諸如負載工作順序或功率復用之類的應用中是非常有用的。

-

單片機

+關注

關注

6032文章

44516瀏覽量

633019 -

轉換器

+關注

關注

27文章

8627瀏覽量

146869 -

微處理器

+關注

關注

11文章

2247瀏覽量

82314 -

信號

+關注

關注

11文章

2780瀏覽量

76629 -

DC-DC

+關注

關注

30文章

1928瀏覽量

81477

發布評論請先 登錄

相關推薦

ADC Input Noise: The Good,The

TPS3510 TPS2511 PC POWER SUPPL

TPS77215,pdf(Power Good Output

TPS77150,pdf(Power Good Output 150-mA LDO Regulator)

TPS77115,pdf(Power Good Output

TPS77227,pdf(Power Good Output

TPS77201,pdf(Power Good Output

TPS77128,pdf(Power Good Output

TPS77127,pdf(Power Good Output

用于信號調理的微電路

LT8709 Demo Circuit - Negative Inverting Regulator with Output Current Monitor & Power Good (-4.5V to -42Vin to 5V @ 4A)

BD9S系列: 配置Power Good功能的車載ADAS用超小型降壓DC/DC轉換器

Power Good信號的使用方式

Power Good信號的使用方式

評論