在進行模塊設計時,我們經常需要統計報文的數量,以供軟件(or 主機)讀取,有些統計僅僅用于debug,有些統計是協議要求,有些統計是為了便于功能實現。 當需要統計的數量較多時,為了降低功耗和減少面積,我們通常采用RAM去實現。

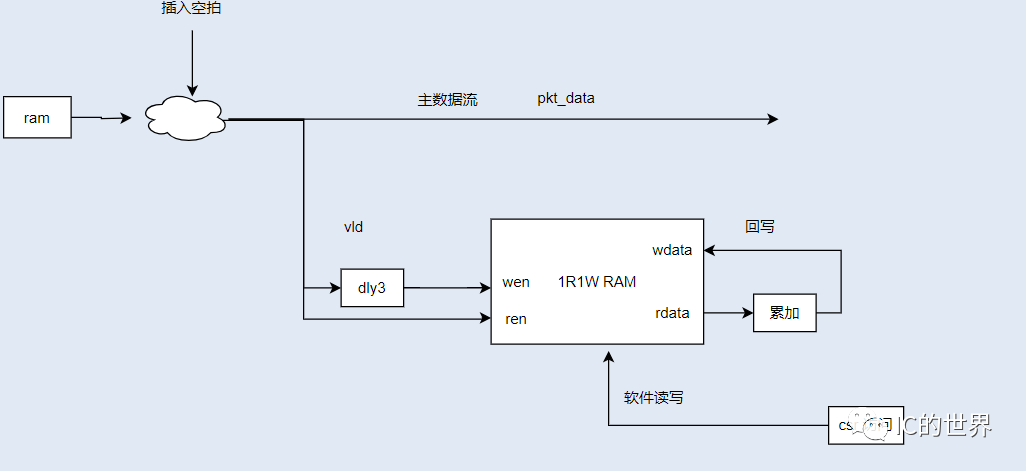

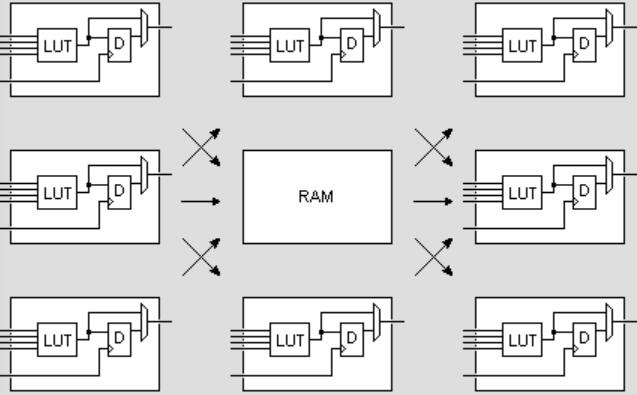

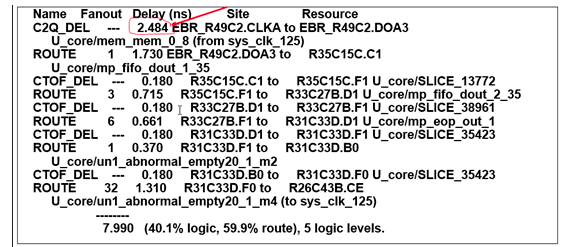

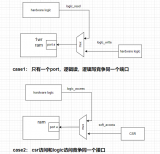

如下案例中,統計有效數據包的個數。 假設數據中存在pkt_id,pkt_id為0~63,則ram的深度為64。pkt_id用于作為讀寫地址。RAM讀延時為3個時鐘周期。 有數據來臨時,pkt_vld作為讀使能,讀出當前包計數rdata,三個周期后,rdata加1回寫到ram。 如下圖所示:需要有三個注意事項 NOTE1:需要有讀寫保護,因為可能出現連續4個周期內,pkt_vld為1,且pkt_id相同,此時會出現同一個周期對相同的地址進行讀寫,因此需要RAM需要添加讀寫保護模塊,保證數據能夠正確寫入,且讀出的都是最新值,否則就會出現統計錯誤。 NOTE2:圖中既有軟件讀、又存在硬件讀,且硬件讀優先級更高,軟件讀優先級低,因此為了保證軟件讀能夠在有效周期內得到響應,因此需要在主數據流上插入空拍,避免出現軟件讀長時間無法響應而產生超時。

編輯:黃飛

-

IC設計

+關注

關注

37文章

1291瀏覽量

103768 -

RAM

+關注

關注

8文章

1367瀏覽量

114531 -

讀寫保護

+關注

關注

0文章

4瀏覽量

5865

原文標題:IC設計:ram的應用 - 統計計數

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于QMSS中link ram的地址問題

關于Ram on Net的設想

屏幕自動刷新RAM和負液晶技術的介紹

詳細介紹關于FPGA開發板內部ram是如何操作的

關于Block RAM的寄存器輸出

在STVDCOSMIC在RAM中運行代碼stm8 ram中運行程序

關于RAM以及單片機內存少的幾點內容

關于dsp28035的adc在ram中運行和rom中運行的問題

IC設計中關于ram的應用

IC設計中關于ram的應用

評論