ShareMemory,顧名思義就是共享內(nèi)存。這個概念在很多計算機系統(tǒng)中都存在,本文特指 EC SRAM 映射到 CPU Memory 空間的共享內(nèi)存設(shè)計。

01—ShareMemory 簡介

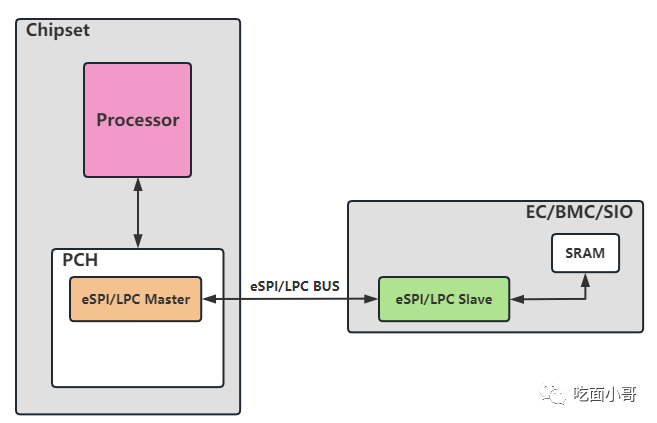

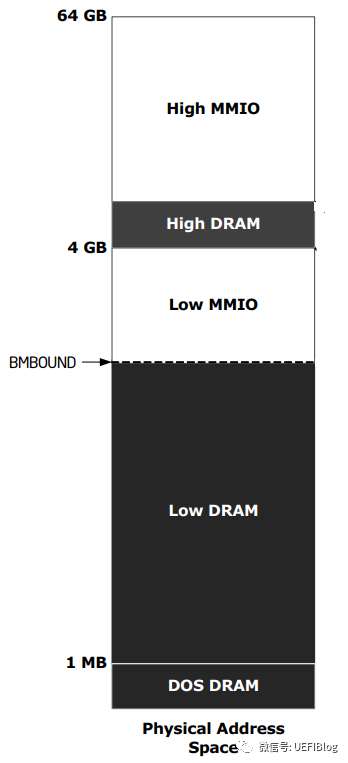

此處的 ShareMemory 特指,在 EC 和 CPU(x86/ARM) 通過 eSPI/LPC 總線連接的系統(tǒng)中,EC SRAM 映射到 Host Memory 空間。當 Host 端需要訪問 EC SRAM 時,就和訪問 Host 的 Memory 一樣簡便。

ShareMemory 的設(shè)計極大提高了CPU 和 EC 之間的數(shù)據(jù)傳輸效率。

eSPI/LPC 的 Master Controller,一般作為一個 PCI 設(shè)備存在。因此可以通過修改 eSPI/LPC Controller 的 PCI 配置空間寄存器將指定的 IO 空間和 Memory 空間等資源分配給 eSPI/LPC Master Controller。

當 OS 或者應用軟件通過 CPU 指令訪問指定 IO端口,或者訪問指定 Memory 地址時,訪問操作會被轉(zhuǎn)發(fā)至 eSPI/LPC 的

Controller。最終由 eSPI/LPC Controller

生成通訊協(xié)議發(fā)送給 eSPI/LPC 總線上連接的從設(shè)備,如下圖所示。

eSPI/LPC Slave 一般有 EC、BMC、SIO 等。以EC 為例,當從設(shè)備接到 eSPI/LPC 總線上的 Memory Cycle后,eSPI/LPC Slave Controller 就會解碼 Memory 地址。

如果發(fā)現(xiàn)該地址在配置的Memory 空間內(nèi),eSPI/LPC Slave Controller 就會把數(shù)據(jù)寫入指定的 SRAM,或者將指定SRAM 的值返回。如此就完成了 EC SRAM 映射到 CPU Memory 空間,這就是 EC ShareMemory 實現(xiàn)的原理。

02—CPU 端的配置

由于設(shè)計上的差異,不同 CPU 針對

ShareMemory 的配置有所不同。

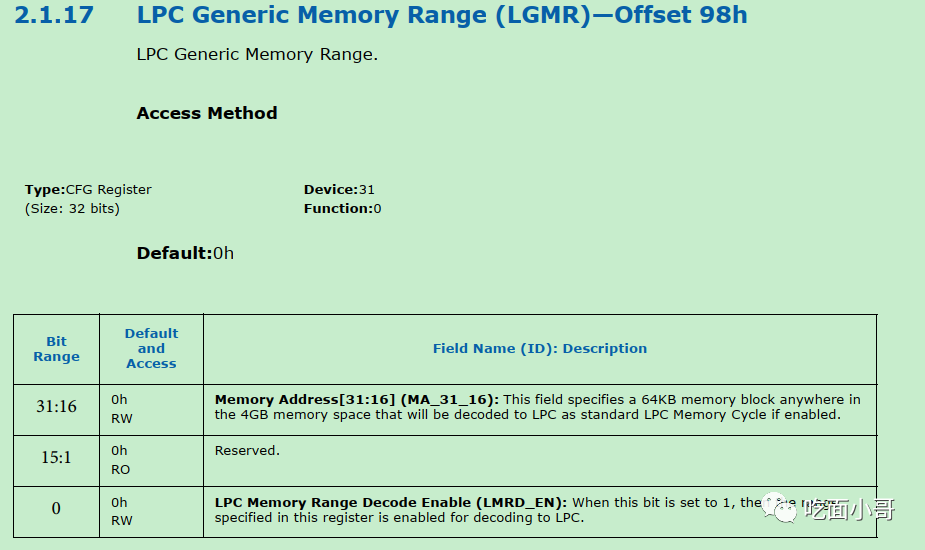

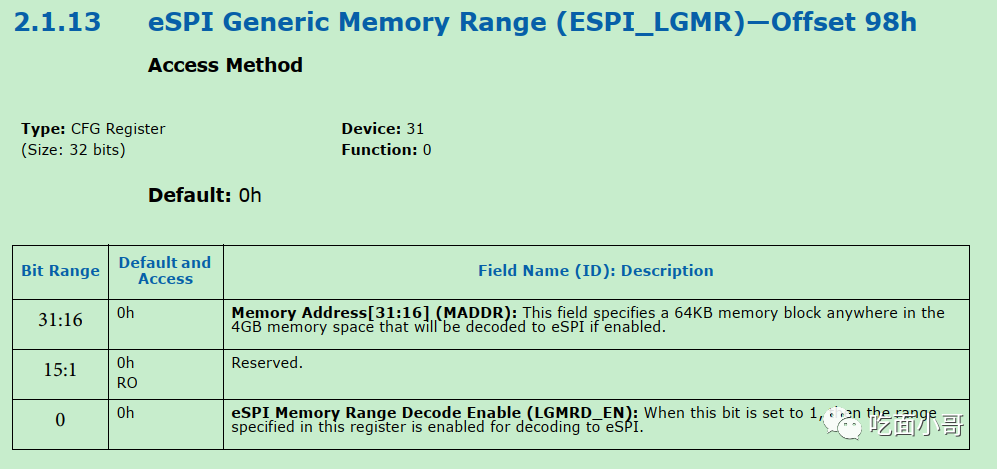

x86 Intel 平臺

在 Intel 平臺上,eSPI 和 LPC Controller 都是作為一個 PCI 設(shè)備存在,兩個控制器的 PCI 設(shè)備號一致,都是B0:D31:F0,實際使

用時二選一。

如下圖所示,配置 Offset 98h 寄存器,即可把 CPU 的指定Memory 空間分配給

eSPI/LPC Master Controller。

x86 AMD 平臺

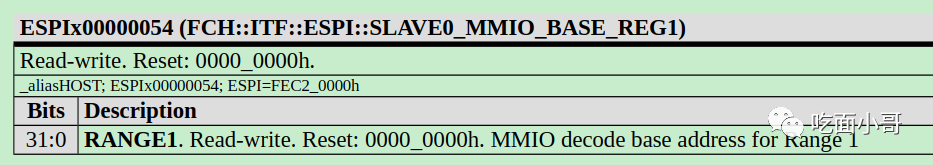

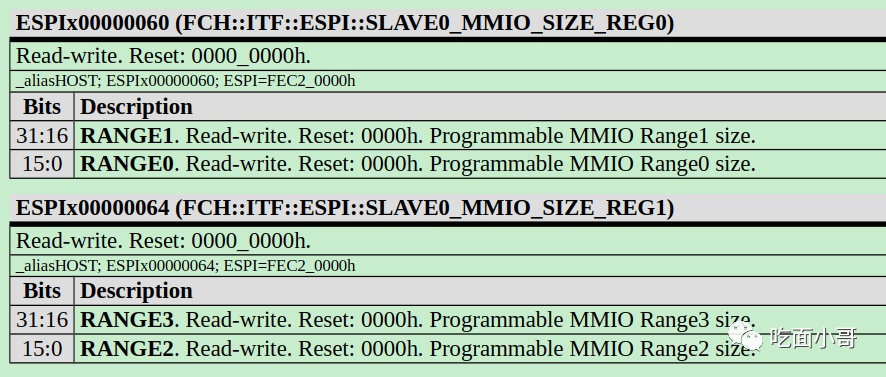

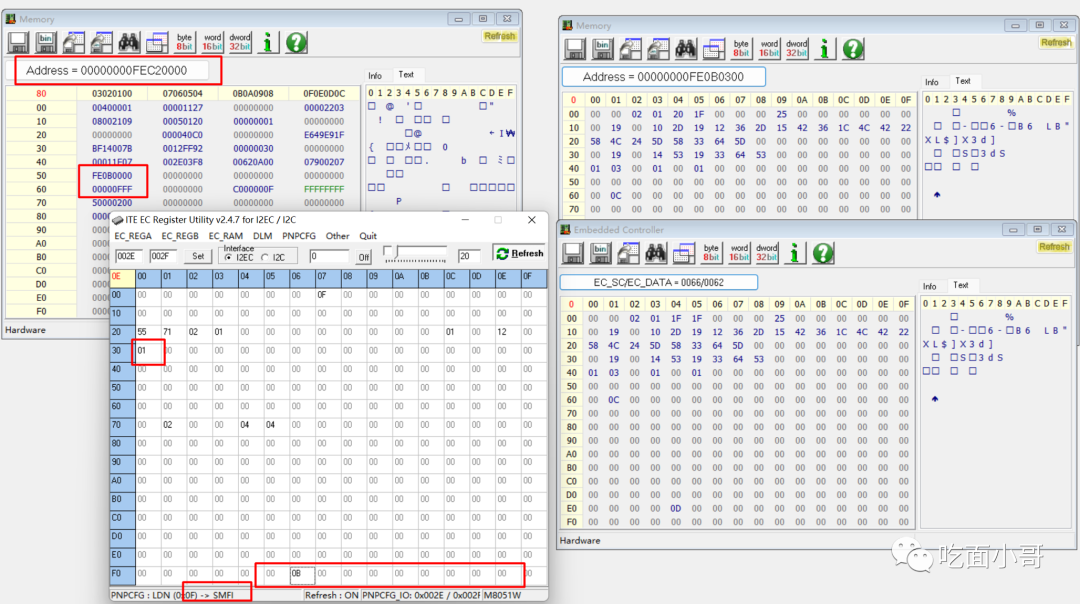

在 AMD 平臺上 eSPI 的配置寄存器先被映射到指定的 Memory 空間。配置eSPI MMIO 寄存器即可把指定的CPU Memory 空間分配給 eSPI 控制器。eSPI 配置空間基地址為 0xFEC2_0000,MMIO 基地址配置寄存器為 Offset 50/54/58/5C,長度配置寄存器為 Offset 60/64。

注意 : 此處的寄存器配置后直接生效。

ARM Phytium 平臺

飛騰平臺上的 LPC Controller 作為一個外設(shè)存在,支持 DMA模式、IO模式、

Memory模式、FirmwareMemory 模式。

由寄存器 INT_APB_SPCE_CONF 配置,每個模塊占用Memory 空間大小為 32M。

如下表格所示訪問 CPU Memory 空間 0x20000062,會發(fā)起 LPC 的 IO Cycle(IO Port 62)。

訪問 CPU Memory 空間 0x22000000,

會發(fā)起 LPC 的 Memory Cycle。

LPC Controller 的 CPU Memory 資源劃分如下:

| 模塊 | 基地址 |

|---|---|

| IO | 0x20000000 |

| Memory | 0x22000000 |

| FirmwareMemory | 0x24000000 |

| DMA | 0x26000000 |

其他 CPU 平臺

eSPI/LPC Master Controller 的資源分配方法在不同的 CPU 平臺上都不一樣,需要

根據(jù) CPU 指導手冊完成配置。

03—EC 端的配置

EC 的硬件設(shè)計中,一般有個

ShareMemory Controller,作為一個SIO設(shè)備存在,負責處理 eSPI/LPC 總線上的 Memory Cycle。

EC 端有如下兩個參數(shù)需要配置:

第一,指定可識別的 Host 端的Memory 基地址。這就指明了 EC 可解碼的

Host Memory 起始地址。配置寄存器一般位于 SIO 配置空間。

第二,指定EC端匹配的 SRAM 基地址和長度。這就指明了 EC 端的某段

SRAM 空間被映射到 Host Memory 空間。配置寄存器一般位于 EC 的

ShareMemory Controller 內(nèi)。

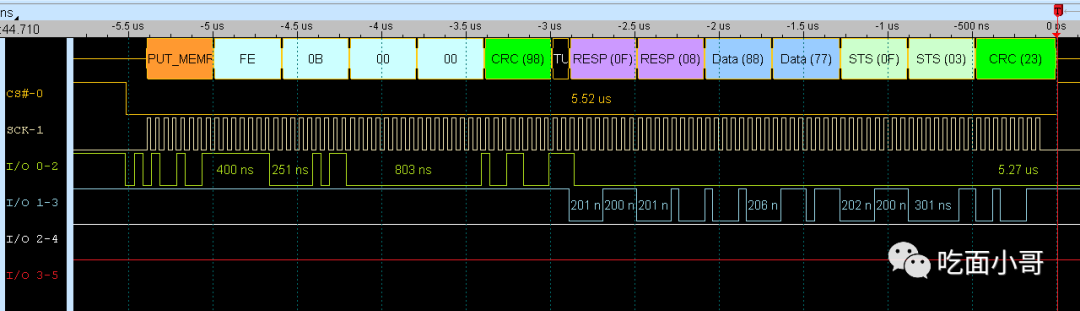

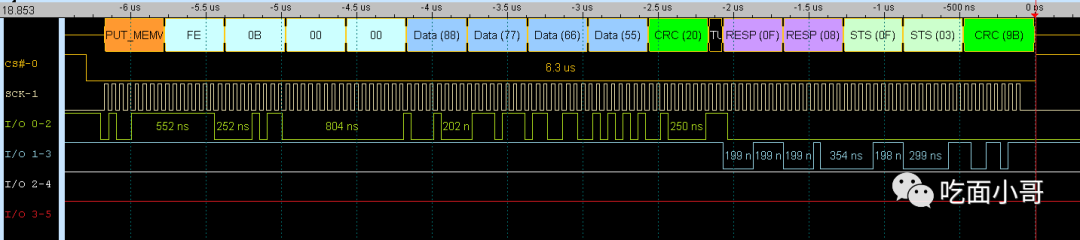

上述2個配置參數(shù)的配置方法以及寄存器位置,查閱對應 EC 芯片的用戶手冊即可獲取。如下圖所示,是基于 eSPI 總線實現(xiàn)

ShareMemory 訪問功能后,Host 讀寫

EC SRAM 的通訊波形。

EC 端和 CPU 端都完成相應配置后,在OS 下訪問 Memory 即可訪問到指定的 EC SRAM 存儲區(qū)間。

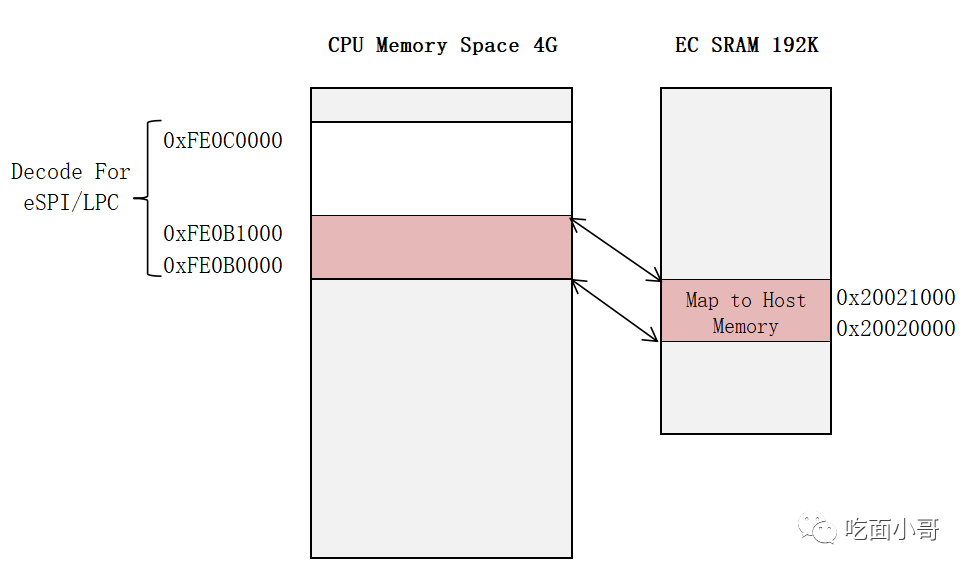

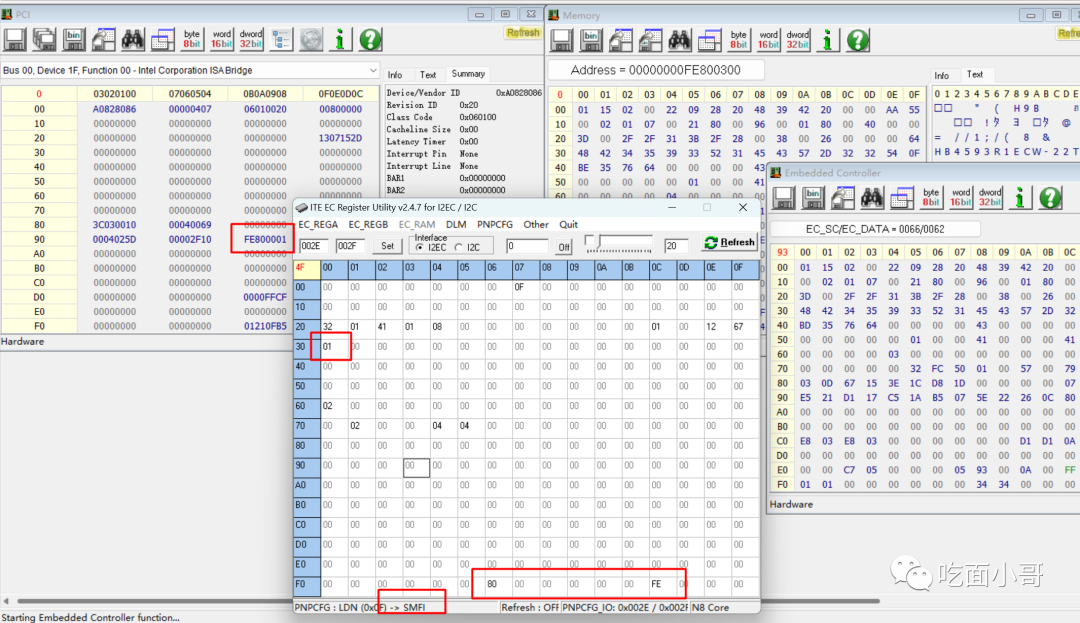

下圖 Intel ADL 平臺和 EC 的配置結(jié)果,最終實現(xiàn)了 EC SRAM 0x300映射到

Host Memory 空間的 0xFE800300 位置。

下圖是 AMD Ryzen7840 平臺和 EC 配置結(jié)果,最終實現(xiàn)了 EC

SRAM 0x300 映射到 Host Memory 空間的 0xFE0B0300 位置。

04—ShareMemory 的應用

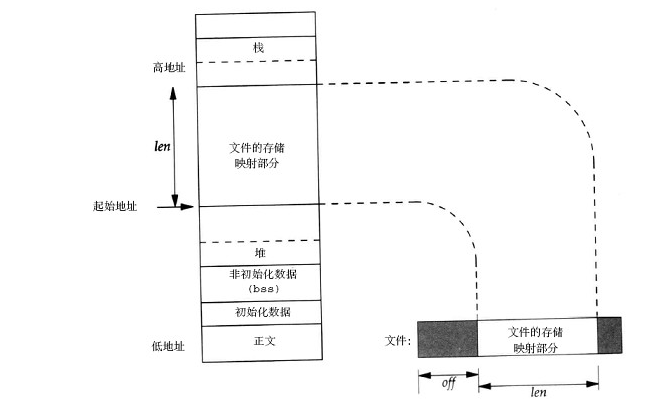

ShareMemory 的目的就是把 EC 的 SRAM 存儲映射到 CPU Memory 空間,如此 CPU 就可以快速完成大量的 EC 數(shù)據(jù)訪問。使用 EC 端提供的

ShareMemory Semaphore,Host 訪問完 EC SRAM 還可以通知 EC 內(nèi)核。

ACPI 規(guī)范定義的 ECI 也可以訪問 EC SRAM,但是涉及到狀態(tài)位的等待同步,訪問速度沒有 ShareMemory 快。

因此 Host 和 EC 之間有大量數(shù)據(jù)需要傳遞的時候,ShareMemory 就是第一方案。當然EC SRAM也可以映射到 CPU的 IO 空間,實現(xiàn)原理一樣。只是方向 CPU IO端口,最終會在eSPI/LPC 總線上發(fā)起 IO Cycle,EC端接到后按映射關(guān)系轉(zhuǎn)換為 SRAM的訪問即可。

-

ARM

+關(guān)注

關(guān)注

134文章

8967瀏覽量

365038 -

cpu

+關(guān)注

關(guān)注

68文章

10702瀏覽量

209371 -

sram

+關(guān)注

關(guān)注

6文章

757瀏覽量

114450 -

計算機

+關(guān)注

關(guān)注

19文章

7174瀏覽量

87157 -

共享內(nèi)存

+關(guān)注

關(guān)注

0文章

16瀏覽量

8294

發(fā)布評論請先 登錄

相關(guān)推薦

如何將共享代碼映射到DSPR5以及將其映射到其他RAM區(qū)域?

Linux的mmap文件內(nèi)存映射機制

請問如何在platform文件中實現(xiàn)將msmc映射到0xa0000000起始的地址空間中?

mmap()函數(shù)映射到內(nèi)存中出現(xiàn)bus error的錯誤

為何啟動模式為SRAM時0x20000000不會映射到0x00000000 ?

使用UARTLite IP如何找到內(nèi)存映射IO方法

linux如何共享內(nèi)存實驗

地址總線是要映射到FPGA的內(nèi)部還是直接ARM的內(nèi)存空間

STM32G0將地址0x00000000重新映射到SRAM不起作用咋辦

ESP32-D0WDR2-V3帶外接flash和emmc,外部閃存將無法將內(nèi)存映射到cpu內(nèi)存空間是怎么回事?

世上最好的共享內(nèi)存(Linux共享內(nèi)存最透徹的一篇)上集

深入剖析Linux共享內(nèi)存原理

內(nèi)存是怎么映射到物理地址空間的?內(nèi)存是連續(xù)分布的嗎?

EC SRAM映射到CPU Memory空間的共享內(nèi)存設(shè)計

EC SRAM映射到CPU Memory空間的共享內(nèi)存設(shè)計

評論