eSPI 協(xié)議在物理層是遵循 SPI 通訊規(guī)范的,但是協(xié)議層有差異,因此不能使用 SPI 協(xié)議去解析(沒(méi)有 eSPI 協(xié)議分析儀的情況下,可以使用 SPI 協(xié)議分析儀去做單獨(dú) Byte 的初步解析,接下來(lái)就人肉解析 eSPI)。

一般邏輯分析儀只能解析 I2C、SPI 等通用協(xié)議。要分析 eSPI 協(xié)議必須使用可以解析 eSPI 協(xié)議的邏輯分析儀 Acute TravelLogic。

目前市場(chǎng)上常用的 eSPI 分析儀如下圖,型號(hào)是 TL4234B。

下載邏輯分析儀軟件

打開(kāi)官網(wǎng)鏈接,下載配套軟件并且安裝,如下圖。

軟件設(shè)置

打開(kāi)軟件后,如下圖,選擇邏輯分析儀。

抓取 eSPI 波形,可以采用快速通道配置。點(diǎn)擊快速設(shè)置,選擇 eSPI 協(xié)議。

點(diǎn)擊下圖,配置按鈕,可以配置 eSPI Bus 采集的參數(shù)。

通道設(shè)置

通道配置中,channel 默認(rèn)從 0 開(kāi)始,一共占用 7 個(gè) channel。依次為 CS#、SCK、IO-0、IO-1、IO-2、IO-3、Alert、Reset。

事實(shí)上,使用 signal IO Mode 時(shí),Alert 是復(fù)用在 IO-1上,因此沒(méi)有實(shí)際的 Alert pin。

CS 工作模式選擇 Active Low,即低電平選擇。

Response 采樣點(diǎn)選擇 Clock Rising,即上升沿采樣。

IO Mode 默認(rèn) signal mode 即可。

解碼顯示設(shè)置

解碼顯示設(shè)置中,選擇需要顯示的內(nèi)容即可。

硬件連線

筆記本設(shè)計(jì)中,采用的是 Signal Master - Signal Slave 模式,Master 是 PCH,Slave 是 EC。

如下圖,IO 有 4個(gè),分別是 IO-0,IO-1,IO-2,IO-3。實(shí)際應(yīng)用中通訊模式選擇 Signal Mode居多。

如果通訊模式是 Signal Mode,邏輯分析儀可以不抓取 IO-2,IO-3 信號(hào)。

按上述軟件配置,邏輯分析儀的 CH[0--7] 分別接硬件的 CS#、CLK、I/O 0、I/O 1、I/O 2、I/O 3、Alert、Reset#。

同時(shí)記得連接一個(gè)地線。

抓取 eSPI 波形

點(diǎn)擊采集,即可開(kāi)啟捕獲波形。捕獲完成后,軟件自動(dòng)解析,黑色區(qū)域顯示具體波形,底下框中顯示每一筆數(shù)據(jù)包的詳情。

持續(xù)抓取 eSPI 波形

eSPI 數(shù)據(jù)包

筆記本的 eSPI 的應(yīng)用中,是 Signal Master - Signal Slave,即一主一從。

PCH 作為 eSPI Master,當(dāng) EC 把 RSMRSET 拉高后,PCH 拉高 eSPI Reset,開(kāi)始做 eSPI 的初始化。

主要內(nèi)容有通訊速率、通訊模式、通訊通道等信息配置。

eSPI 初始化數(shù)據(jù)包

PCH 端的 eSPI Master 對(duì) EC 端的 eSPI Slave 初始化,其實(shí)就是根據(jù)實(shí)際需求,改寫(xiě) eSPI Slave Register。

使用到的指令是 GET_CONFIGURATION 和 SET_CONFIGURATION。

所以基本邏輯就是 eSPI Master 讀取 eSPI Slave 寄存器,改寫(xiě)寄存器,回讀確認(rèn)。寄存器操作最小單位是 4Byte。

eSPI Slave 端需要配置的寄存器只有如下 5個(gè),即 Offset 08、10、20、30、40。

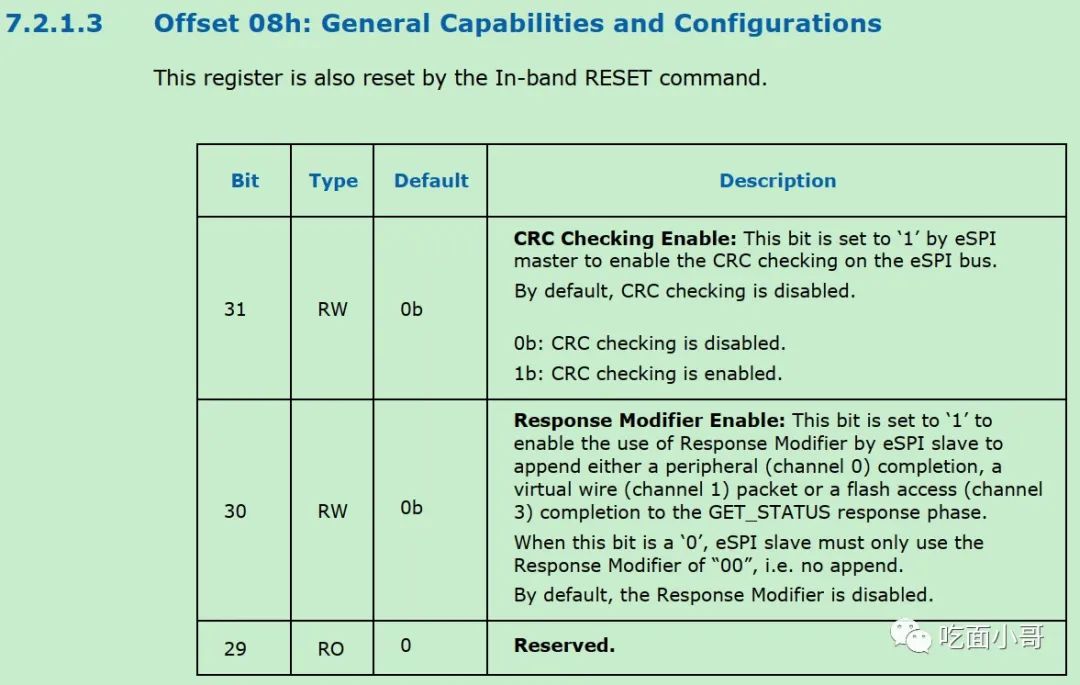

Offset 08h: General Capabilities and Configurations

通用功能描述和配置寄存器。包括通訊速率、模式、校驗(yàn)使能,通道支持。

讀取 offset 08h 寄存器

改寫(xiě) offset 08h 寄存器

eSPI Master 選擇 Quad I/O mode,66MHz 通訊。下圖可以明顯看到改寫(xiě) 08 寄存器后,CLK 變快,I/O[2-3] 參與通訊。

Offset 10h: Channel 0 Capabilities and Configurations

通道 0 功能描述和配置寄存器。 Peripheral Channel 。

寫(xiě) offset 10h 寄存器,使能 Peripheral Channel。

Offset 20h: Channel 1 Capabilities and Configurations

通道 1 功能描述和配置寄存器。 Virtual Wire Channel 。

讀取 offset 20h 寄存器

寫(xiě) offset 20h 寄存器,使能 Virtual Channel。

Offset 30h: Channel 2 Capabilities and Configurations

通道 2 功能描述和配置寄存器。 OOB Message Channel 。

讀取 offset 30h 寄存器

寫(xiě) offset 30h 寄存器,使能 OOB Message Channel。

Offset 40h: Channel 3 Capabilities and Configurations

通道 3 功能描述和配置寄存器。 Flash Access Channel 。

寫(xiě) offset 40h 寄存器,使能 Flash Access Channel。

PCH SLP Signal 數(shù)據(jù)包

PCH 端的 eSPI Master 使用 PUT_VWIRE 指令把 SLP 信號(hào)傳遞給 EC。

Index = 0x02,代表 System Event 2。

Data = 0x76,代表 SLP_S5、SLP_S4、SLP_S3 信號(hào)有效,其中 SLP_S5、SLP_S4 為 High,SLP_S3 為 Low。

EC 端的 eSPI Slave 有 Virtual Wire 信號(hào)發(fā)送時(shí),會(huì)先在 I/O[1] 上產(chǎn)生一個(gè) Alert#,然后 Host 使用 GET_VWIRE 獲取 Virtual Wire 狀態(tài)。

KBC 數(shù)據(jù)包

按下 “A” 鍵后松開(kāi)。有按鍵觸發(fā)后,KBC 端需要主動(dòng)發(fā)送 IRQ 并且發(fā)送 Key Code(Make and Release)。

EC 端的 KBC 有數(shù)據(jù)需要發(fā)送給 Host,需要用 Virtual Wire 發(fā)送一個(gè) SERIRQ。

Host 讀取 Virtual Wire,返回值是 Index=0x00,Data=0x81。

Index = 0x00,代表 Interrupt Event 0。

Data = 0x81,BIT-7 為 1 代表 Interrupt Level High。BIT[0-6] 為 1 代表 IRQ-1。

Host 端發(fā)收到 IRQ-1,讀取 I/O 64 判斷 OBF 是否為 1,即 KBC 端是否已經(jīng)準(zhǔn)備好數(shù)據(jù)。然后讀取 I/O 60 獲取數(shù)據(jù)(1E,即 “A” 鍵 Scan Code Set-1)。

Host 讀取完“Key Code”,緊接著讀取 Virtual Wire 狀態(tài),發(fā)現(xiàn) IRQ-1 變?yōu)?Low。因此 KBC 的 IRQ-1 是高電平觸發(fā)。

-

SPI

+關(guān)注

關(guān)注

17文章

1663瀏覽量

90708 -

波形

+關(guān)注

關(guān)注

3文章

374瀏覽量

31376 -

邏輯分析儀

+關(guān)注

關(guān)注

3文章

212瀏覽量

23048 -

SPI協(xié)議

+關(guān)注

關(guān)注

0文章

18瀏覽量

8335

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

常見(jiàn)eSPI通訊數(shù)據(jù)包的分析

加密后抓包分析的問(wèn)題?

空口抓包方式和wireshank分析工具使用介紹

請(qǐng)問(wèn)BLE-Dongle是否支持抓包協(xié)議分析?請(qǐng)問(wèn)怎么進(jìn)行抓包協(xié)議分析?

使用wireshark抓包分析TCP及UDP的資料詳細(xì)說(shuō)明

Wireshark數(shù)據(jù)抓包網(wǎng)絡(luò)協(xié)議的分析

最新PCIe Gen 5 switch芯片已內(nèi)置SerialTek PCIe抓包分析功能

Wireshark從入門(mén)到精通之網(wǎng)絡(luò)抓包協(xié)議分析必備

802.11抓包軟件對(duì)比之Microsoft Network Monitor

SRT協(xié)議的工作流程、數(shù)據(jù)包結(jié)構(gòu)及Wireshark抓包分析

【RT-Thread學(xué)習(xí)筆記】好用高性價(jià)比的BLE藍(lán)牙抓包器

詳細(xì)的Wireshark的抓包和分析

如何抓取app數(shù)據(jù)包 網(wǎng)絡(luò)抓包原理及實(shí)現(xiàn)

eSPI協(xié)議抓包分析

eSPI協(xié)議抓包分析

評(píng)論