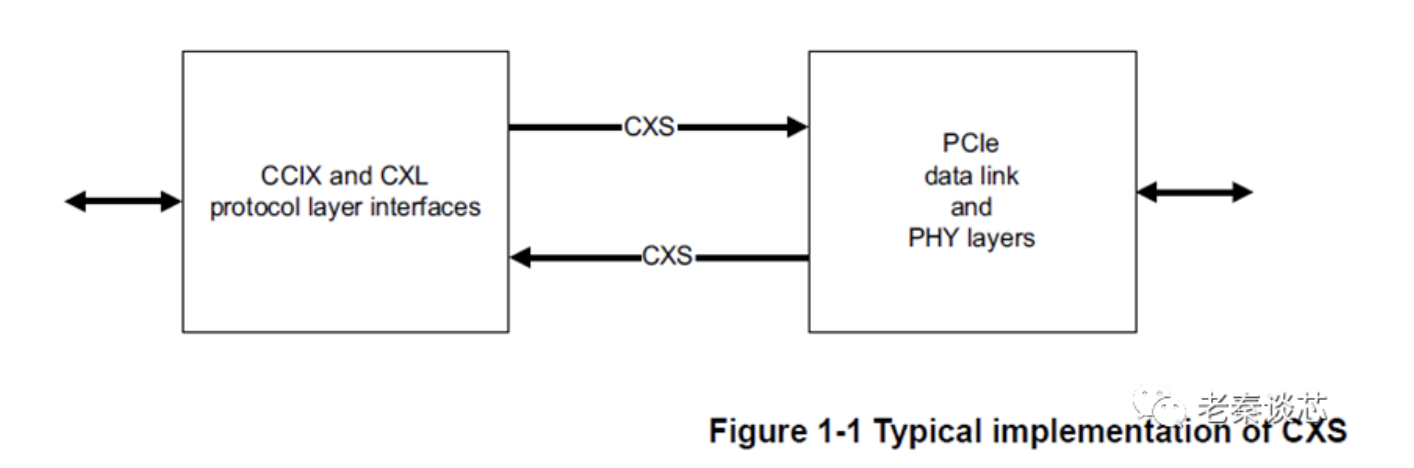

CXS (Credited eXtensible Stream)是一個流接口協議,主要用于點到點(point-to-point)的數據包通信。CXS接口的主要使用情形是在片上互連和PCIe控制器。CXS中的數據傳輸是單向的,因此一般CXS接口是收/發成對出現的。

看到這里,是不是想起了什么?沒錯,就是AXI-Stream,同樣也是點到點的流接口傳輸,比如中斷控制器GIC的組件之間就采用了AXI-Stream。AXI-Stream在 FPGA中應用較多,尤其是多媒體領域。

CXS接口的數據傳輸是單向的,兩端是Transmitter(TX)和Receiver(RX)。一個時鐘周期內傳輸的數據稱作flit。一個數據包可以占用一個或多個flit組成。

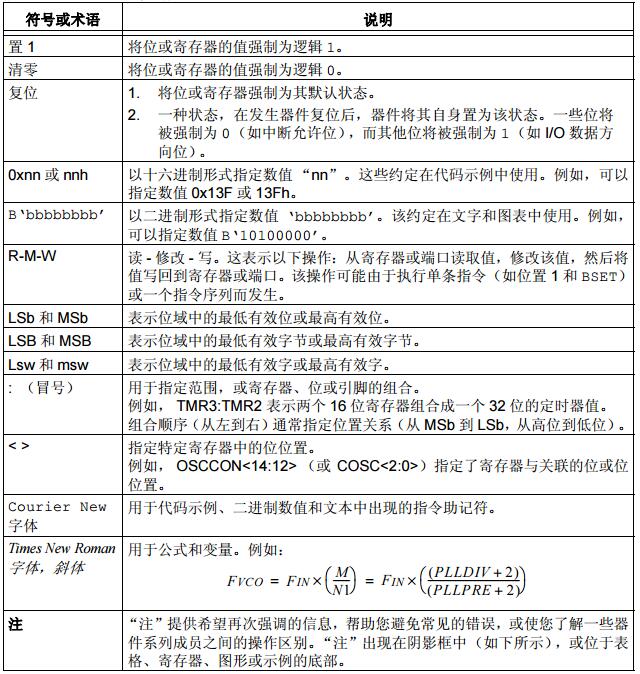

CXS的接口信號分為兩部分,一部分是必須包含的,另一部分是可選信號。其中必須實現的信號如下(以下用正粗體表示信號,斜粗體表示屬性):

從接口信號上看,并沒有READY信號,也就是說CXS不像其它的AMBA總線,比如AXI,是通過“VALID - READY”來控制流量。

正如名字中的含義,CXS接口上的流量控制(flow control)通過信用交換機制實現。其信用機制規則如下:

- 僅當TX有信用值時才能發送數據

- 當接口剛完成復位或者是第一次active,TX沒有信用值,不能發送數據

- RX通過CXSCRDGNT信號授予TX信用

- 在CXSCRDGNT被RX置位的每個時鐘周期,RX授予一個信用值給TX。每個信用值可用作一次flit傳輸。

- RX必須保證每釋放一個信用值,即可接收一個flit

- TX置位 CXSVALID ,每個時鐘周期發送一個flit,占用一個信用值

- RX可以授予TX的最大信用值數由CXS_MAX_CREDIT屬性決定

- TX只有等到CXSCRDGNT被置位之后,得到信用才能發送flit

- 可選,TX可以通過CXSCRDRTN返還信用值給RX,無需發送flit

- RX不能重用已消耗或返回的信用

- 如果TX在發送flit或者返回給RX信用的同時接收到一個信用,則TX端的可用信用數不變

正常情況下,TX發送一個flit給RX,同時消耗一個信用值;RX接收到flit,如果有能力接收更多的flit,則可以授予TX一個信用值;隨后,TX得到新的信用值。從TX消耗信用值到得到新的信用值,這段時間稱為信用延遲(credit latency)。為保證TX能夠源源不斷的發送數據,則需要設計好最大可用的信用數量,以保證不會由于信用延遲造成的斷流。

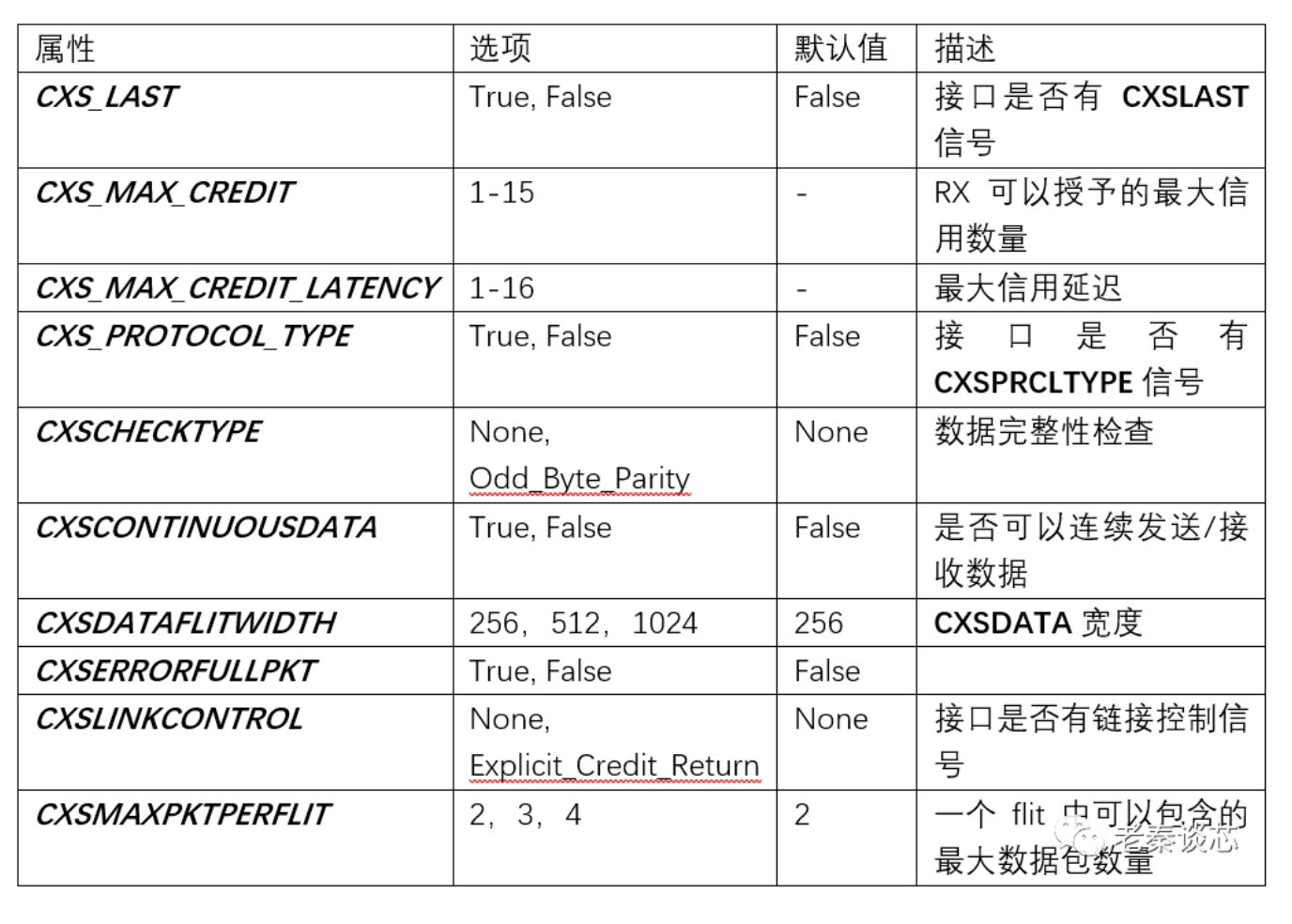

CXS接口的屬性包括以下:

其中,TX和RX的屬性可以單獨設置。

CXS的完整接口信號列表如下:

其中,CXSLAST用于連續傳輸;CXSPRCLTYPE用于支持多種協議類型。

當CXSCHECKTYPE 屬性被設置成Odd_Byte_Parity,CXS接口上會增加額外的信號線,用于增強接口信號的完整性。對于單bit信號線,增加一個bit,比如 CXSVALID ,增加一個信號 CXSVALIDCHK ;對于多bit信號,每8bit增加一個信號,比如256-bit的 CXSDATA ,增加一個32-bit信號 CXSDATACHK 。增加的信號與原信號相加為奇數。

CXS對每個flit中的數據包放置進行了限制,以簡化數據路徑實現:

- 數據包的第一個byte必須是16-byte對齊的邊界

- 數據包的后續字節占用flit的后續字節

- 數據包可以在任何4-byte對齊的邊界上結束。

- 從字節位置開始的數據包將占用該flit中的每個后續字節,直到數據包結束或flit結束。

- 如果flit結束時數據包中還有剩余字節,則該數據包將從下一個flit的字節[0]開始,并占據隨后的每個字節位置,直到數據包結束或flit結束。

- 當數據包在flit中結束時,flit中的剩余字節可以不使用。

- flit中的任何數據包必須從相對于flit開始或前一數據包結束的第一個可用16-byte邊界開始。

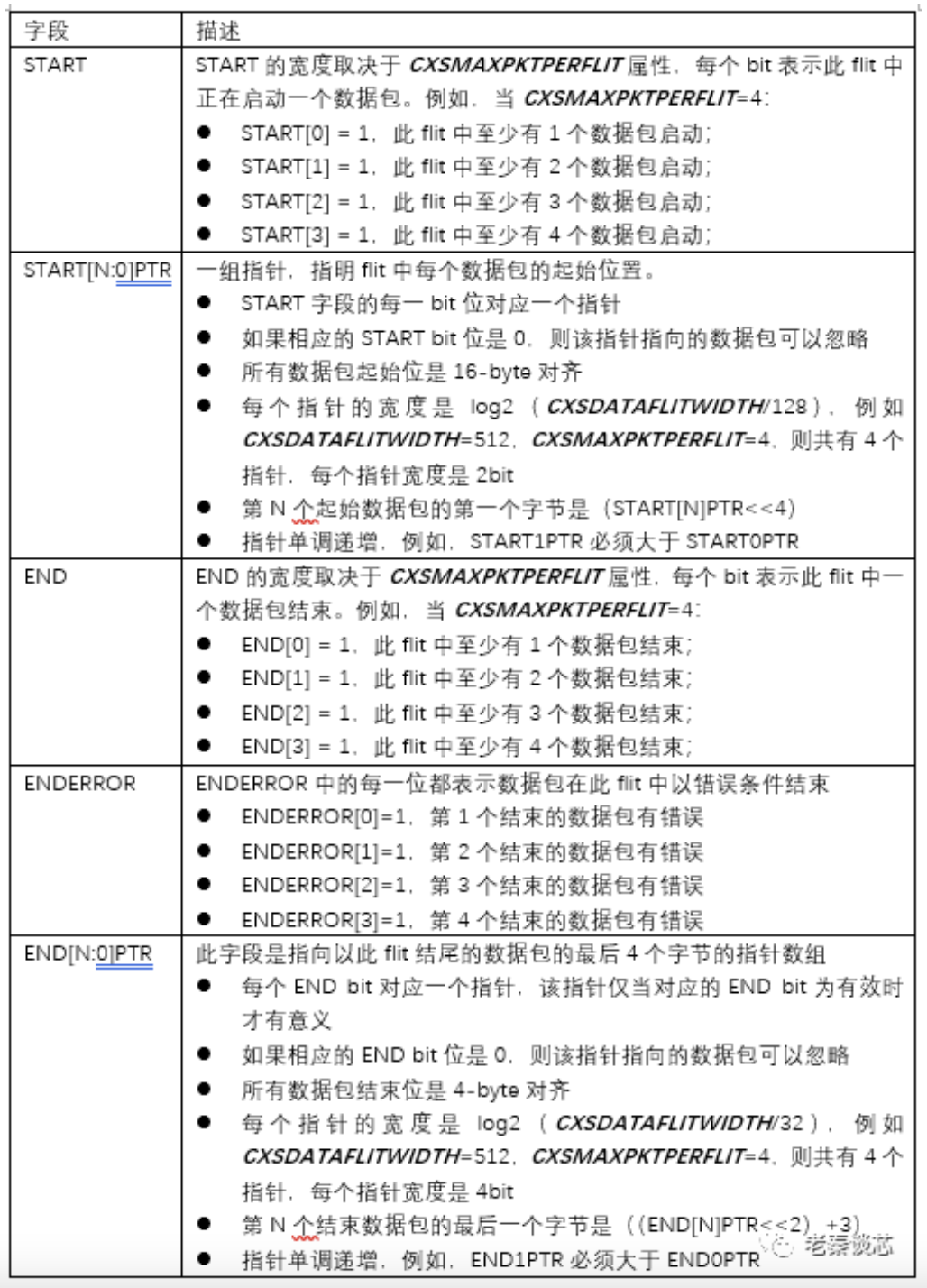

CXSCNTL信號總線可以分為五個字段,分別為:START,START[N:0]PTR,END,ENDERROR和END[N:0]PTR。下面分別解釋。

下圖給出CXSCNTL信號的組成示例。當屬性 **CXSMAXPKTPERFLIT ** = 4,屬性 **CXSDATAFLITWIDTH ** = 512時,CXSCNTL信號共有36-bit。

CXS接口傳輸滿足以下要求的數據包大小需滿足:

- 至少為4字節

- 為4字節的倍數

- 數據大小沒有上限

如果CXS用于CCIX數據包傳輸,需要遵守CCIX的約定。

協議中給出了數據包傳輸的例子,看一個比較復雜的示例。屬性 ***CXSMAXPKTPERFLIT *** = 4, ***CXSDATAFLITWIDTH *** = 512, ***CXSCONTINUOUSDATA *** = true,Protocol 0用于可變長數據包,Protocol 1用于固定長64-byte數據包。在Protocol 0中,P0D和P0E分組必須保持在一起;在Protocol 1中,P1B和P1C分組必須保持在一起,P1E,P1F和P1分組必須保持在一起。

當屬性 **CXSLINKCONTROL _ ** = Explicit *Credit *Return,CXS接口上會多出一組信號, CXSCRDRTN , CXSACTIVEREQ ,CXSACTIVEACK和 CXSDEACTHINT 。

其中 CXSACTIVEREQ ,CXSACTIVEACK實現四相位的握手機制。握手機制共分為四種狀態:

- STOP

- CXS接口在STOP狀態時沒有任何操作,所有的信用被RX收回

- STOP是一個穩定狀態,CXS接口可以無限期保持在STOP

- RX此時不可以接收flit,也不可以授予信用

- TX此時不可以發送flit,也不可以返還信用

- 如果TX有flit等待發送,需要從STOP狀態轉移到ACTIVATE狀態

- ACTIVATE

- 此狀態為STOP到RUN的過渡

- 期望進入此狀態后,期待CXS通路很快進入RUN狀態

- 此狀態下,TX必須接收信用,但還不可以發送flit

- RX此時不可以接收flit,也不可以授予信用

- RX不可以在狀態ACTIVATE下發送信用。但是允許RX在進入RUN狀態的同一周期內發送信用。由于存在潛在的競爭條件,因此TX在ACTIVATE狀態下可能會收到信用

- 當RX準備好接收flit時,它可以從ACTIVATE狀態轉移到RUN狀態

- RUN

- TX和RX在此狀態下傳輸flit

- RUN狀態是穩定狀態,CXS通道可以一直保持在RUN狀態

- RX可以接收flit,授予信用,接收返還的信用

- TX可以發送flit,,接收信用

- TX允許返還信用給RX

- TX可以在某些情況下從RUN狀態切換到DEACTIVATE狀態,比如TX沒有flit可以發送了

- DEACTIVATE

- 此狀態用于從RUN到STOP的過渡

- DEACTIVATE是一個中間狀態

- 在進入此狀態前,TX必須停止發送flit,由于潛在的競爭條件,RX有可能在此狀態下接收flit

- RX可以發送信用,當RX發現TX返還信用時必須停止繼續發送信用

- RX可以接收TX返還的信用

- TX必須發送信用返回,以便將所有信用返回給RX。

- 只有當所有信用都已返回時,RX才能退出該狀態并移至STOP狀態。

四種狀態轉換的關系如下圖:

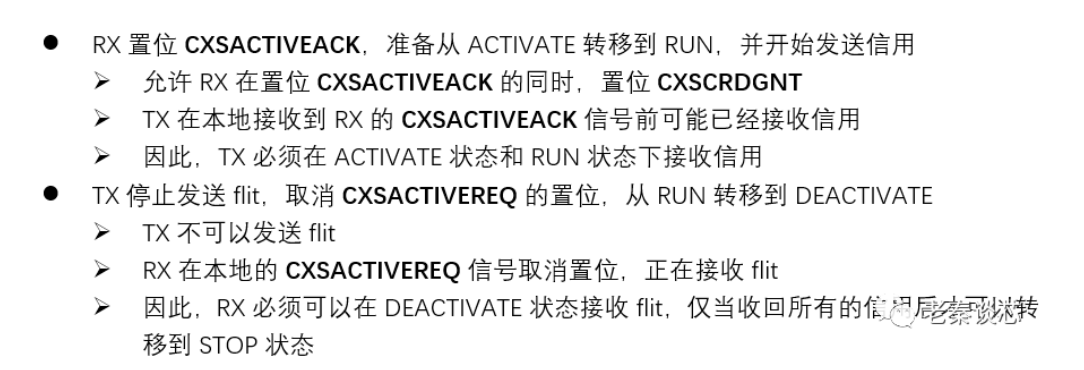

TX始終負責啟動從RUN到STOP,或從STOP到RUN的狀態更改,例如:

- TX端有flit等待發送,所以需要從STOP轉移到RUN

- TX端沒有flit可以發送,可以從RUN切換到STOP

- TX可以觀測一個獨立的邊帶信號,判斷是否需要從RUN移動到STOP,或從STOP移動到RUN

- TX可以觀測RX發出的CXSDEACTHINT來判斷是否需要從RUN轉移到STOP

當接口的一方同時執行兩個操作時,即存在競爭條件。CXS規范允許數據流和鏈路控制信號組之間存在不同的延遲。因此,到達時的操作順序可能與發出的順序不同。競爭條件之所以會存在,是因為不要求CXSACTIVEREQ和CXSACTIVEACK信號不需要在TX和RX之間的其它信號具有相同的延遲。

CXS接口信號間的時序關系如下。

- CXSVALID,CXSDATA,CXSCNTL和CXSCRDRTN必須是同步關系,且具有相同的延時

- CXSCRDGNT,CXSACTIVEACK,CXSDEACTHINT必須是同步,但是可以有任意延時

- CXSACTIVEREQ必須是同步驅動,但是接收端可以異步接收,且可以任意延時

來看一個例子。

- 1.T0時刻,TX和RX都處于STOP狀態,兩邊都可以關斷時鐘,甚至電源;

- T1時刻,TX置位 CXSACTIVEREQ ,從STOP轉移到ACTIVATE;TX等待RX啟動;

- 3.T6時刻,RX完成啟動,置位 CXSACTIVEACK ;

- 4. CXSCRDGNT與CXSACTIVEACK**在同一時刻被置位;

- 5. T7時刻,TX接收到一個信用,發送一個flit;

- 6. TX在接收到更多信用后,連續發送flit。

某些情況下,CXS通道不能中斷數據流,例如PCIe。這時,需要TX和RX實現一個存儲轉發(store-and-forward)buffer。

如果RX內置了這個buffer,數據包可以被下游完整接收。RX必須有足夠的空間來存儲TX所能發送的最大數據包。這種情況下,TX和RX可以設置屬性 *** CXSCONTINUOUSDATA * ** = False。TX無需緩存數據包。

如果RX沒有緩沖區并且需要連續數據,則它會將** *CXSCONTINUOUSDATA *屬性設置為True,并且TX也必須將 *CXSCONTINUOUSDATA ***設置為True。然后,TX必須能夠在不依賴其它接口的情況下發出數據包內的所有flit。

如果需要連續流量,必須確保RX有足夠的信用來覆蓋最壞情況下的往返信用延遲:

- RX和TX之間的CXSCRDGNT延遲

- TX端的CXSTXCRDGNT和CXSTXVALID之間的最大內部延遲,由TX的CXS_MAX_CREDIT_LATENCY屬性描述

- RX和TX之間的CXSVALID延遲

- RX端的CXSTXVALID和CXSTXCRDGNT之間的最大內部延遲,由RX的CXS_MAX_CREDIT_LATENCY屬性描述

RX可以發出的最大信用數取決于其緩沖區的大小,可以通過其** CXS MAX *CREDIT ***屬性來描述。

如果下游接口的時鐘比CXS鏈路慢,則可能不需要每個周期發送一個flit。在這種情況下,RX保持恒定流量所需的信用數可能小于往返延遲。

-

緩沖器

+關注

關注

6文章

1903瀏覽量

45320 -

接收機

+關注

關注

8文章

1158瀏覽量

53161 -

狀態機

+關注

關注

2文章

489瀏覽量

27391 -

中斷控制器

+關注

關注

0文章

59瀏覽量

9411 -

PCIe接口

+關注

關注

0文章

116瀏覽量

9625

發布評論請先 登錄

相關推薦

ARM系列-CXS基礎知識介紹

ARM系列-CXS基礎知識介紹

評論