前言

Chiplet多芯片系統(tǒng)將多個(gè)裸芯片集成在單個(gè)封裝中,這對(duì)于系統(tǒng)架構(gòu)的設(shè)計(jì)來(lái)說(shuō)增加了新的維度和復(fù)雜性,多芯片系統(tǒng)的設(shè)計(jì)貫穿著系統(tǒng)級(jí)協(xié)同設(shè)計(jì)分析方法。

在系統(tǒng)定義和規(guī)劃時(shí),虛擬原型可以用來(lái)分析架構(gòu)設(shè)計(jì)決策可能產(chǎn)生的影響,將系統(tǒng)的功能性和非功能性要求轉(zhuǎn)化為系統(tǒng)的物理硬件屬性,包括裸片的目標(biāo)工藝、面積大小以及不同組成芯片的組裝要求等。根據(jù)不同的解決方案,選擇不同的chiplets和堆疊架構(gòu),進(jìn)行早期的分析驅(qū)動(dòng)的架構(gòu)探索和優(yōu)化迭代,包括電氣可靠性、散熱、良率分析、應(yīng)力分析等等。從而可以基于目標(biāo)系統(tǒng)的指標(biāo)定義,確定系統(tǒng)的瓶頸所在——性能、功耗、存儲(chǔ)容量/帶寬、面積/體積、成本以及上市時(shí)間等,逐步建立和完善各類(lèi)分析模型,使得整個(gè)系統(tǒng)最終定型。

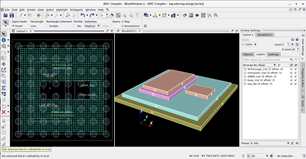

芯和半導(dǎo)體的3DICCompiler(以下簡(jiǎn)稱(chēng)“3DICC”)設(shè)計(jì)平臺(tái),全面支持chiplet多芯片系統(tǒng)2.5D/3D集成設(shè)計(jì)和仿真。本文介紹如何在3DICC設(shè)計(jì)平臺(tái)實(shí)現(xiàn)基于虛擬原型實(shí)現(xiàn)多芯片架構(gòu)探索。整個(gè)流程包含chiplets虛擬原型和頂層創(chuàng)建、布局堆疊規(guī)劃、Bump/TSV設(shè)計(jì)規(guī)劃、PG網(wǎng)絡(luò)規(guī)劃和系統(tǒng)早期EMIR&Thermal分析等。

案例介紹

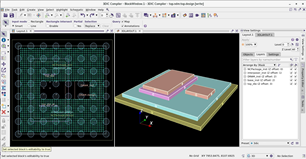

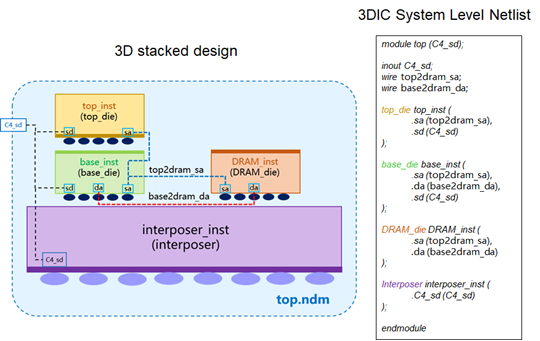

圖1

多芯片系統(tǒng)3D架構(gòu)探索、布局、分析和迭代

1. Chiplets虛擬原型和頂層創(chuàng)建

創(chuàng)建chiplets虛擬原型,包含長(zhǎng)寬尺寸和信號(hào)接口規(guī)劃。

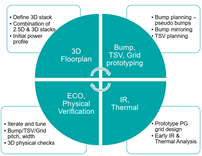

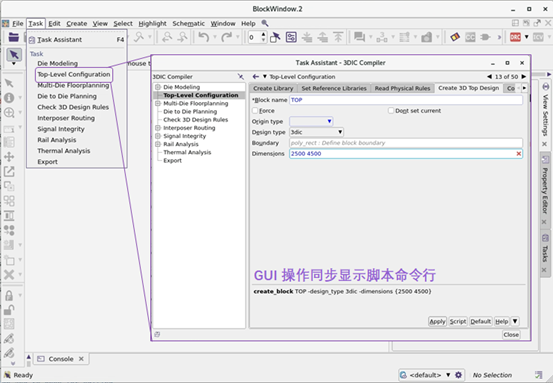

圖 2

虛擬芯片原型創(chuàng)建

創(chuàng)建虛擬頂層網(wǎng)表,建立芯片間互連關(guān)系,包含多芯片系統(tǒng)的所有實(shí)例和互連,但不會(huì)產(chǎn)生用于生產(chǎn)制造的實(shí)際GDS。

圖3

虛擬頂層網(wǎng)表創(chuàng)建

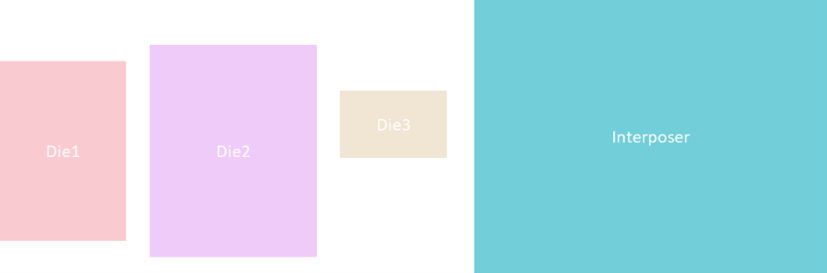

2. 布局堆疊規(guī)劃

Chiplet多芯片系統(tǒng)架構(gòu)和布局規(guī)劃有諸多因素需要考量,如chiplets和IP選擇、接口協(xié)議和類(lèi)型、裸片是并排放置還是垂直堆疊等等,選擇的確定取決于目標(biāo)應(yīng)用在功耗、性能、功能、成本和散熱等方面的要求。

3DICC對(duì)于系統(tǒng)的架構(gòu)布局支持多種芯片堆疊方式,如face-to-face、face-to-back等,在布局探索過(guò)程中,這些都可以從2D和3D的視圖進(jìn)行交互式設(shè)計(jì),快捷直觀。

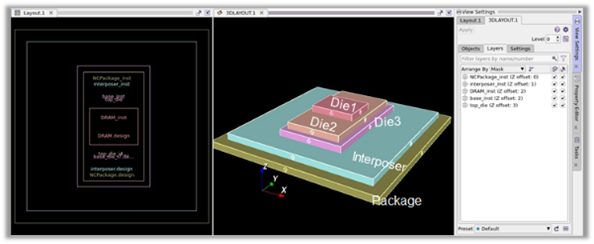

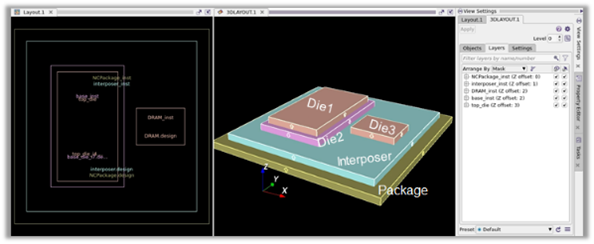

圖4

堆疊布局探索

3.Bump/TSV設(shè)計(jì)規(guī)劃

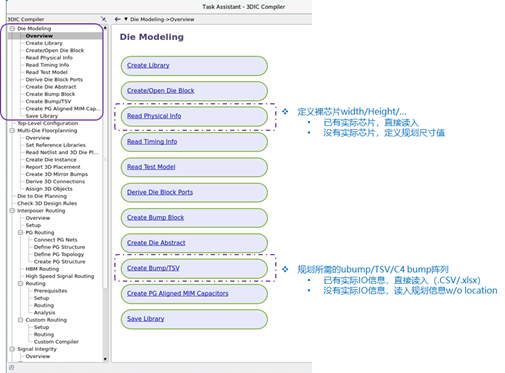

在chiplets的架構(gòu)探索和設(shè)計(jì)階段,需要完成系統(tǒng)級(jí)Floorplan和各個(gè)層次的bump planning。

對(duì)于ubump、TSV、C4 bump的設(shè)計(jì),3DICC支持多種規(guī)劃方式,包括CSV、Excel表格以及圖形界面陣列設(shè)計(jì)等,可以根據(jù)實(shí)際的設(shè)計(jì)條件和需求,選擇適合的方式進(jìn)行。例如:

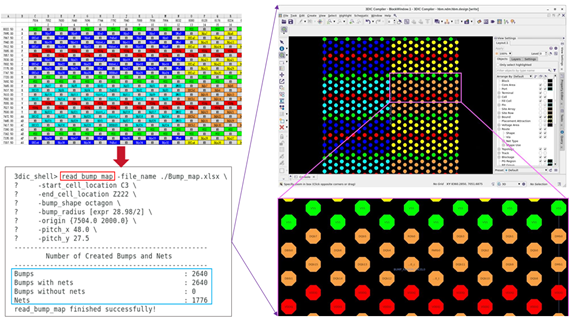

Die1:已有Excel表格類(lèi)型IO信息,導(dǎo)入文件自動(dòng)創(chuàng)建。

圖 5

導(dǎo)入excel格式的bump map

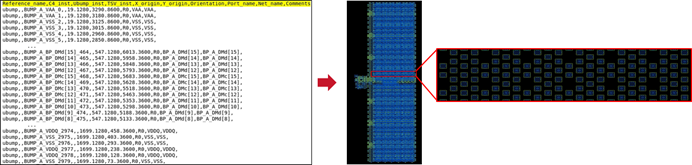

Die2:已有CSV格式IO信息,導(dǎo)入文件自動(dòng)創(chuàng)建。

圖6

FanOut設(shè)計(jì)頂層創(chuàng)建

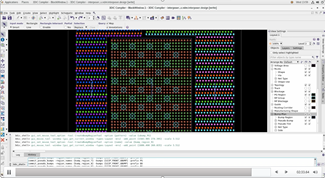

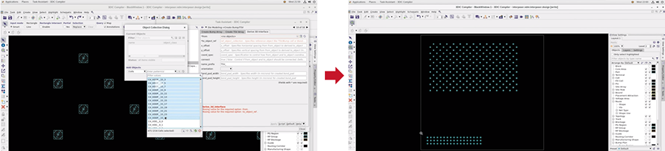

Die3:只有IO信號(hào)列表,可以設(shè)定區(qū)域和pattern創(chuàng)建,也可以由工具基于信號(hào)接口關(guān)系自動(dòng)分布創(chuàng)建。

圖7

設(shè)定區(qū)域和pattern創(chuàng)建bump陣列

圖8

工具自動(dòng)分布創(chuàng)建bump陣列

4.PG網(wǎng)絡(luò)規(guī)劃和系統(tǒng)早期EMIR&Thermal分析

3DICC可以快速建立不同類(lèi)型和pattern的PG網(wǎng)絡(luò),用于支持原型階段的EMIR和Thermal建模分析。這些結(jié)果為PG網(wǎng)絡(luò)、bump/TSV陣列、芯片熱功耗、芯片堆疊方式等設(shè)計(jì)選擇確定提供了必要的數(shù)據(jù)支持,推進(jìn)架構(gòu)探索設(shè)計(jì)迭代優(yōu)化。

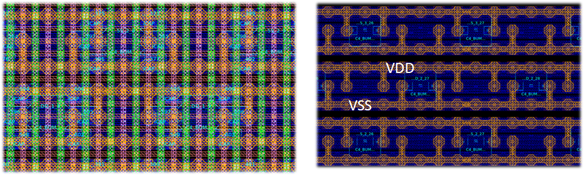

圖9

PG網(wǎng)絡(luò)實(shí)現(xiàn)

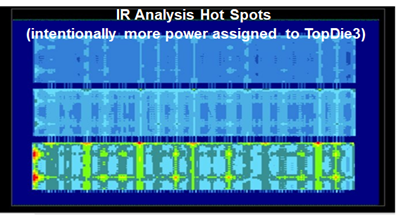

圖10

EMIR&Thermal分析示例

總結(jié)

與單片系統(tǒng)相比,chiplet多芯片系統(tǒng)在架構(gòu)定義階段,必須通過(guò)功能架構(gòu)、物理架構(gòu)的協(xié)同假設(shè)和優(yōu)化,從整個(gè)系統(tǒng)的角度進(jìn)行設(shè)計(jì)和驗(yàn)證,問(wèn)題越早發(fā)現(xiàn),就越有可能做出有影響力的改變來(lái)優(yōu)化整個(gè)系統(tǒng)。通常來(lái)說(shuō),有價(jià)值的設(shè)計(jì)數(shù)據(jù)通常要到設(shè)計(jì)流程的后期才能獲得,而借助虛擬原型技術(shù),開(kāi)發(fā)者可以更好地掌控功耗和性能,同時(shí)仍可以在設(shè)計(jì)過(guò)程中做出修正和優(yōu)化,從而規(guī)劃出系統(tǒng)的理想藍(lán)圖。

3DIC Compiler提供的基于虛擬原型實(shí)現(xiàn)多芯片架構(gòu)探索,對(duì)于多芯片系統(tǒng)的可行性、可優(yōu)化性和可實(shí)現(xiàn)性等方面提供了有效且高效的功能支持。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

453文章

50393瀏覽量

421786 -

封裝

+關(guān)注

關(guān)注

126文章

7778瀏覽量

142719 -

仿真

+關(guān)注

關(guān)注

50文章

4041瀏覽量

133413 -

chiplet

+關(guān)注

關(guān)注

6文章

416瀏覽量

12558 -

芯和半導(dǎo)體

+關(guān)注

關(guān)注

0文章

99瀏覽量

31405

原文標(biāo)題:【應(yīng)用案例】如何在 3DICC 中基于虛擬原型實(shí)現(xiàn)多芯片架構(gòu)探索

文章出處:【微信號(hào):Xpeedic,微信公眾號(hào):Xpeedic】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何基于3DICC實(shí)現(xiàn)InFO布局布線(xiàn)設(shè)計(jì)

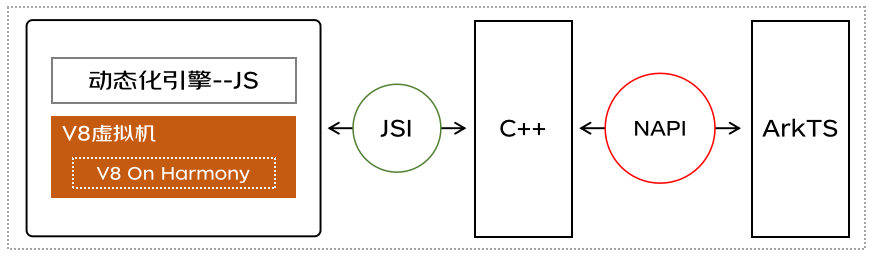

鴻蒙跨端實(shí)踐-JS虛擬機(jī)架構(gòu)實(shí)現(xiàn)

高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)設(shè)計(jì)及驗(yàn)證

多通道RF到位開(kāi)發(fā)平臺(tái)可實(shí)現(xiàn)相控陣的快速原型設(shè)計(jì)

如何在嵌入式系統(tǒng)或快速原型構(gòu)建板上實(shí)現(xiàn)即交即用式部署?

如何在visual studio上實(shí)現(xiàn)USB虛擬串口功能?

STM32實(shí)現(xiàn)虛擬串口功能

ARM GIC(八)GICv3架構(gòu)的變化

將 Virtualizer 虛擬原型和 HAPS 系列基于 FPGA 的原型無(wú)縫集成

帶有Android的四核ARM虛擬原型

如何在3DICC中基于虛擬原型實(shí)現(xiàn)多芯片架構(gòu)探索

如何在3DICC中基于虛擬原型實(shí)現(xiàn)多芯片架構(gòu)探索

評(píng)論