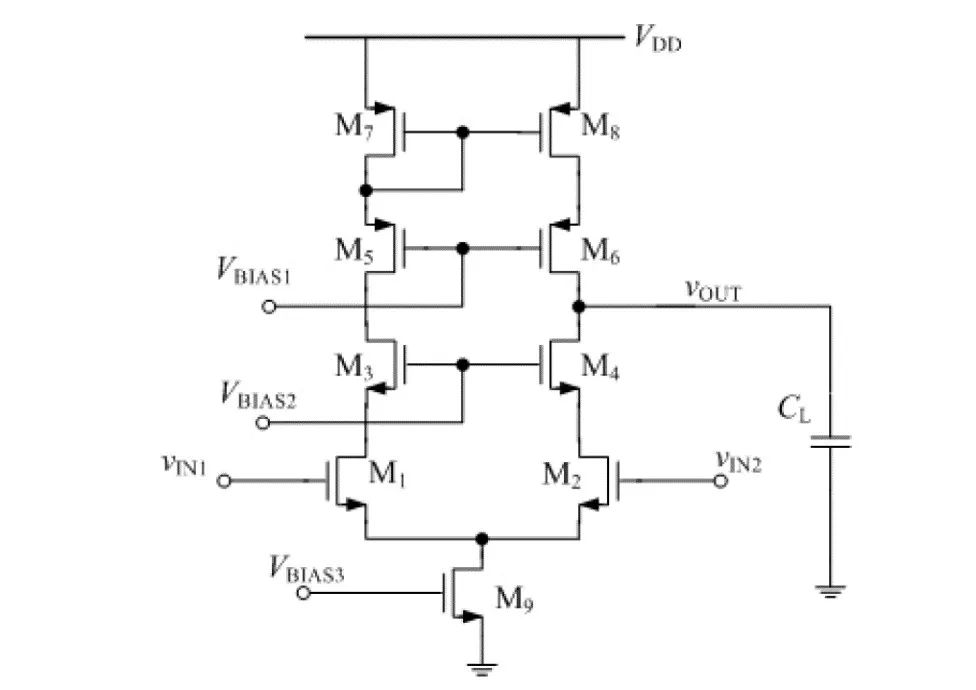

figure 1 套筒式運放原理圖

設計思路:

- 通過M9電流200uA,兩條支路分別是100uA的電流。我們計算設計仿真的順序是:M9-M7M8-M5M6-M1M2-M3M4。

- M9電流大,過驅動電壓給大些,Von9=300mV,I9=200uA,利用飽和區電流公式計算M9的W/L。偏置電壓用Von+Vth算。

- M7M8的PMOS管本應該給大Von,但是其二極管連接,Vds大,由于溝道調制效應,所以給小Von=200mV,I=100uA,計算M7和M8的W/L。

- M5M6手工計算不準確,但還是得初步計算。I=100uA,pmos需給大Von=300mV,算出寬長比。偏置電壓Vb1

- M1和M2,Von=200mV,I=100uA,計算寬長比。偏置電壓Vcm=Vds9+Von1+Vth1。此時的Vth1和Vds9都需要仿真后查看再調整輸入共模電壓。

- M3和M4與M1和M2寬長比計算一樣。Vb2= Vds9+Vds11+Von3+Vth3,同樣需要仿真后回頭調整。

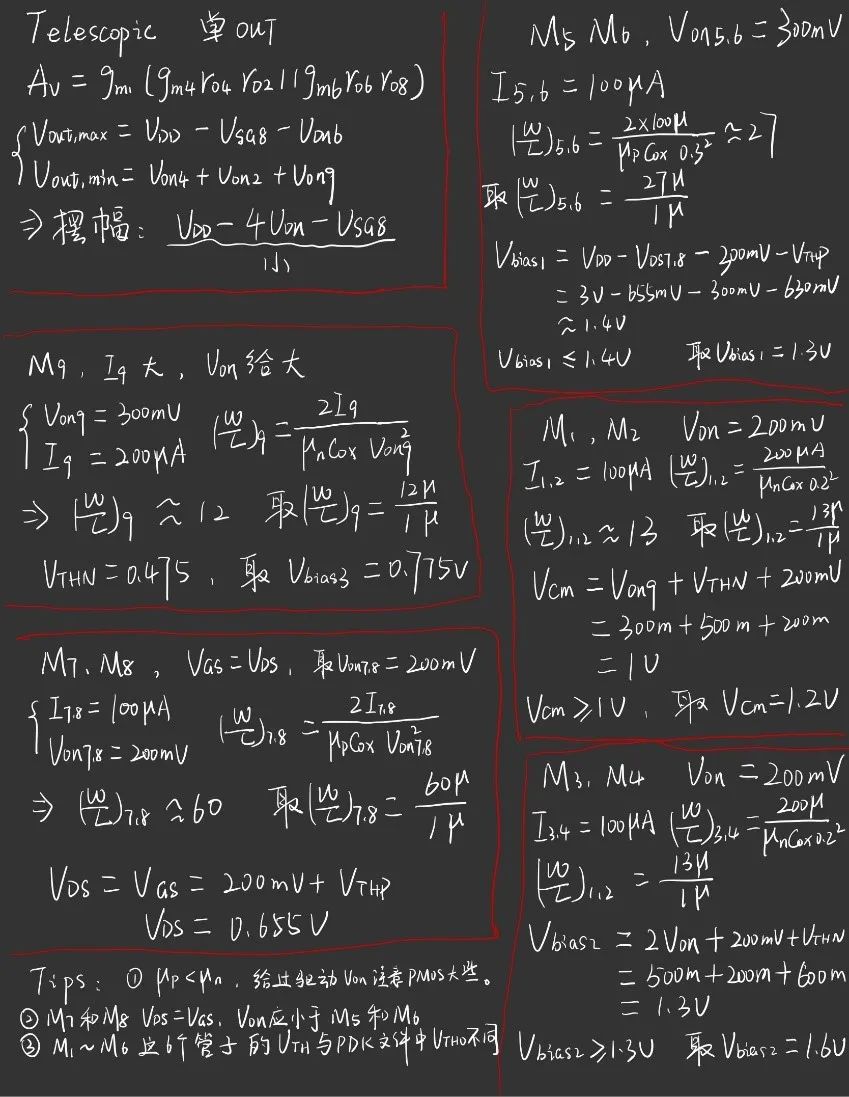

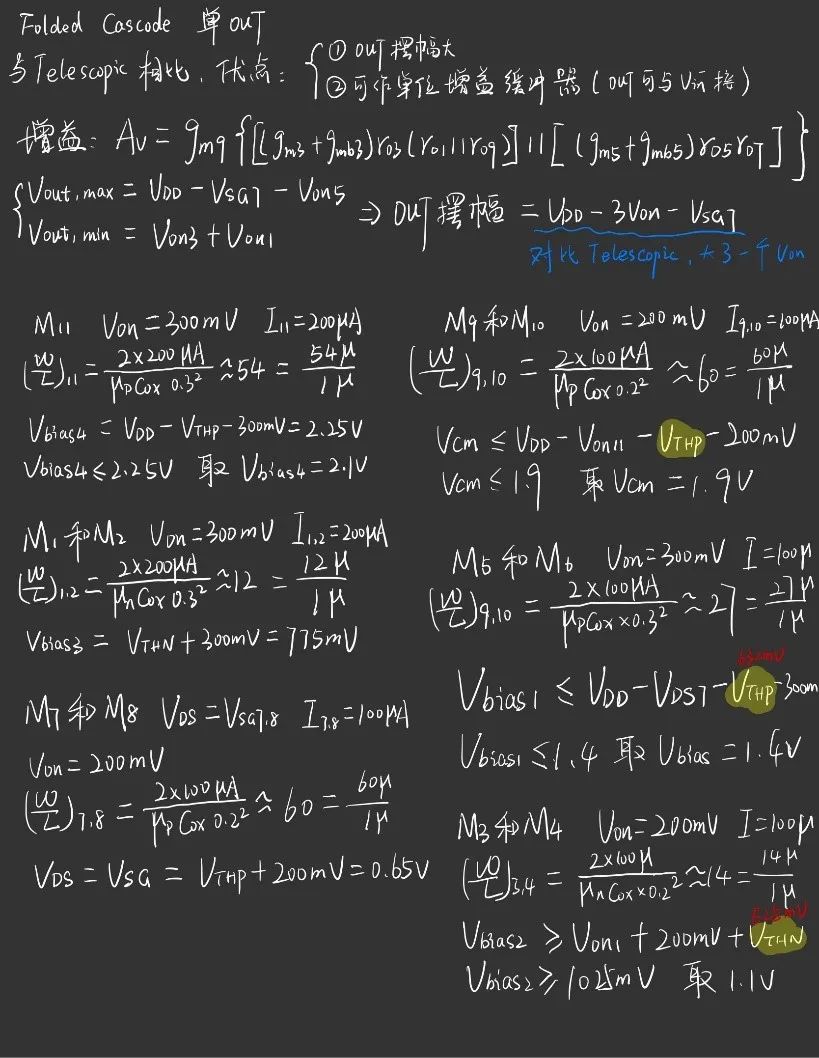

圖2是手算的記錄:

figure 2 telescopic手算

M5和M6最難調整,可以將其余的偏置電壓確定后,用parametricanalysis掃描一下這兩管子的寬,確定一個精確值。在TSMC180nm工藝下,我的電路的參數如下:

| Vcc | 3V | (W/L)9 | 12u/1u |

|---|---|---|---|

| Vcm | 1.2V | (W/L)7,8 | 60u/1u |

| Vb1 | 1.3V | (W/L)5,6 | 27u/1u |

| Vb2 | 1.6V | (W/L)3,4 | 13u/1u |

| Vb3 | 775mV | (W/L)1,2 | 13u/1u |

| CL | 3pF |

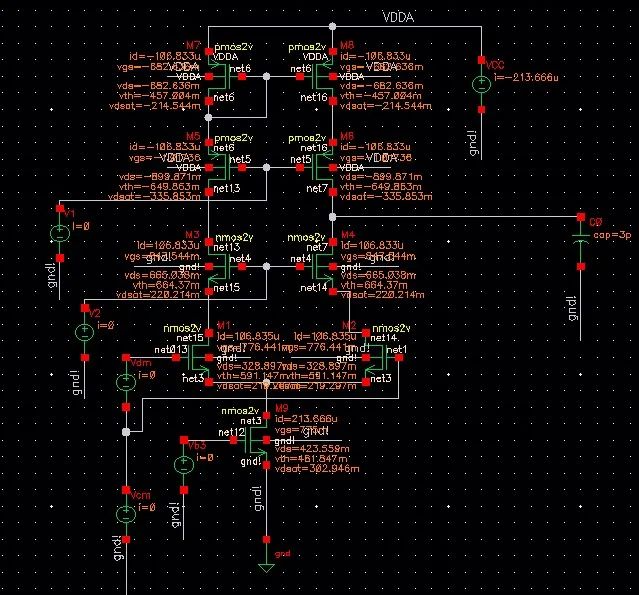

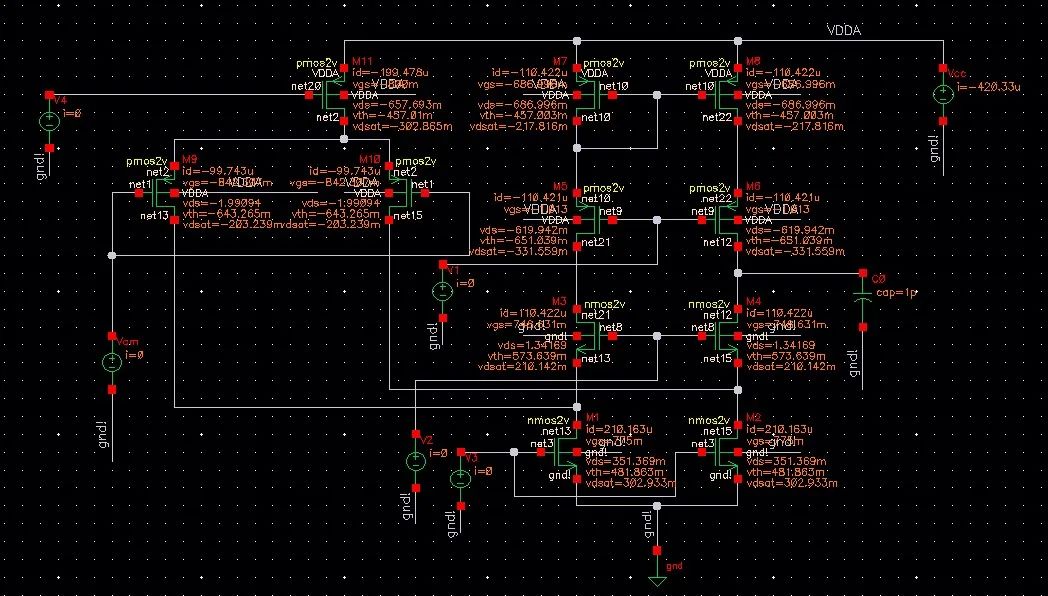

DC仿真結果如下:

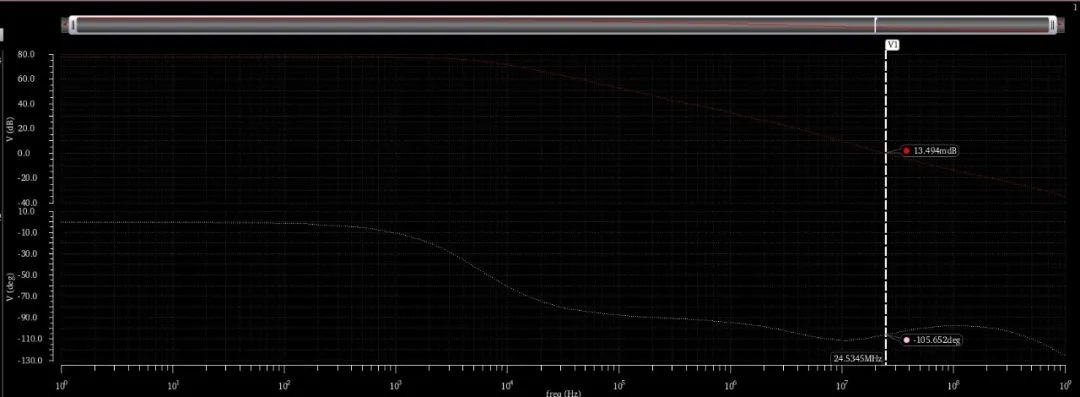

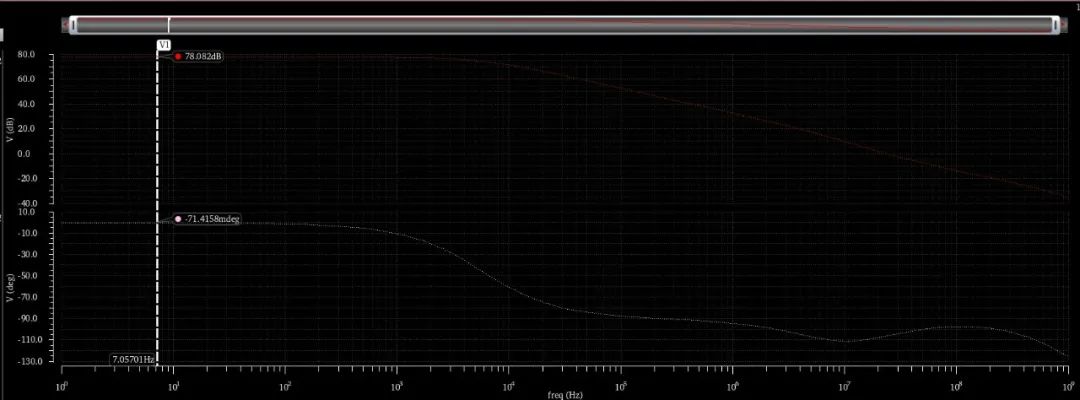

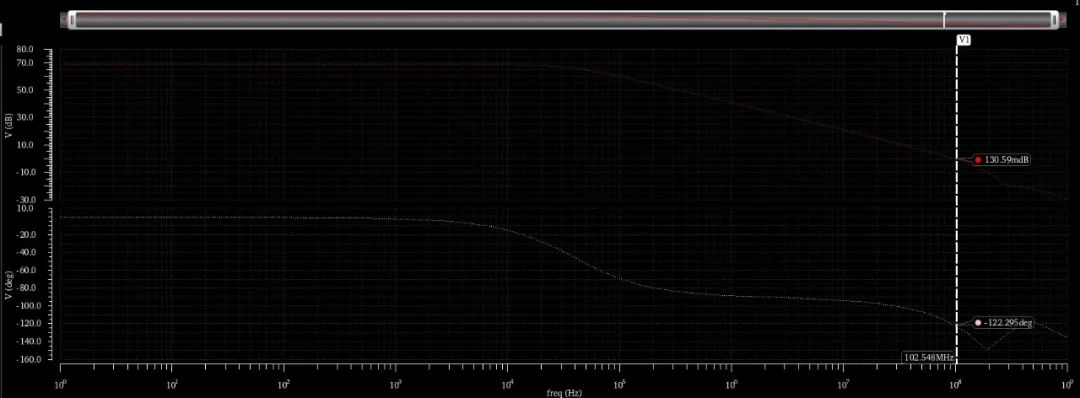

ac仿真結果如下,低頻增益78dB。

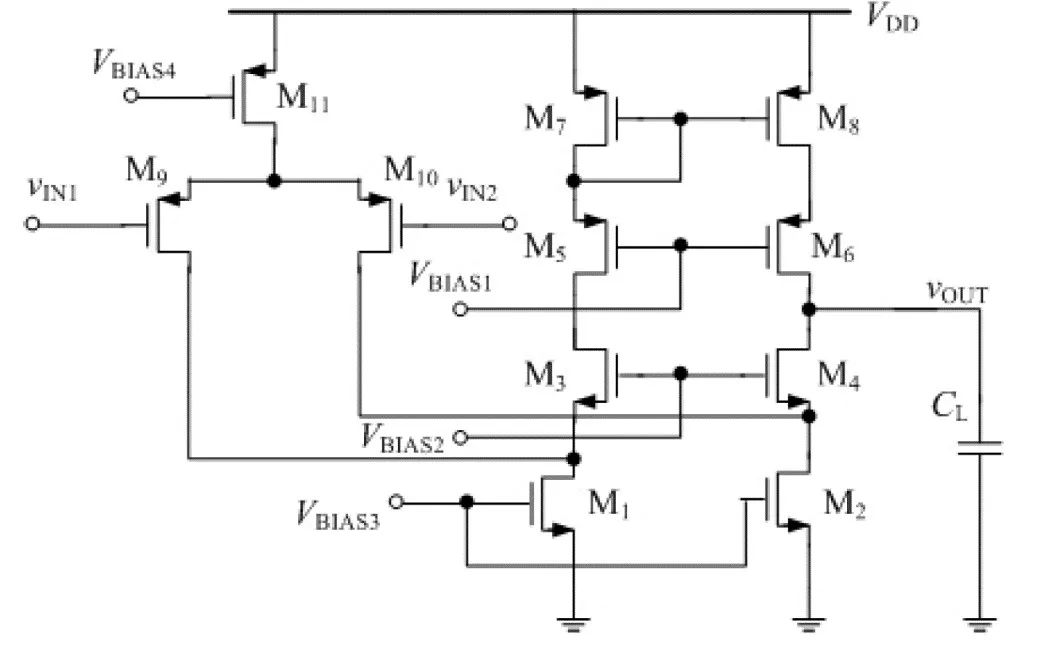

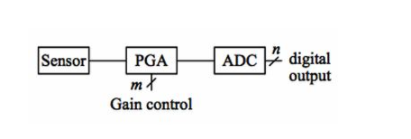

二、折疊共源共柵單級單端輸出運放

figure 3 折疊共源共柵運放電路原理圖

設計步驟與telescopic差不多,主要就是每個偏置電壓需要多次仿真調節,M5和M6的寬長比很敏感,需要parametricanalysis掃描一下。圖4是手算記錄:

figure 4 折疊共源共柵運放參數手算

在TSMC180nm工藝下,電路參數如下表:

| Vcc | 3V | (W/L)9 | 12u/1u |

|---|---|---|---|

| Vcm | 1.5V | (W/L)7,8 | 60u/1u |

| Vb1 | 1.3V | (W/L)5,6 | 29u/1u |

| Vb2 | 1.1V | (W/L)3,4 | 14u/1u |

| Vb3 | 775mV | (W/L)1,2 | 12u/1u |

| Vb4 | 2.2V | (W/L)9,10 | 70u/1u |

| CL | 1pF | (W/L)11 | 54u/1u |

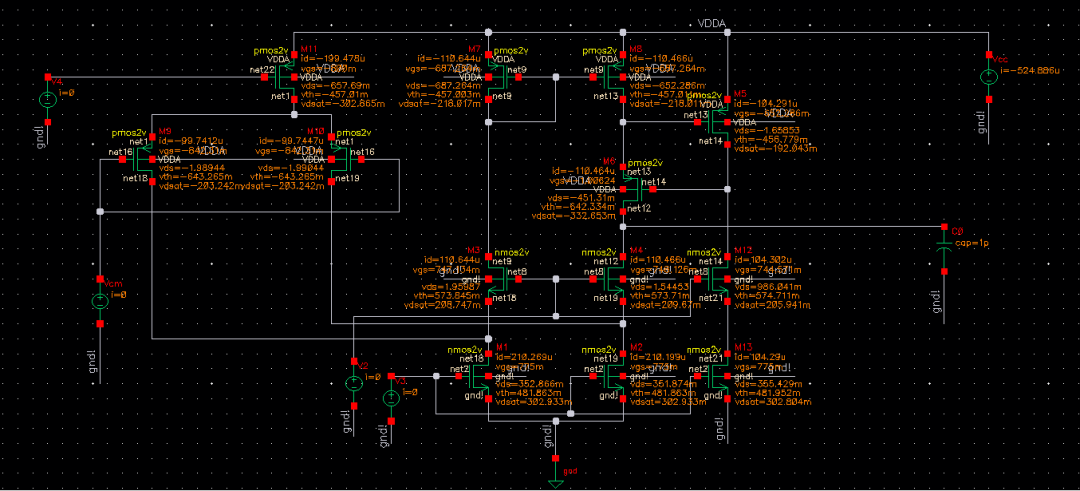

dc直流仿真結果如下圖:

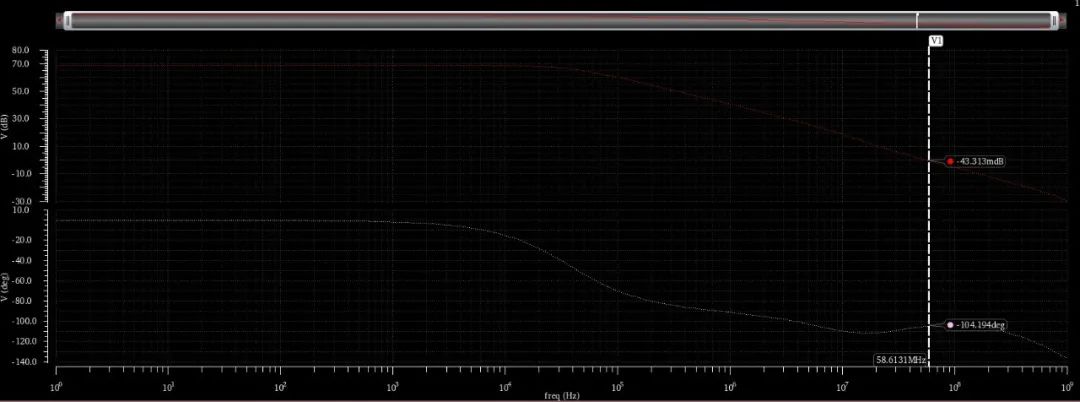

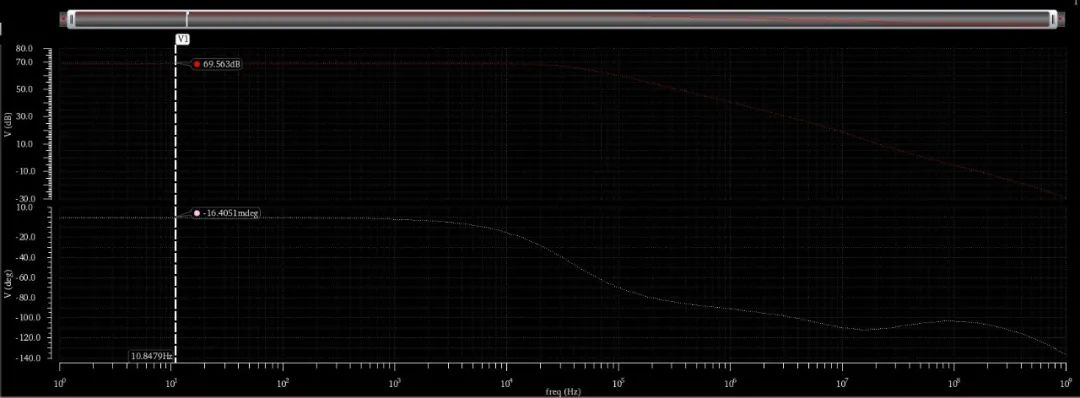

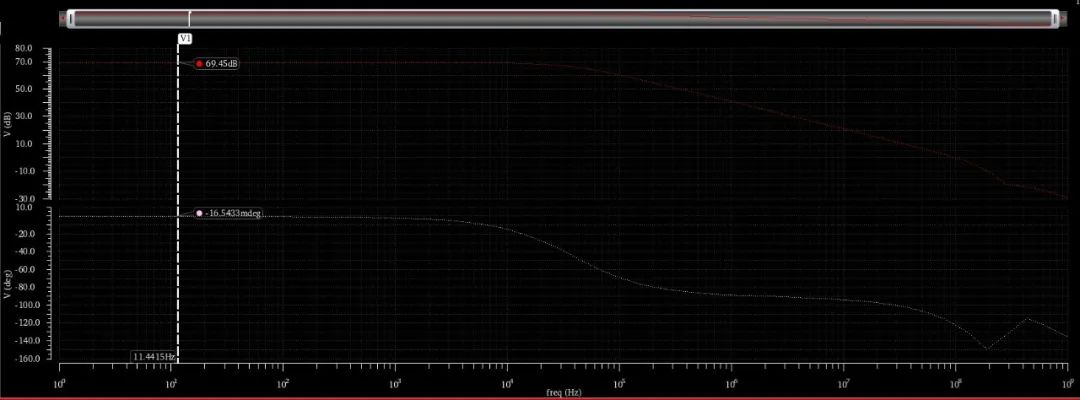

ac仿真結果如下圖,低頻增益69dB:

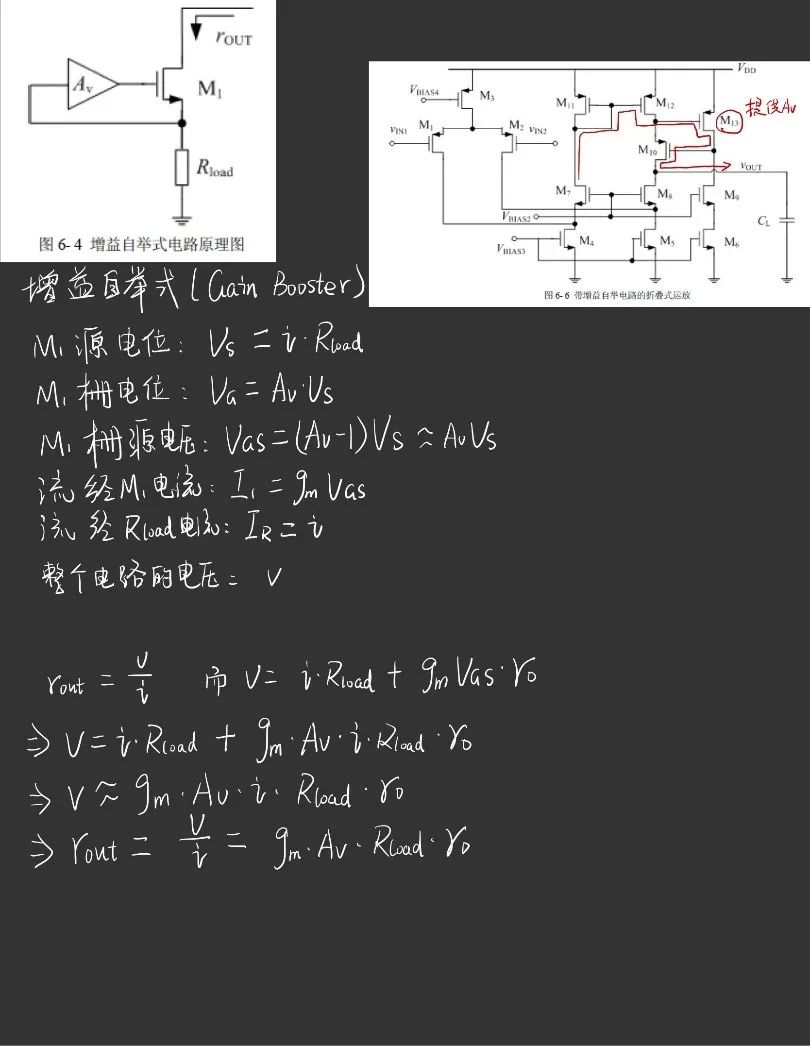

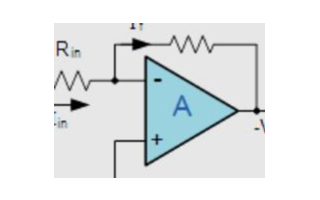

三、增益自舉(Gain Booster)

增益自舉原理如下圖:

將折疊共源共柵運放改進成下面的電路,并給出仿真直流參數:

上面的電路的M5寬長比調節至關重要,要使其Vds恰好給M6提供偏置電壓,而M6所需偏壓和前述折疊共源共柵的M5和M6一模一樣。在TSMC180nm工藝下,該電路參數如下表:

| Vcc | 3V | (W/L)9 | 12u/1u |

|---|---|---|---|

| Vcm | 1.5V | (W/L)7,8 | 60u/1u |

| Vb1 | 1.3V | (W/L)5 | 72u/1u |

| (W/L)6 | 29u/1u | ||

| Vb2 | 1.1V | (W/L)3,4,12 | 14u/1u |

| Vb3 | 775mV | (W/L)1,2=2(W/L)13 | 12u/1u |

| Vb4 | 2.2V | (W/L)9,10 | 70u/1u |

| CL | 1pF | (W/L)11 | 54u/1u |

ac仿真結果如下圖,低頻增益69dB(不知為何增益沒有提高,但是GBW增大了一倍,猜測是引入了零點):

四、總結

不管是折疊共源共柵還是套筒式,電流源負載管M5和M6的偏置電壓和寬長比總是最敏感的,需要多次仿真調整。

對于增益自舉電路的加入,沒能提升共源共柵運放的增益這點有待深入學習。

給過驅動電壓Von一般:NMOS小些,PMOS大些,二極管連接的PMOS小些。

-

二極管

+關注

關注

147文章

9581瀏覽量

165954 -

電路設計

+關注

關注

6667文章

2430瀏覽量

203420 -

運放

+關注

關注

47文章

1155瀏覽量

52984 -

仿真

+關注

關注

50文章

4048瀏覽量

133431 -

PMOS管

+關注

關注

0文章

82瀏覽量

6618

發布評論請先 登錄

相關推薦

高增益與高帶寬怎么兼得?

三運放放大器怎么提高增益和CMRR?

單位增益穩定的運放是什么類型的運放?

高增益與高帶寬電路設計,如何實現?

可編程增益放大器電路如何實現高增益

高增益單級運放和增益自舉電路設計

高增益單級運放和增益自舉電路設計

評論