寫在前面

本文以STM32F401RCT6為例,講解單片機最小系統的設計方法,以及一些相關的原理。

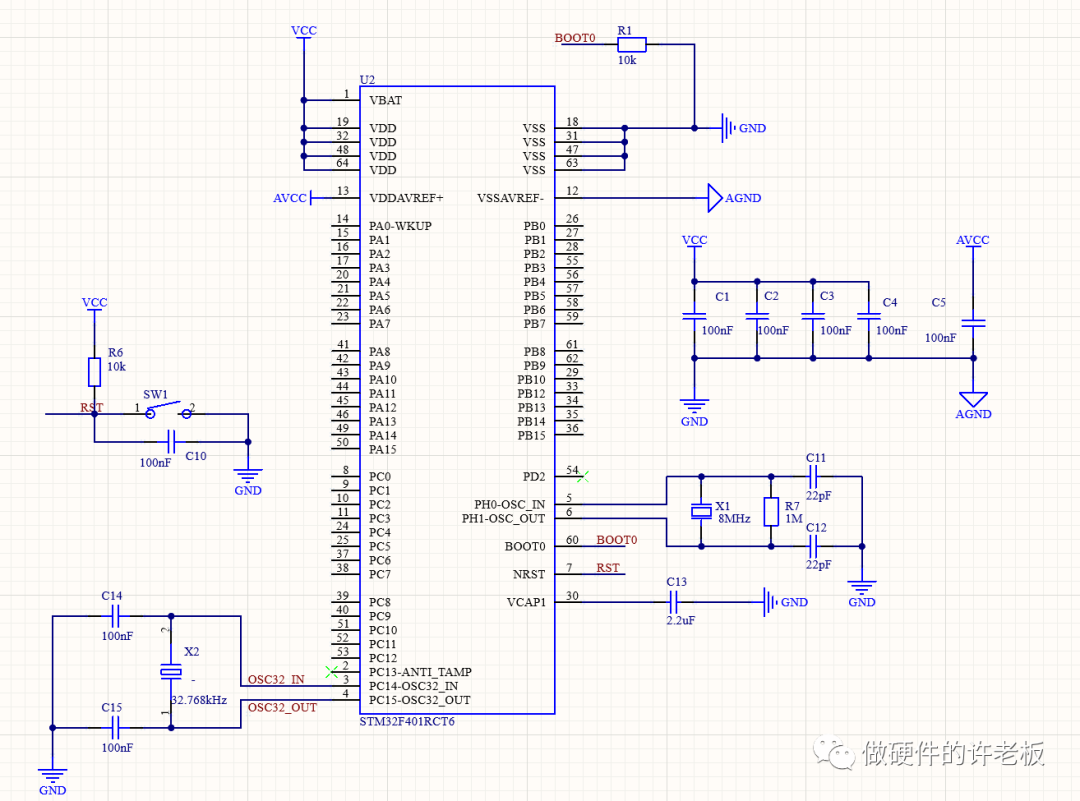

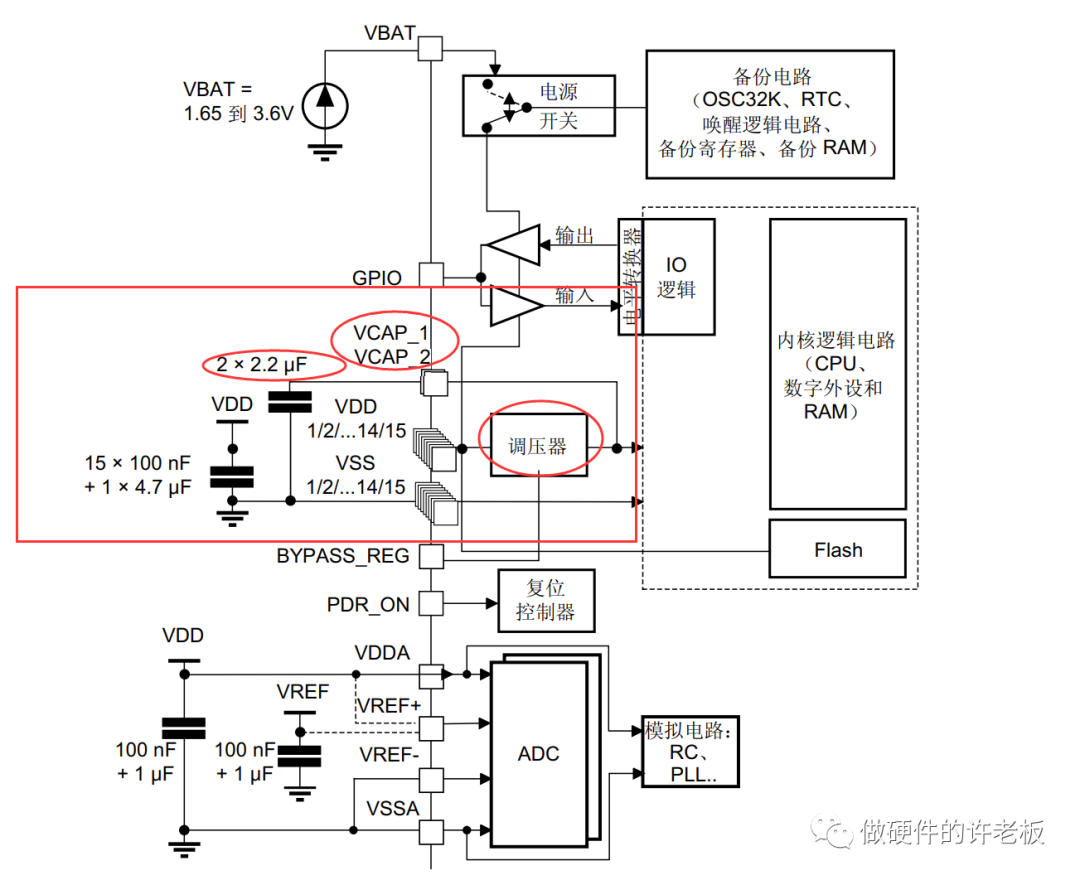

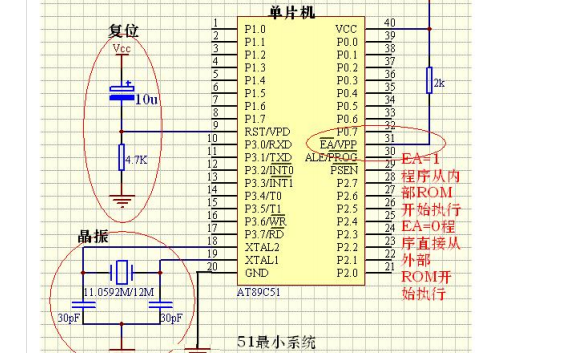

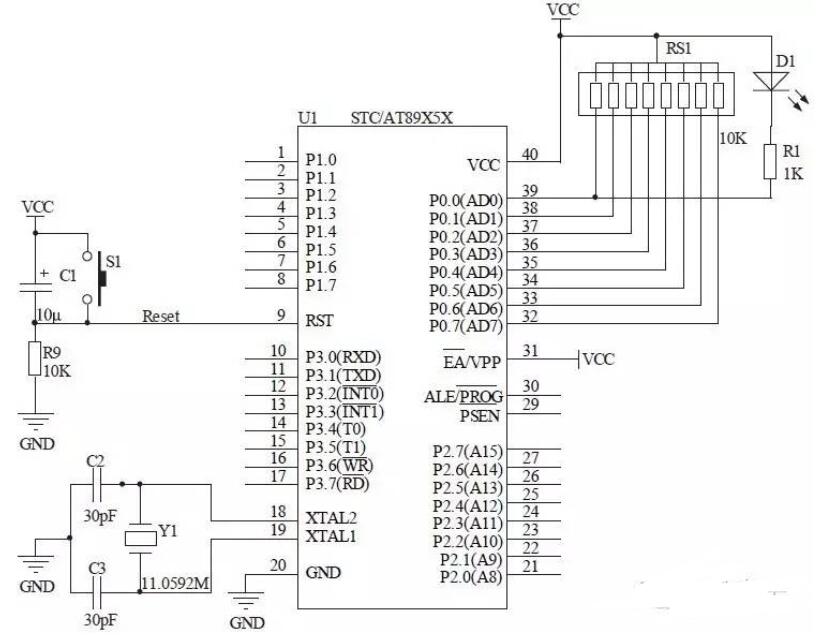

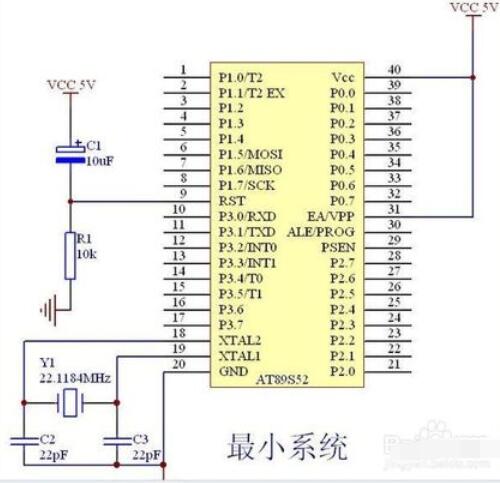

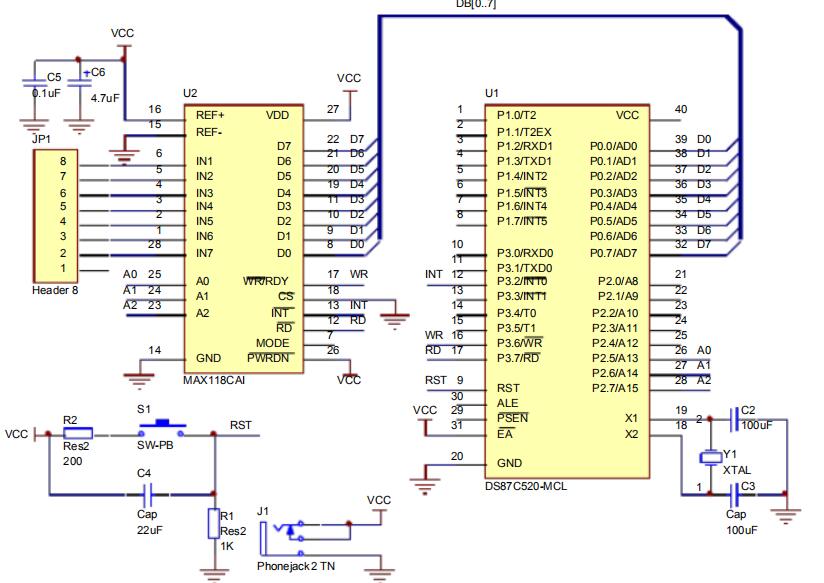

上圖所示即為單片機最小系統電路,我們將其分為三個部分,即電源電路、復位電路、時鐘電路。在了解最小電路之前,我們先看看下面幾個問題

- 設計最小系統電路的時候,常常在芯片的VDD和VSS之間連接一個104電容,為什么這些電容要放得離引腳足夠近?

- VDD和AVDD有什么區別?VSS和AVSS又有什么區別?

- 同樣是接地,為什么會有AGND和GND?為什么又會有VCC和AVCC?這些不同的電源和地在PCB設計的時候有什么注意事項?

- 為什么兩個標上OSC的引腳上都需要接晶振?這兩個引腳有什么不同嗎?晶振的作用是什么?

- 復位電路是如何實現復位的?單片機復位的具體原理是什么?

- VCAP引腳為什么需要接2.2uF電容?這跟芯片的供電有什么關系嗎?

如果這幾個問題難不倒你,那么本文的內容你也已經不需要再看了。如果你看懵了,那我們接下來就一個一個解決這些問題。

旁路電容和電源濾波

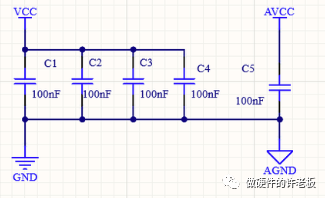

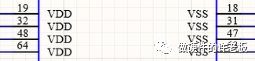

細心的朋友應該也發現了,放置的100nF電容的數量,正好和VDD、VSS引腳的數量相同。因此,在PCB設計時,需要把這些電容放置得距離芯片引腳足夠近,這些電容也被稱為旁路電容。

我們都知道,電容很重要的一個作用就是濾波,因此在供電電路中,經常需要放置電容來濾除雜波,使得高電平的電壓值更加穩定。因此,旁路電容的作用就是濾波。如果這些旁路電容距離單片機的VSS、VDD引腳太遠,就有可能導致濾波后的電平在傳輸過程中又產生了雜波,使得單片機的輸入輸出電壓參考出現了不準確的問題。

同樣的道理,AVCC和AGND之間的電容則需要放置在AVDD和AVSS之間,那么這就需要說到模擬信號和數字信號之間電路分割的問題了。

為了防止串擾,我們在設計PCB的時候常常會將模擬信號的電路和數字信號的電路分開,并在接地處僅僅使用一根銅導線連接。這里也是一樣,理論上AVCC和VCC的電平是一樣的,但是只能分開供電,因為模擬信號是具有連續性的,連在一起會干擾到數字信號的電平參考。

為什么AGND和GND需要用一根銅線相連?

因為整個板子需要共地。我們需要理解清楚的是,電流是從高電平流向低電平的,那么最后就必然會流回GND,而模擬信號是以不同大小的電平,數字信號卻只有高電平和低電平之分,因此,如果將整塊板子的GND都連接到一起,就會導致錯誤的回流。比如,我們的外設電路中有一個ADC采樣采集到了2V的電壓,如果這個時候的高電平參考是3.3V,那么就必須防止從這個2V高電平流出來的電流流入VSS引腳,而只能讓其流入AVSS引腳。而實際上,我們又需要保證GND和AGND的電平一致,所以就采取了這種多點接地的方式。

時鐘電路

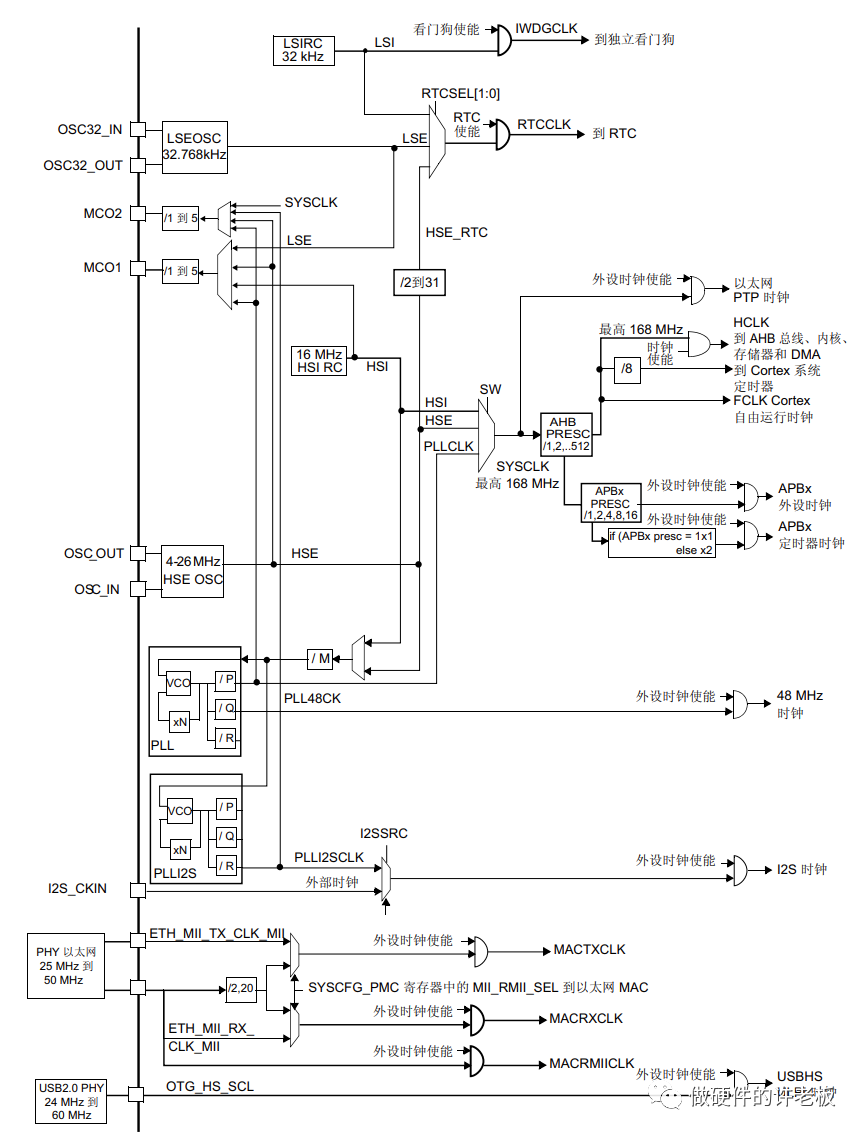

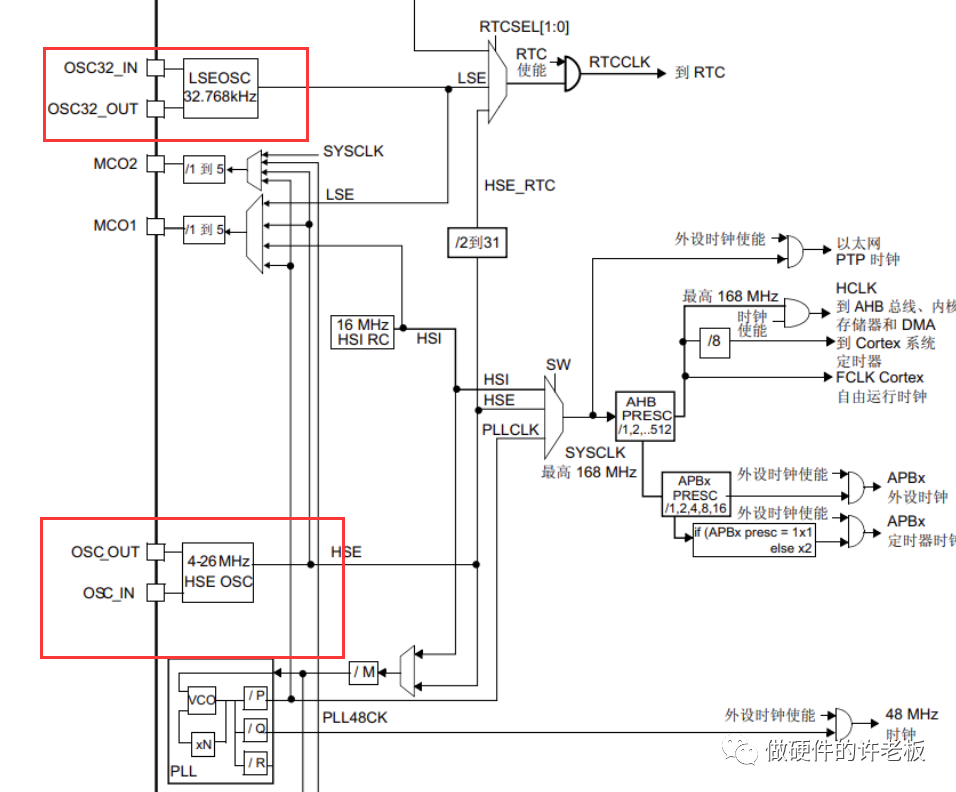

設計單片機的時鐘電路就必須先了解單片機時鐘信號的發生機制。《STM32F4xx參考手冊》中有這么一張時鐘樹

相信用過STM32CubeMX進行工程配置的小伙伴應該不會感到陌生。STM32可以使用三種不同的時鐘源來驅動系統時鐘 (SYSCLK),即 HSI振蕩器時鐘、HSE振蕩器時鐘和主PLL時鐘 。對于每個時鐘源來說,在未使用時都可單獨打開或者關閉,以降低功耗。

在這個時鐘樹里面,我們可以看到下圖紅框里的四個引腳,對應的就是我們時鐘電路的引腳。可以看到,在OSC32_IN和OSC32_OUT兩個引腳內部,標注的是LSEOSC 32.768kHz,在OSC_OUT和OSC_IN內部,標注的是4-26MHz HSE OSC。

細心的小伙伴應該發現了,OSC32引腳連接的晶振剛好是32.768kHz,OSC引腳連接的晶振是8MHz,正好介于4-26MHz之間。這里就要說到單片機的HSE時鐘和LSE時鐘了

HSE時鐘

HSE為高速外部時鐘信號(High-speed external clock),該信號有兩個時鐘源

- 外部用戶時鐘

外部用戶時鐘是通過外部輸入占空比約為 50% 的外部時鐘信號(方波、 正弦波或三角波)來驅動 OSC_IN 引腳,同時OSC_OUT引腳保持高阻態。該方法適用于有外部時鐘源,或者有其他信號發生器能夠提供信號的情況。

- 外部晶振/陶瓷諧振器

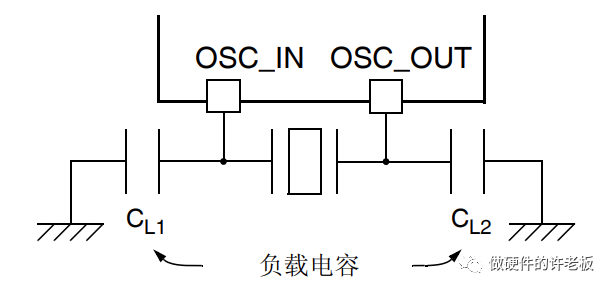

這也是我們設計電路時常常采用的方法,它的特點是精度高。

外部晶振的頻率范圍為4MHz~26MHz,本系統采用8MHz石英晶體作為系統的外部時鐘源,該高速外部時鐘可以直接作為系統時鐘或者PLL輸入。

大家可能會好奇,為什么這里的晶振兩端要并聯一個1MΩ電阻呢?

在無源晶振應用方案中,兩個外接電容能夠微調晶振產生的時鐘頻率。而并聯1MΩ電阻可以 幫助晶振起振 。因此,當發生程序啟動慢或不運行時,可以給晶振并聯1MΩ的電阻。這個1MΩ電阻可以增加電路中的負性阻抗,縮短了晶振起振時間,達到了晶振起振更容易之目的。

假設電路中無任何的擾動信號,那么晶振就不可能起振。因為一般的電路都有擾動信號,所以許多反相門電路中都不加這個電阻,但有個別的反相門電路不加這個電阻就不能起振,因為擾動信號強度不夠。同時,并聯1MΩ電阻還能夠增加振蕩電路的穩定性,有時候也給晶振同時串聯一個100Ω的電阻,用以減少晶振的頻率偏移程度。

這里需要注意的時,給晶振并聯電阻不能太小,串聯電阻不能太大。否則,在溫度較低的情況下不易起振。

LSE時鐘

LSE 晶振是 32.768 kHz 低速外部 (Low-speed external clock) 晶振或陶瓷諧振器,可作為實時時鐘外設 (RTC) 的 時鐘源來提供時鐘/日歷或其它定時功能,具有功耗低且精度高的優點。

與HSE時鐘類似,可以利用方波、三角波等信號驅動OUC32_IN引腳來實現外部時鐘源。同樣,也可以使用32.768 kHz晶振起振來實現時鐘信號的發生,其電路設計方法和HSE類似。

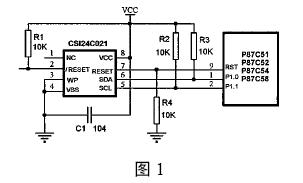

復位電路

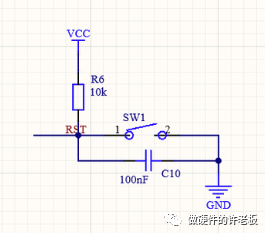

在STM32中,共有三種類型的復位,分別為 系統復位 、電源復位和 備份域復位 。關于這三種復位的方式有很多種,比如NRST引腳輸入低電平、窗口看門狗計數結束、獨立看門狗計數結束等。我們這里需要設計的電路就是NRST引腳低電平輸入電路。

有人可能會有疑惑,NRST輸入低電平的電路有什么好設計的?

的確沒什么好設計的,我們這里采取的是按鍵復位的方式,只需要讓按鍵按下后,NRST引腳電平拉低即可。唯一需要說的就是按鍵的硬件消抖,我這里放置抖動的方法是電容濾波。同時,NRST引腳需要通過一個上拉電阻,保證其在按鍵松開狀態下處于高電平。

由于我采用的芯片封裝是LQFP64,即芯片只有64個外露的引腳,因此沒有電源監視器開關控制管腳,即PDR_ON。這里需要注意的是,在有該引腳的芯片中,當PDR_ON接+3.3V時則為開啟電源監視器,當PDR_ON接GND時則為關閉電源監視器。只有當PDR_ON接高電平+3.3V時,系統上電復位電路才會正常工作實現上電復位的功能。

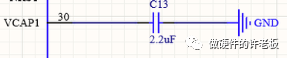

嵌入式線性調壓器

嵌入式線性調壓器為備份域和待機電路以外的所有數字電路供電。調壓器輸出電壓約為 1.2 V。此調壓器需要將兩個外部電容連接到專用引腳 VCAP_1 和 VCAP_2,所有封裝都配有這兩個引腳。為激活或停用調壓器,必須將特定引腳連接到 VSS 或 VDD。具體引腳與封裝有關,我們這里選的封裝是LQFP64,只有一個VCAP引腳,因此只需要連接一個電容。

查閱《STM32F4xx參考手冊》,即可知道VCAP需要連接一個2.2uF電容接地,如圖所示

最后

本文為我個人設計PCB的總結,希望能夠幫助到大家。由于個人能力有限,如有錯誤,歡迎直接指出,謝謝!

-

單片機

+關注

關注

6023文章

44375瀏覽量

628288 -

旁路電容

+關注

關注

7文章

178瀏覽量

24710 -

STM32

+關注

關注

2257文章

10826瀏覽量

352431 -

PCB設計

+關注

關注

394文章

4648瀏覽量

84525 -

最小系統

+關注

關注

9文章

249瀏覽量

28981

發布評論請先 登錄

相關推薦

2.2 單片機最小系統

單片機最小系統

單片機最小系統的設計方法和原理分析

單片機最小系統的設計方法和原理分析

評論