一、背景描述

板載的二次電源設計關乎單板的正常、可靠工作, 本文主要分享最近遇到的一個故障,從而提醒大家在板載二次電源設計中還需要重點關注這樣一個參數“斜坡時間Ramp Time”的設置。

二、故障現象

某交換機模塊,其核心是基于FPGA K7進行了擴展,出現了部分模塊上電后偶發無法正常啟動的情況,偶發的頻次還比較高,主要兩個關鍵信息:1)有模塊上電能一直正常工作,2)問題模塊有時也能上電正常工作。

經觀察出故障時FPGA的FLASH配置狀態LED,顯示未配置成功,對FPGA的相關電源電壓值和紋波進行測量也符合要求。

三、斜坡時間RampTime引入

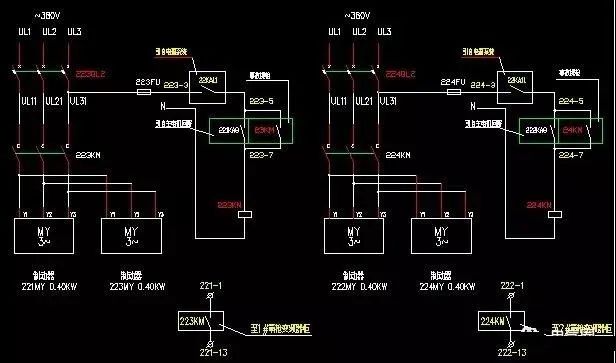

1、根據FPGA的配置手冊,FPGA配置流程分為8大步驟,第一步是Power-Up,如下圖所示:

2、在FPGA的Power-Up步驟,有如下的注意要求,即使FPGA和BPI flash共享同一個電源,兩者的響應也會不同時,因此需要特別關注FPGA和BPI flash的“上電順序power-on sequence”以及“上電斜坡power-on ramp”。

3、關于FPGA的上電順序power-on sequence如下圖所示,這塊通常大家都比較注意。

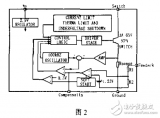

4、關于FPGA的上電斜坡power-on ramp要求如下圖所示,其中VCCO電源要求斜坡時間為0.2~50ms之間。

5、上電斜坡power-on ramp的時間如何設置?以我們常用的凌特46XX系列舉例,下圖來自LTM4620的軟啟動設置引腳TRACK的介紹以及軟起動ramp時間的設置公式,當電容選擇為100nF(0.1uF)時,根據公式100nF/1.3uA*0.6V=46ms,考慮到電容容值誤差(5%)以及后端容性負載的差異,ramp斜坡時間基本上在50ms左右,處于臨界值。

經過實際測量故障模塊的3.3V斜坡時間(上升沿時間)確實為50ms左右。

6、處理器的上電斜坡power-on ramp time示例:

1)P2020手冊中一方面明確了電源需要在50ms內到達穩定值,可以認為ramp time<50ms;另一方面規定了ramp rate的最大值為3600V/s,換算為ramp time以1V電壓為例,即等于1/3600=0.277ms;則我們認為P2020的ramp time在0.277~50ms之間。

2)T2080手冊中一方面明確了電源需要在75ms內到達穩定值,可以認為ramp time<75ms;另一方面規定了ramp rate的最大值為25V/ms,換算為ramp time以1V電壓為例,即等于1/2500=0.4ms;則我們認為T2080的ramp time在0.4~75ms之間。

四、補充說明

1、在板載二次電源設計時,斜坡時間Ramp Time也很重要,需要特別注意,上升沿太陡峭會引入過流保護、沖擊電流等問題,上升沿太緩會影響各芯片正常工作的先后時序等問題,需要根據具體的數據手冊選擇合適的Ramp Time時間,通常在5~10ms之間為優。

2、對于電源芯片的選用以及電路設計上,關注Ramp Time的相關設置,對于凌特系列可通過TRACK引腳上電容大小按公式進行調整,通常可選擇10nF級別左右。

3、硬件系統的可靠性需要更多精益求精的設計。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601843 -

電源設計

+關注

關注

30文章

1531瀏覽量

66297 -

FlaSh

+關注

關注

10文章

1621瀏覽量

147754 -

交換機

+關注

關注

21文章

2622瀏覽量

99258 -

二次電源

+關注

關注

0文章

8瀏覽量

9374

發布評論請先 登錄

相關推薦

二次電池的特性和應用

什么是二次諧波?二次諧波的定義?

二次電池是什么_二次電池有哪些_二次電池充放電方程式

二次回路的作用

什么是一次電源?什么是二次電源?資料下載

DCDC二次電源輻射特性研究

航天器平臺二次電源系統的可靠性設計

板載二次電源設計中斜坡時間Ramp Time的設置

板載二次電源設計中斜坡時間Ramp Time的設置

評論