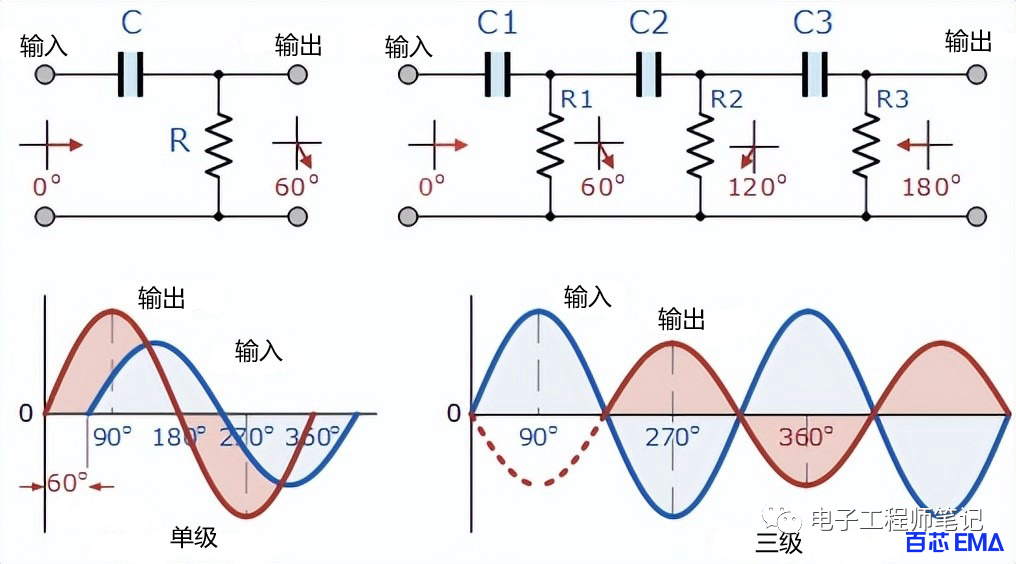

1. 奇數級振蕩器

1.1 基于反相器的振蕩器

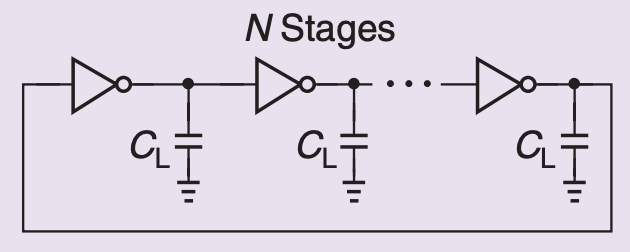

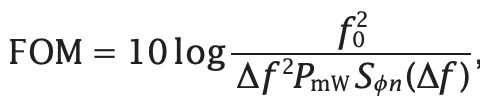

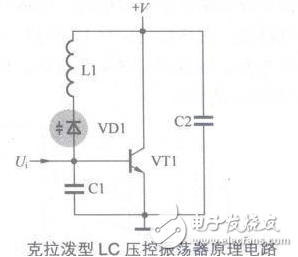

圖一

如圖一,假設振蕩器由N級反相器組成,N必須為奇數,以保證電路DC時為負反饋。每級反相器延時TD,振蕩周期為2NTD。這樣的振蕩器有三個特點:一,供電電壓VDD越高,每級延時越短,因此振蕩頻率f0和供電電壓VDD成正相關。二,假設每級反相器負載電容為CL,總功率約等于Nf0CLVDD^2。三,提供每級相位差為180°/N的N個輸出信號(DC負反饋本身提供180°相移,那么NTD再產生180°相移,即可滿足360°相移的振蕩條件)。

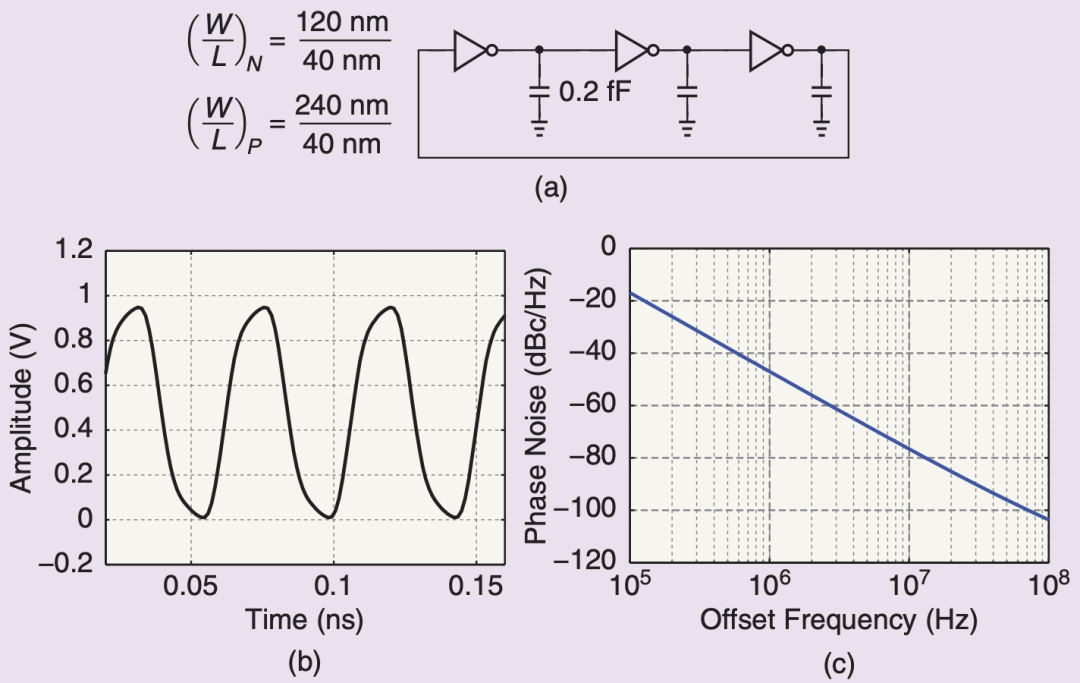

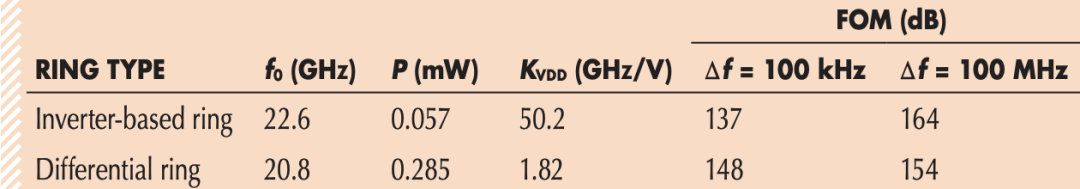

圖二

原作者設計了一個實際的振蕩器,如圖二。具體參數如下:f0=22.6GHz,功耗57uW,電源電壓到輸出頻率的增益KVDD=50.2GHz/V,是一個非常高的數值。如圖二(c),相位噪聲隨著offset頻率的下降速率為30dB/dec,說明閃爍噪聲是主導因素。

據原文,改善相位噪聲有一個方法,叫做線性縮放(linear scaling):將所有晶體管尺寸(W/L)增大到M倍,假設版圖寄生可以一定比例縮放,保證f0和KVDD保持不變,那么相位噪聲就可以降低10*log(M)。例如,將圖二(a)晶體管尺寸增加100倍,相位噪聲可以減少20dBc/Hz。這樣做的代價是晶體管等效阻抗減小,為保持頻率不變,各節點電容增加,那么功耗也增加了。在這個例子中功耗會增大到5.7mW。當然,面積也會同比例增加。

1.2 基于全差分運放的振蕩器

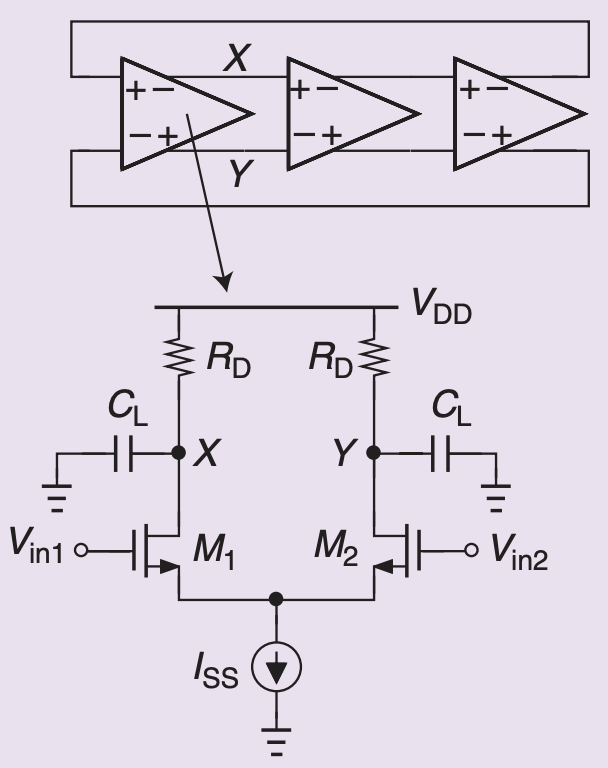

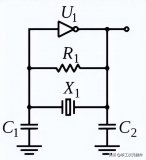

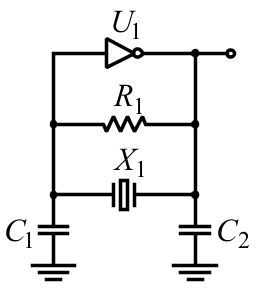

圖三

如圖三,這種差分振蕩器和前面的反相器式振蕩器有四點不同:一,對電源VDD不敏感,因為每一級延時是由RDCL來決定的。二,各內部節點,如X/Y點的單端最大擺幅為ISSRD,不能實現軌到軌輸出。三,可以用偶數級實現振蕩器,只需要將其中一級的輸入反接。四,有靜態電流。

針對第二點,有兩個地方需要補充說明。一個是晶體管的尺寸選取,W/L需要足夠大,這樣可以保證每一級輸出達到滿擺幅時所需的輸入差分電壓小于ISSRD,那么在輸入滿擺幅(ISSRD)時,輸入對管其中之一(M1或M2)可以完全關斷。二是對于三級振蕩器,即便可以實現振蕩,但會因為整個環路延時太短而無法實現完全的切換,那么每個節點都無法實現滿擺幅(ISSRD)振蕩。根據現有文獻,振蕩擺幅約為0.5ISS*RD。

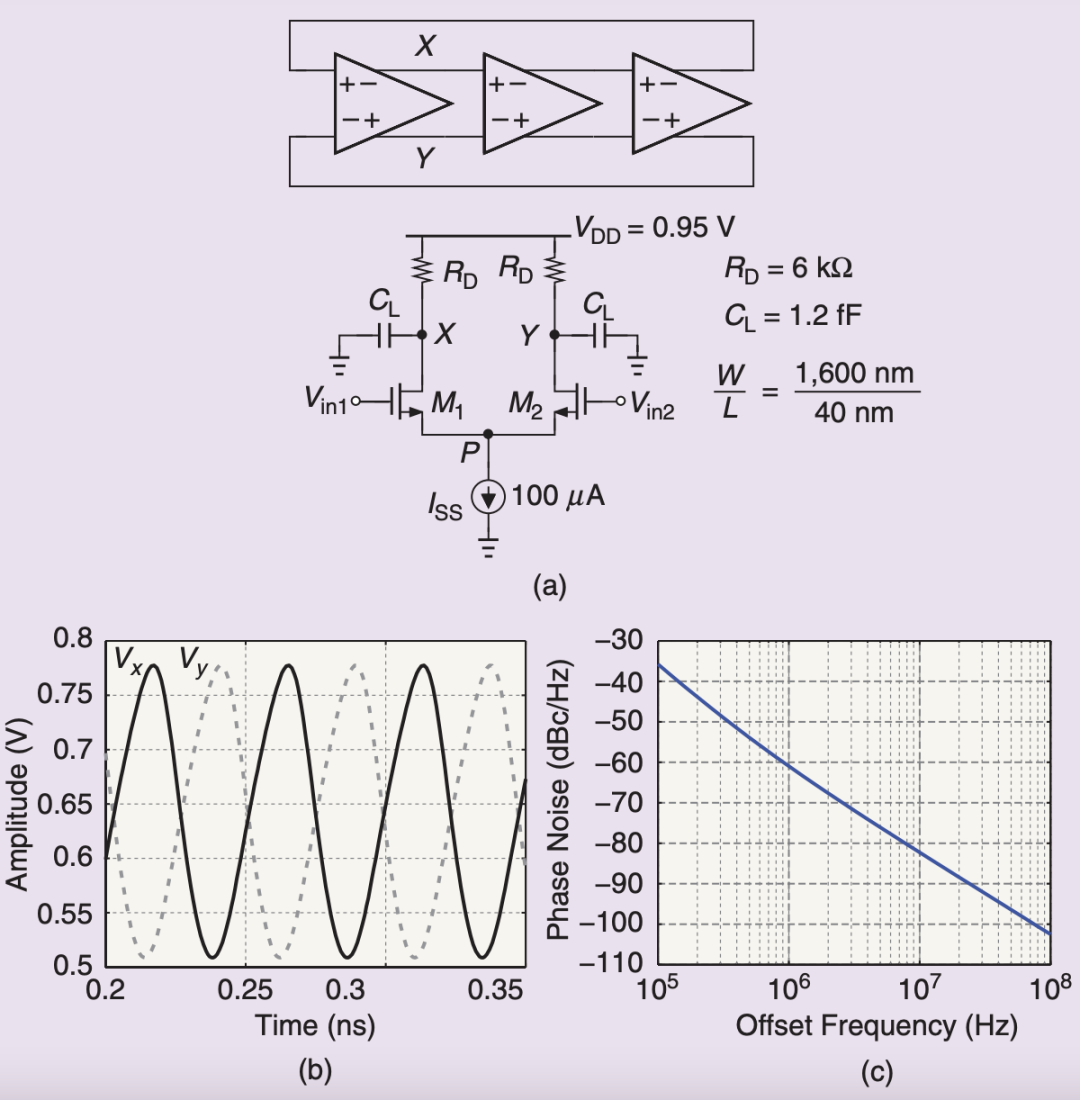

圖四

作為對比,原作者設計了一個振蕩頻率和圖二差不多的差分振蕩器,如圖四。f0=20.8GHz,功耗285uW,電源電壓到輸出頻率的增益KVDD=1.82GHz/V,比圖二小得多。從圖四(b)看到的擺幅為270mV,和前面預估的0.5*ISS*RD=300mV差不多。根據圖四(c),相位噪聲的下降斜率從1MHz以下的-30dB/dec過渡為之后的-20dB/dec,意味著和圖二相比,閃爍噪聲的比重降低。

為了減小相位噪聲,線性縮放的方法依然是可行的。在這里,需要將M1/M2的W/L和ISS增大M倍,同時將RD減小M倍。

1.3 總結與對比

為了實現兩種結構的公平對比,作者定義了一個figure of merit (FOM):

其中,Δf為offset頻率,PmW為功耗,Sφn(Δf)為在該offset頻率下的相位噪聲。FOM越大,性能越好。

表一

表一對比了兩種振蕩器的差別。在Δf=100kHz時,反相器式振蕩器性能更差,這是因為此時頻率低,閃爍噪聲顯著,而反相器式振蕩器的相位噪聲由閃爍噪聲主導。在Δf=100MHz時,差分振蕩器性能更差,因為此時閃爍噪聲降低,熱噪聲主導了相位噪聲,而差分振蕩器輸出擺幅更小,熱噪聲影響更大。事實上,反相器式輸出擺幅約為差分式的3.5倍(11dB),而這也和兩者在100MHz的FOM之差相當。

2. 偶數級振蕩器

2.1 四級全差分振蕩器

前面提到,全差分振蕩器容易做成偶數級,只需要其中一級輸入反接即可。那么在圖三的基礎上增加一級即可構成四級振蕩器,每級相位差為45°。相比三級振蕩器,由于級數增加,可以預期每級擺幅增加。然而,為了保證功耗不變,ISS需要減小。從相位噪聲的角度來看,這兩個因素可以互相抵消一部分。根據仿真,FOM約降低1dB。

2.2 四級反相器式振蕩器

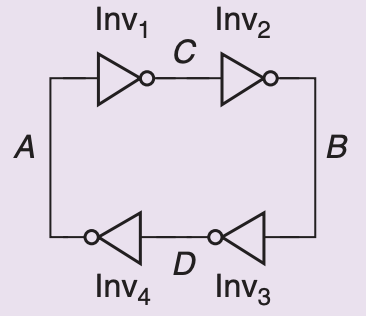

圖五

反相器式振蕩器一般不可直接用偶數級實現,這是因為偶數級在DC情況下是正反饋,會導致電路在DC情況被鎖住。如圖五,假設A=1,C=0,B=1,D=0,電路會一直latch在這種狀態。但是,如果忽略這種latch的情況,電路是否有可能在某個頻率振蕩?答案是肯定的。假設每級延時為TD,考慮到DC正反饋未提供額外的相移,環路總延時4*TD需要達到360°則有可能振蕩。那么每級相位差為360°/4=90°,振蕩周期為4*TD。此時A和B相位差180°,C和D相位差180°,和DC情況下的A=B,C=D不同。那么,是否只要我們規避了DC的latch狀態,就可以實現振蕩?

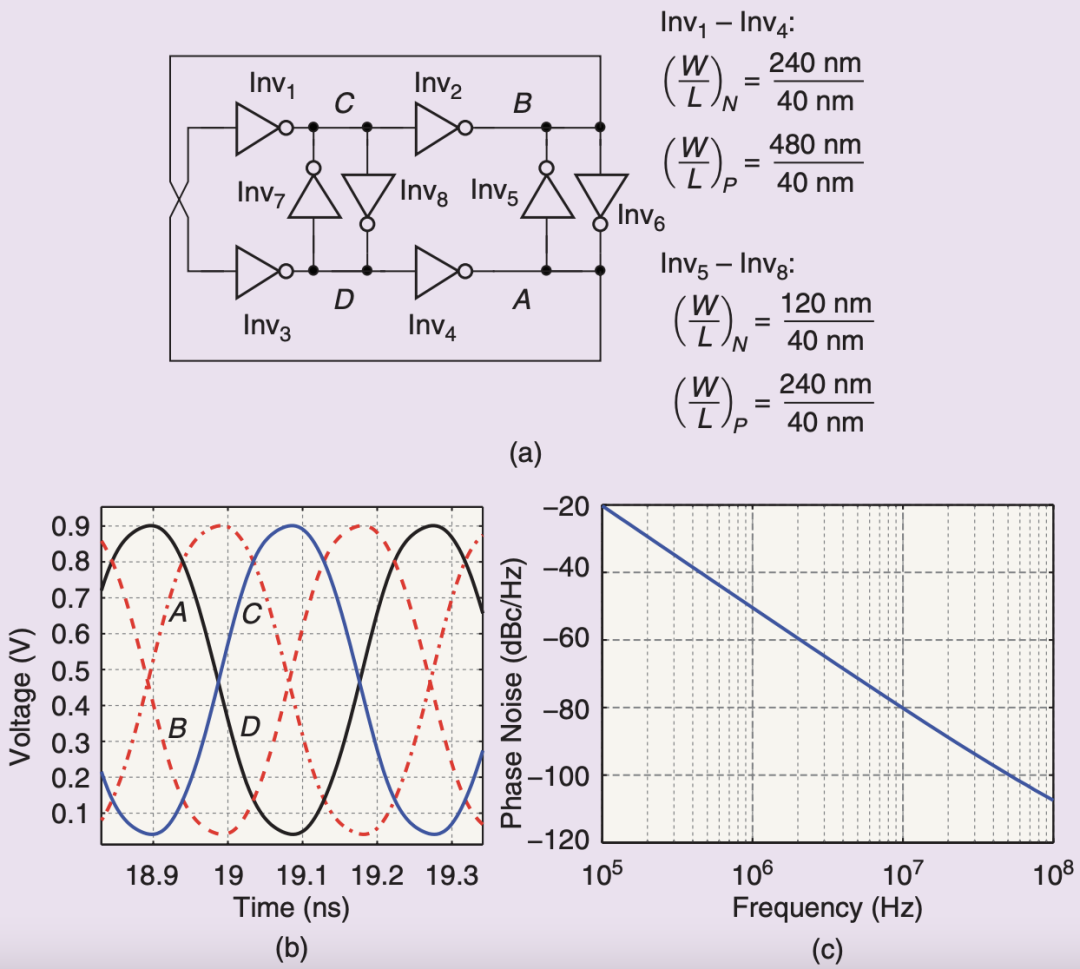

圖六

出于前面的想法,設計電路如圖六。這個畫法不容易看懂,但實際上就是在圖五的基礎上,在A/B之間和C/D之間插入inverter-based latch(Inv5 ~ 8),保證不會因為兩對節點相同而在DC情況下鎖住。對于Inv5 ~ 8的尺寸選取需要注意,一方面需要足夠大尺寸,保證可以實現避免自鎖的功能;另一方面,由于Inv5 ~ 8會和Inv14競爭,如果Inv58尺寸過大,會導致功耗和噪聲增加。

圖六中的設計指標如下:f0=26.5GHz,電流為235μA(三級振蕩器為60μA)。根據計算,相比三級振蕩器,總的FOM降低了1.5dB。這就是采用偶數級結構的成本。

-

振蕩器

+關注

關注

28文章

3813瀏覽量

138873 -

反相器

+關注

關注

6文章

310瀏覽量

43243 -

負載電容

+關注

關注

0文章

137瀏覽量

10428

發布評論請先 登錄

相關推薦

一文詳解振蕩器

振蕩器,振蕩器的分類,振蕩器的特性

振蕩器,振蕩器的分類和原理是什么?

壓控振蕩器,壓控振蕩器是什么意思

壓控振蕩器電路圖大全(八款壓控振蕩器電路設計原理圖詳解)

什么是皮爾斯振蕩器?皮爾斯振蕩器電路如何工作?

振蕩器原理詳解(2)

振蕩器原理詳解(2)

評論