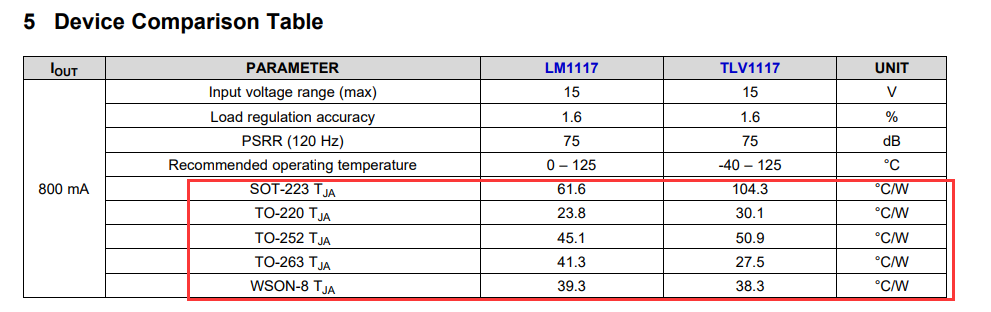

文章一開始介紹了LDO的歷史和由來,以及為什么需要LDO這個東西。像在鎖相環(huán)或者SAR ADC這樣的系統里,由于不同模塊的瞬態(tài)電流具有不同的頻率分量,為防止模塊之間的干擾,一般不會共享同一個電源。也就是說,每個模塊需要一個單獨的LDO。那么LDO的設計就顯得尤為重要。

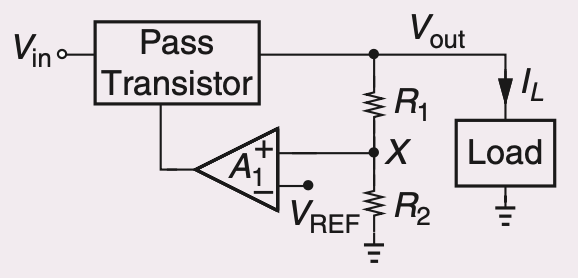

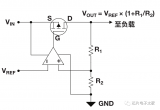

圖一是一個基礎的regulator的結構。其中pass transistor有兩種選擇,PMOS或者NMOS。前者是作為電流源的形式,后者是source follower輸出。通常,我們將PMOS的regulator稱為LDO。

圖一

除了dropout以外,無論哪種類型,需要關注的參數都是以下幾點:

- PSR :Vin到Vout的增益,越小越好。來源有兩條路,一是pass transistor,二是運放。

- 輸出噪聲

- load regulation :負載電流變化引起的Vout變化,也就是IL到Vout的增益,和regulator輸出阻抗直接相關。

- 功耗和面積

原文是將這幾個指標雜糅在一起講的,本文希望按順序逐個整理總結。出于篇幅考量,這里就只講PSR,其余指標會在之后的文章中總結補充。

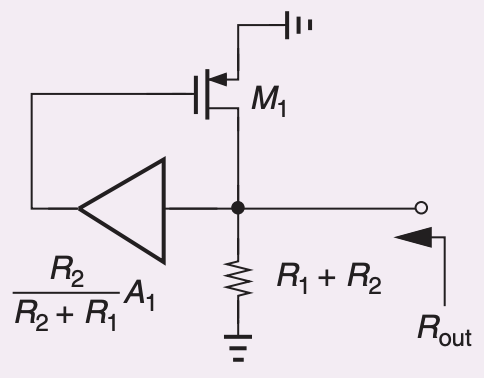

那么首先看一下PMOS作電流源的regulator,如圖二。

圖二

從運放輸入正極斷開,容易得出環(huán)路增益的表達式如下:

可以認為運放將M1的跨導等效增大了A1倍。

如何計算PSR呢?一個簡單做法是將此結構簡化為圖三的形式,將電阻分壓比直接乘到運放開環(huán)增益上,再推導Vin到Vout的傳遞函數。

圖三

首先假設M1的ro1無窮大,那么Vin到Vout的前向通路表達式可以等效為一個共柵極放大器的增益,PSR可以直接寫為:

分母剛好是1+ALG(分母第一個R2為筆誤,應該是RL),分子則是前向通路的增益。容易看出, A1越大,電源抑制越好。 在ALG>>1的情況下,此式可以簡化為:

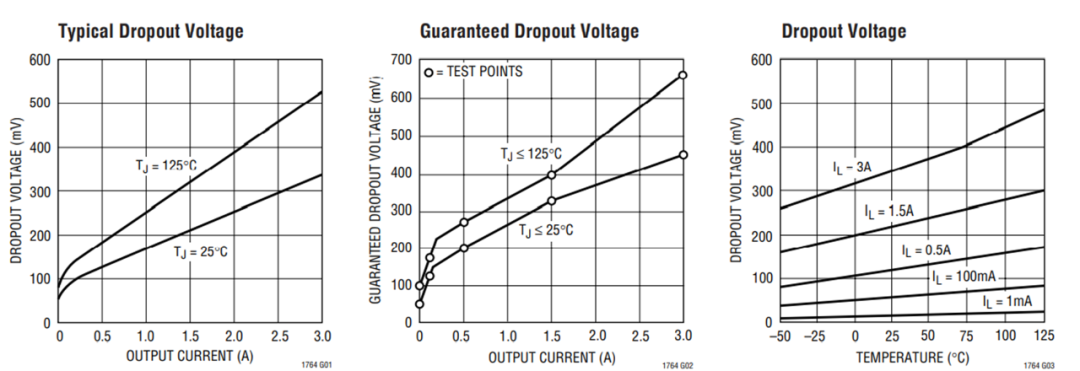

考慮到主極點之后運放增益會衰減,高頻下的PSR會隨著運放增益的衰減而變差,如圖四。

圖四

因此,LDO需要一個高增益,大帶寬的運放以獲得較好的PSR。

另外一種做法是在輸出端對地加一個大電容CM,那么表達式可重新推導為:

加電容后在輸出端引入一個極點1/(RCM),假設此極點高于運放主極點ω0,則圖四曲線開始會在ω0處上升,在1/(RCM)后抑制上升趨勢。高頻下CM減小輸出節(jié)點對地阻抗,從分壓的角度也可以看出Vin到Vout的增益會減小。

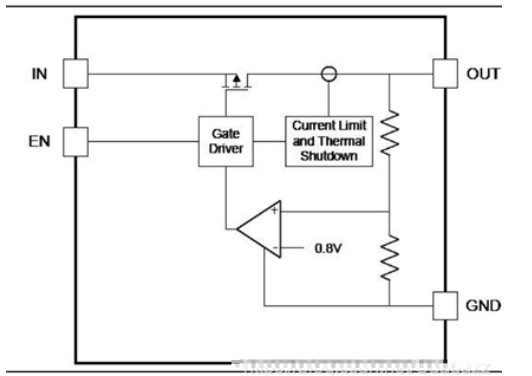

另外單獨考慮ro1對電源抑制的影響,此時忽略M1的受控源部分,那么PSR就是Rout和ro1的分壓比,如圖五。

圖五

假設RL>>Rout,這部分的PSR表達式為:

Vout/Vin =Rout/(ro1 +Rout) =(1+R1/R2)/(gm1ro1A1 +1+R1/R2)

依然是A1越大越好,同時M1的本征增益也是越大越好。但由于這一部分PSR相比圖三那一部分小了幾乎是一個gm1*ro1倍,認為這一部分的貢獻可以忽略。

討論完M1的通路對PSR的貢獻,另外考慮運放自身的PSR對系統PSR的影響。

圖六

如圖六,假設運放的供電和LDO主功率路徑無關,運放電源的擾動為VnDD,此擾動到運放輸出端的增益為β(也就是運放自身的PSR),我們可以很容易地推導出VnDD到Vn,out的表達式:

基本思路是從運放輸出倒推到運放輸入,再通過電阻分壓推導至LDO輸出。從表達式可以看出,想要弱化運放自身PSR對LDO整體PSR的貢獻,需要盡可能地 增大A1,同時改善運放自身的PSR(減小β) 。這和我們之前的目標是一致的。

那么,如果運放的供電和LDO主功率路徑是同一個電源呢?

圖七

以圖七為例,假如采用一個簡單的NMOS輸入的五管運放,DC情況下Mc的 VGS是一定的,因此Vin上的擾動會直接引起P點發(fā)生相同的變化,而穩(wěn)定情況下VF又應該等于P點電壓,因此五管運放的β=1,自身的PSR是很差的。但事實上,如果Vin的變化引起了VF有同樣的變化,意味著M1的VGS趨于恒定,則LDO的輸出電壓更不容易受到Vin變化的影響,那么LDO整體的PSR反而更好。也就是說,在同一個電源供電下,五管運放PSR差的特點反而有助于改善LDO的PSR。

另外,拉扎維也提到一點,想要減輕運放自身PSR對LDO整體PSR的影響,有一種思路是用輸出電壓給運放供電。

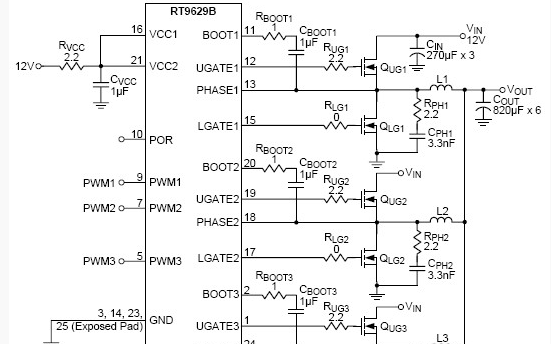

分析完PMOS型的regulator之后,讓我們來看一下NMOS型的regulator,如圖八。

圖八

如果不考慮M1的溝道長度調制效應,那么這種結構擁有完美的電源抑制能力,Vin到Vout的增益為0。

如果考慮M1的溝道長度調制效應,則按照前面的方法來分析,如圖九。

圖九

忽略M1的受控源部分,只考慮ro1和Rout的分壓,可以得到表達式如下:

和PMOS型regulator相比,此時分母上多了gm1*ro1的系數,也就是減小了M1的本征增益倍。因此, 即便考慮非理想因素,NMOS型regulator依然有明顯更好的PSR 。

對于regulator的PSR分析就到此結束啦,之后的文章里會補充LDO的其他指標分析,欲知后事如何,且聽下回分解~

-

負載電流

+關注

關注

1文章

247瀏覽量

14313 -

鎖相環(huán)

+關注

關注

35文章

583瀏覽量

87699 -

ldo

+關注

關注

35文章

1919瀏覽量

153188 -

adc

+關注

關注

98文章

6452瀏覽量

544144 -

運放

+關注

關注

47文章

1155瀏覽量

52982

發(fā)布評論請先 登錄

相關推薦

LDO的參數指標分析(2)

LDO的參數指標分析(1)

LDO的參數指標分析(1)

評論