一、LVDS概述

1) LVDS: 英文全稱Low-Voltage Differential Signaling,中文全稱:低電壓差分信號,其基本特點即:“低電壓”、“差分”,引申特點“高速”、“低功耗”、“抗干擾”、“低輻射”。

2) LVDS可認為僅定義“物理層”標準,其僅定義了相關的電氣特性,因此也可被其他協議標準借用為其物理層接口。

3) LVDS相關規范標準:TIA/EIA-644 規范、IEEE1596.3規范。

4) 使用場景:點對點,高速數據傳輸,比如ADC接口、視頻接口等,也可用于板內、背板、電纜等數據傳輸。

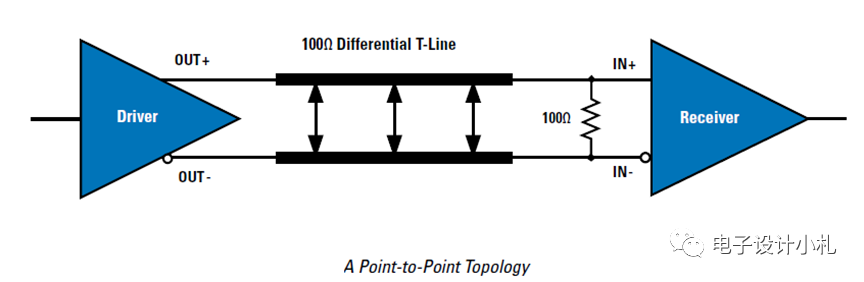

二、拓撲結構

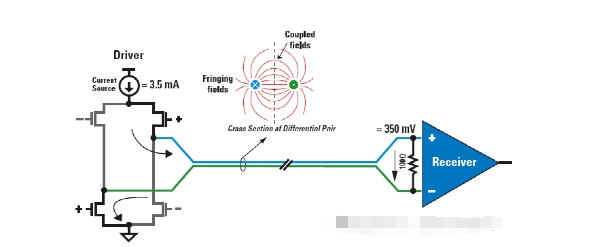

如上圖,一個LVDS傳輸鏈路, 包含四種組件,LVDS驅動器、LVDS接收器、LVDS差分傳輸介質、終端匹配電阻 ,其中:

LVDS驅動器實現單端轉差分LVDS信號;

LVDS接收器實現差分LVDS轉單端信號;

LVDS差分傳輸線由兩根(一對)差分信號線組成,可以是PCB走線、也可以是線纜;

終端匹配電阻:一般為100歐,一方面以便在接收器正負兩端形成0.35V的壓差,一方面作為端接電阻防止信號反射。

為了提升傳輸的帶寬,可以選擇多組LVDS傳輸鏈路進行傳輸,類似于PCIe的X2,X4這種。

其拓撲結構為點對點傳輸,對于多點傳輸的MLVDS這里先不考慮。

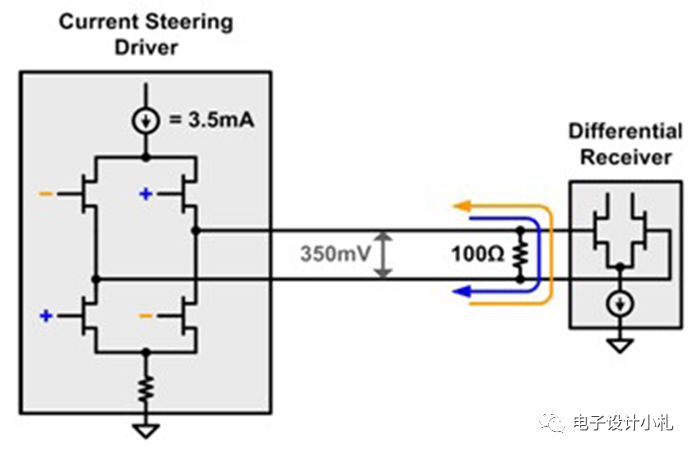

三、工作原理

如上圖可知,LVDS驅動端有個3.5mA的恒流源驅動,同時由4個MOS管形成了全橋開關電路,通過4個MOS管的開關,控制3.5mA恒流源輸出的電流方向;而接收器端在同相和反相之間并聯了一個100Ω端接電阻,通過端接電阻可產生3.5mA*100Ω=0.35V的電壓壓降,該壓降經過接收端電平判斷可形成高低電平。

依據上圖的電路結構,可知LVDS是一個電流驅動型接口,需要依賴外部電阻產生電壓, 如果單獨測量驅動端(端口懸空)是無法測量到電壓信號的 ,這與我們常規的CMOS電壓驅動型信號還是有所區別的。

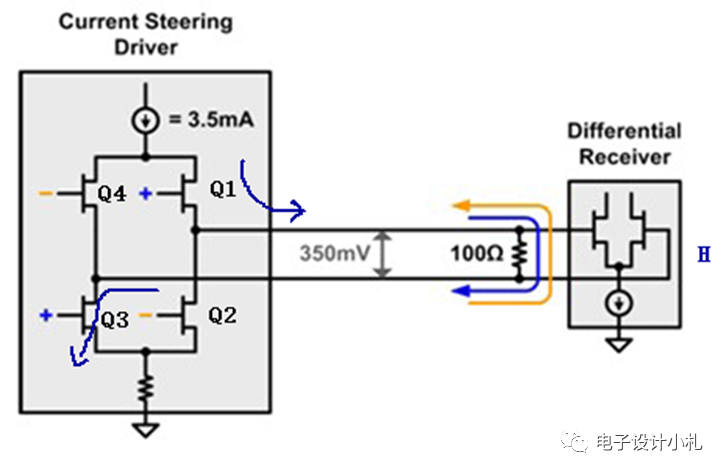

具體高電平產生示意如下圖藍色箭頭所示,當Q1和Q3導通,Q2和Q4截止,恒流源3.5mA電流分別經過Q1、100歐端接電阻、Q3,最后經過偏置電阻到GND,接收端輸入阻抗較大,則3.5mA基本全部經過100歐電阻,形成了350mV的正向電壓差,即認為輸出為“H”。

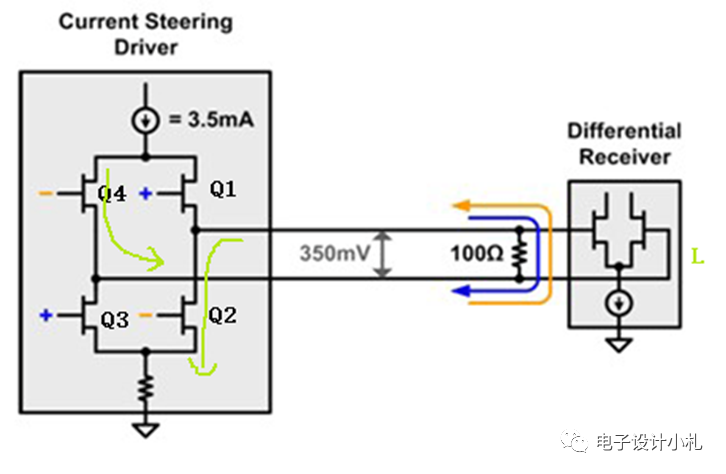

具體低電平產生示意如下圖橙色箭頭所示,當Q2和Q4導通,Q1和Q3截止,恒流源3.5mA電流分別經過Q4、100歐端接電阻、Q2,最后經過偏置電阻到GND,一般接收端輸入阻抗較大,則3.5mA基本全部經過100歐電阻,形成了350mV的負向電壓差,即認為輸出為“L”。

四、電氣特性

1)輸出特性(對發送端來說)

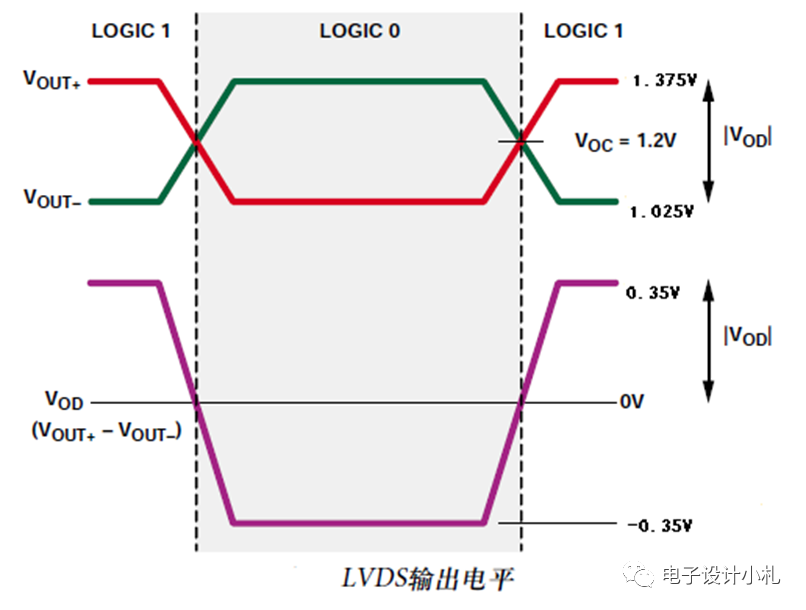

如上圖所示,對LVDS而言,正端輸出信號VOUT+:邏輯1為高電平,邏輯0為低電平,負端輸出信號VOUT-:邏輯1為低電平,邏輯0為高電平。

這里面有兩個概念,一個是差分電壓,一個是共模電壓,其中:

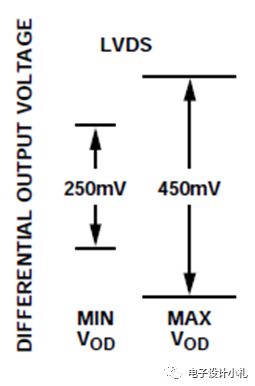

差分電壓=“VOUT+”與“VOUT-”之間的電壓差,可為正,也可為負,通常以|VOD|表示;VOD按照上文的原理分析,一般電壓差為350mV,但是在實際過程中有個范圍(如下圖),一般在250mV~450mV之間。

共模電壓=“VOUT+”與“VOUT-”的中心電壓,通常以VOC表示,共模電壓在實際不同的芯片中也有不同,通常情況下對于2.5V/3.3V/5V供電的設備,其VOC一般為1.2V,但是對于1.8V供電的設備,其VOC一般可能為0.9V。

2)輸入特性(對接收端來說)

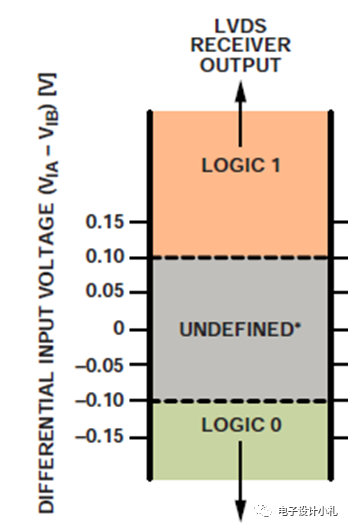

對于接收端來說,也有同樣的共模電壓VIC和差分電壓VID概念,接收端針對這兩個特性分別有要求,其中:

差分電壓會有個判決門限(如下圖所示),正VID >= +100 mV對應于邏輯1,負VID <=?100 mV則對應于邏輯0。

需要特別說明的是,如果差分電壓在兩個閾值之間,則LVDS接收器輸出為未定義態,可能為高電平或低電平。比如說LVDS接收器件輸入端短路或者開路時,就會發生這種情況,現在新一代的LVDS接收器通常會避免這樣的情況,被稱為fail-safe, 具體參照前面的這篇文章。

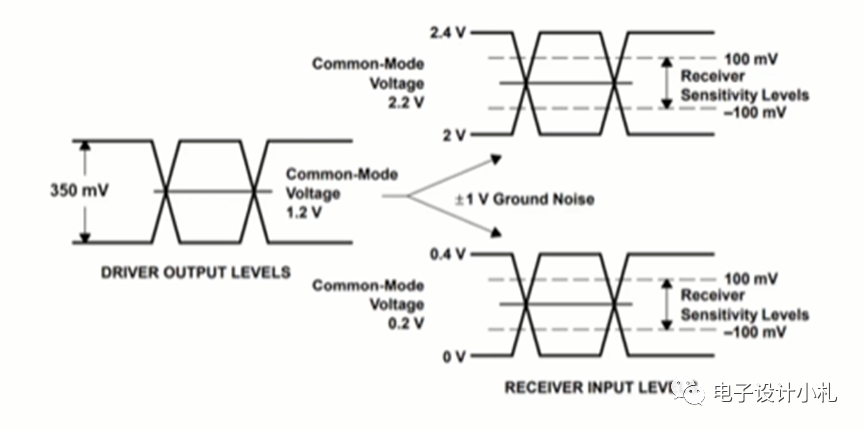

需要重點說的是,由前面的介紹可以知道,LVDS信號為電流驅動型,通常采用直流耦合的方式進行, 因此LVDS的發送端和接收端是需要進行共地處理的,這塊尤其注意,只不過對于共地的要求不是特別高,允許兩端有一定的地電勢差(如下圖所示) ,通常允許兩端的地電勢差在±1V之間。(當然現在也有一些自帶隔離型的LVDS器件)

3)傳輸線

LVDS傳輸線可以為導線,也可以為PCB走線,其走線長度從幾十厘米到10米這樣的范圍,其傳輸速率能夠達到3.125Gbps這樣的速率,當然傳輸速率與傳輸距離是成反比的,當100Mbps的時可以達到10米,當3.125Gbps時只能小幾十厘米,準確的距離還受傳輸介質、阻抗匹配等影響,需要通過仿真去評估。

五、應用說明

1) 應用場景:點對點傳輸、低功耗,LVDS速率最高可>3.125Gbps,傳輸距離最長可達到10m左右,但需要關注速率、傳輸介質與傳輸距離的關系等;

2) 原理圖設計時,需要關注接收端并聯端接100歐電阻,同時關注LVDS兩端的共地情況,有些時候端接電阻會內置在接受端內部;

3) PCB設計時,主要關注差分信號的等長、阻抗匹配,以及端接電阻緊貼著LVDS接收端器件放置(離發送端器件最遠處)。

-

驅動器

+關注

關注

52文章

8154瀏覽量

145997 -

接口

+關注

關注

33文章

8496瀏覽量

150834 -

電平

+關注

關注

5文章

359瀏覽量

39853 -

lvds

+關注

關注

2文章

1036瀏覽量

65700

發布評論請先 登錄

相關推薦

lvds接口與其他接口比較

lvds接口適用于哪些設備 lvds接口兼容性問題解析

lvds接口傳輸距離限制 lvds接口優勢及劣勢分析

lvds接口和HDMI的區別 lvds接口電路設計技巧

lvds接口用途與應用 lvds接口連接方法指南

edp接口和lvds接口區別 edp接口和lvds接口能混用嗎

lvds接口需要驅動嗎

edp接口和lvds接口能混用嗎

FPGA學習筆記-入門

請問AD7626 FPGA LVDS電平標準如何選擇?

高速論壇講座回放|?LVDS接口舊話新說&誤碼判定的邏輯

電平標準LVDS接口學習筆記

電平標準LVDS接口學習筆記

評論