傳輸線在阻抗匹配時串聯端接電阻為什么要靠近發(fā)送端?

傳輸線在阻抗匹配時,串聯端接電阻靠近發(fā)送端的原因有多個方面。

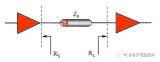

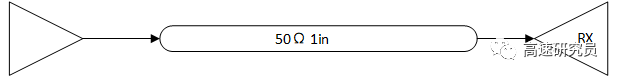

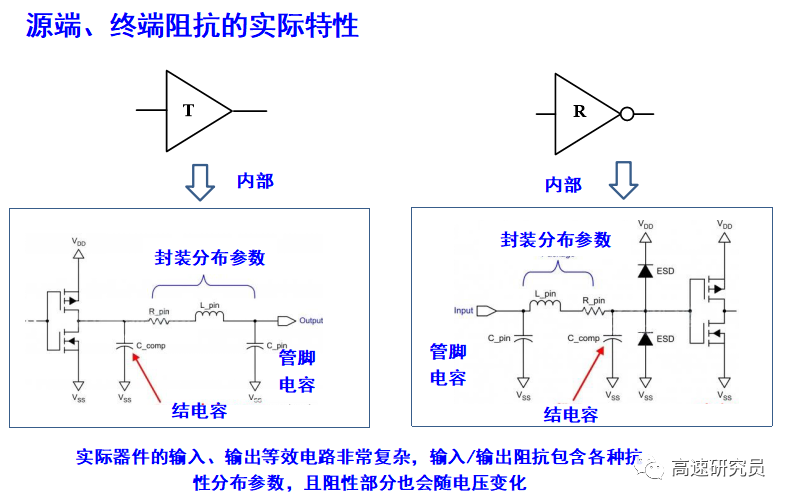

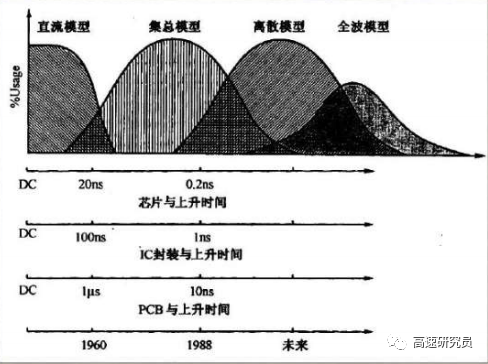

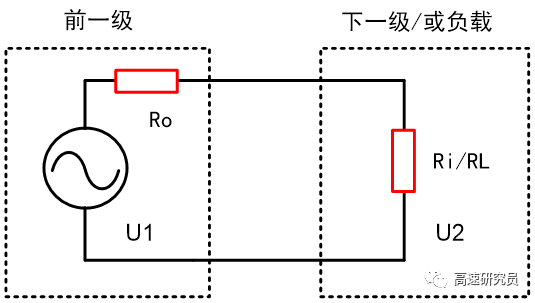

首先,了解傳輸線的基本原理是必要的。傳輸線是用于傳輸電信號的導體,如電纜或微帶線。它有一個特定的阻抗,通常以歐姆表示,表示為電阻和電抗的復數組合。傳輸線的負載阻抗與傳輸線的特性阻抗之間的不匹配會導致反射,并且會產生信號衰減和系統性能下降。

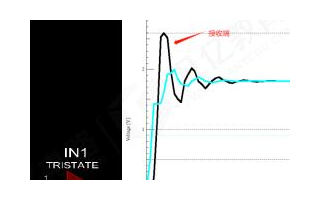

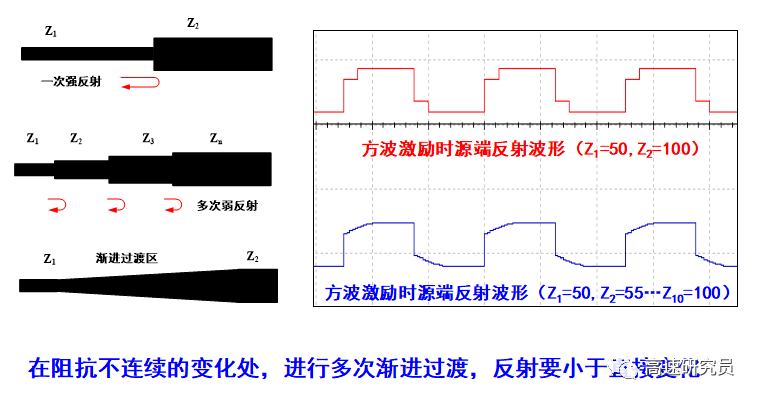

在阻抗匹配時,串聯端接電阻靠近發(fā)送端,可以減少傳輸線末端的反射。當信號從發(fā)送端傳輸到傳輸線末端時,如果負載阻抗與傳輸線的特性阻抗不匹配,就會由于反射而導致信號的部分反射回到發(fā)送端。這種反射會導致信號干擾和失真,并且會降低傳輸線的效率。

然而,如果串聯端接電阻靠近傳輸線末端,反射會更加明顯。這是因為信號在傳輸線上傳播的速度是有限的,而信號的反射需要一定的時間才能回到發(fā)送端。如果串聯端接電阻在傳輸線的末端附近,反射會在傳輸線上往返多次,從而產生更大的干擾。因此,為了減少反射引起的信號失真,串聯端接電阻應該靠近發(fā)送端。

另一個原因是,串聯端接電阻靠近發(fā)送端可以降低傳輸線的負載容量。傳輸線具有一定的電容性質,當信號傳輸到末端時,負載阻抗會與傳輸線的電容串聯形成低通濾波器。這將導致高頻信號的衰減,并且會限制系統的頻率響應。如果串聯端接電阻靠近發(fā)送端,傳輸線的負載容量將減少,高頻信號的衰減將降低,從而提高傳輸線的頻率響應。

此外,將串聯端接電阻靠近發(fā)送端還可以減少信號的串擾。當多個傳輸線并行布置時,信號在相鄰的傳輸線之間可能會引起串擾。如果串聯端接電阻靠近發(fā)送端,信號的引導路徑將更短,并且信號的電磁場干擾范圍將減小,從而減少串擾的可能性。

在實際應用中,將串聯端接電阻靠近發(fā)送端,也可以使系統的調試和維護更加方便。如果串聯端接電阻靠近傳輸線末端,需要在發(fā)送端和傳輸線末端之間添加插入點或切換開關,以便在調試或維護時屏蔽電阻的影響。而將串聯端接電阻靠近發(fā)送端,可以在不影響傳輸線的情況下更容易地接入或調整電阻。

總的來說,傳輸線在阻抗匹配時,串聯端接電阻靠近發(fā)送端是為了減少反射引起的信號失真、降低傳輸線的負載容量、減少信號的串擾,并且便于系統的調試和維護。因此,在實際應用中,我們應該合理地設計和布局傳輸線,以確保串聯端接電阻靠近發(fā)送端。

-

阻抗匹配

+關注

關注

14文章

345瀏覽量

30661 -

傳輸線

+關注

關注

0文章

370瀏覽量

23925

發(fā)布評論請先 登錄

相關推薦

傳輸線在阻抗匹配時串聯端接電阻為什么要靠近發(fā)送端?

傳輸線在阻抗匹配時串聯端接電阻為什么要靠近發(fā)送端?

評論