本文要點

阻抗不匹配會導致并行網絡出現信號反射和不同步現象,從而導致接收器上出現比特錯誤。

要快速識別阻抗超標,需要在 PCB 設計工具中使用規則管理器,然后在設計規則中設置阻抗限制和容差。

布線后仿真工具可用于檢查不符合阻抗規則的網絡,并確定哪些區域的設計應該更改。

走線阻抗控制主要在于確保走線的尺寸大小合適。如果獨立考慮一條走線,其阻抗值是很明確的。但是,當它靠近另一條走線或導體時,由于意外耦合作用,該走線的阻抗將與最初的設計值不同。這個問題非常棘手,會導致沿著互連的阻抗變化不定,而傳輸線和接收器之間的極端阻抗失配將導致信號反射。

盡管我們已根據最佳實踐對 PCB layout 進行了布線,并且布線的走線寬度全部符合設計值,但是互連中也有可能出現阻抗變化。這時就需要使用規則驅動設計,即,在對 layout 進行布線時,根據設計規則來檢查電路板。如果要處理一塊工藝比較陳舊的電路板,那么就需要分批檢查阻抗;為此,可以運行一個批處理設計規則檢查 (DRC),一目了然地瀏覽阻抗超標情況。

通過規則管理來控制阻抗,準確發現信號反射

要糾正整個電路板上的阻抗錯誤,Sigrity 的布線后仿真功能可以助我們一臂之力,用以分析整個單端和差分互連的阻抗。同時,還可以發現互連線上特定位置的信號反射,如過孔或連接器過渡處。在下文中,我們將介紹如何使用 Allegro PCB layout 工具和 Sigrity 分析功能。

定義阻抗控制的規則

阻抗控制的目的是確保 PCB 上的走線在每個互連中的幾何形狀都是一致的。該方法適用于單端和差分對布線。為此,需要遵循我們的高速信號標準來定義這些約束規則,而這些信號標準又取決于所選的器件或設計的接口類型。

PCB 設計軟件的適應性很強,確保用戶能夠定義任何物理和電氣規則,以符合可制造性設計 (DFM) 要求和信號標準。Allegro 提供的設計工具允許用戶使用 Allegro Constraint Manager(規則管理器)來定義所需的阻抗值和容差。此工具可在 Allegro PCB Designer 或 Allegro Sigrity SI 內訪問。

對四個阻抗控制網絡進行分析。

在接下來的例子中,我們將討論如何定義和檢查現有 layout 中一組網絡的阻抗規則。如上圖所示,這四個要檢查的網絡是 DDR3 數據總線的一部分,定義的阻抗是 34 歐姆。此時,我們要檢查這些走線的阻抗是否在 JEDEC 標準的限制范圍內,以及在這些走線上是否會發生過度的信號反射。

定義規則

在開始定義規則之前,我們需要確定規則定義是針對單個網絡,還是針對一組網絡。Allegro PCB Designer 允許用戶將幾個網絡劃分到一個網絡組,因此可以將同一組設計規則分配至整個網絡組。請注意,不是必須要將網絡分配到網絡組;一個網絡也可以有自己的設計規則和約束。所有設計規則都可以在 Allegro Constraint Manager 中訪問、查看和編輯。

要訪問 Allegro Constraint Manager 并定義電路板中的約束規則,請在 Allegro Sigrity SI 中打開 .BRD 文件。單擊 Setup 菜單并找到 Constraints → Constraint Manager。打開 Constraint Manager 后,可以從屏幕左側的面板上訪問基于網絡組和基于網絡的電氣規則。

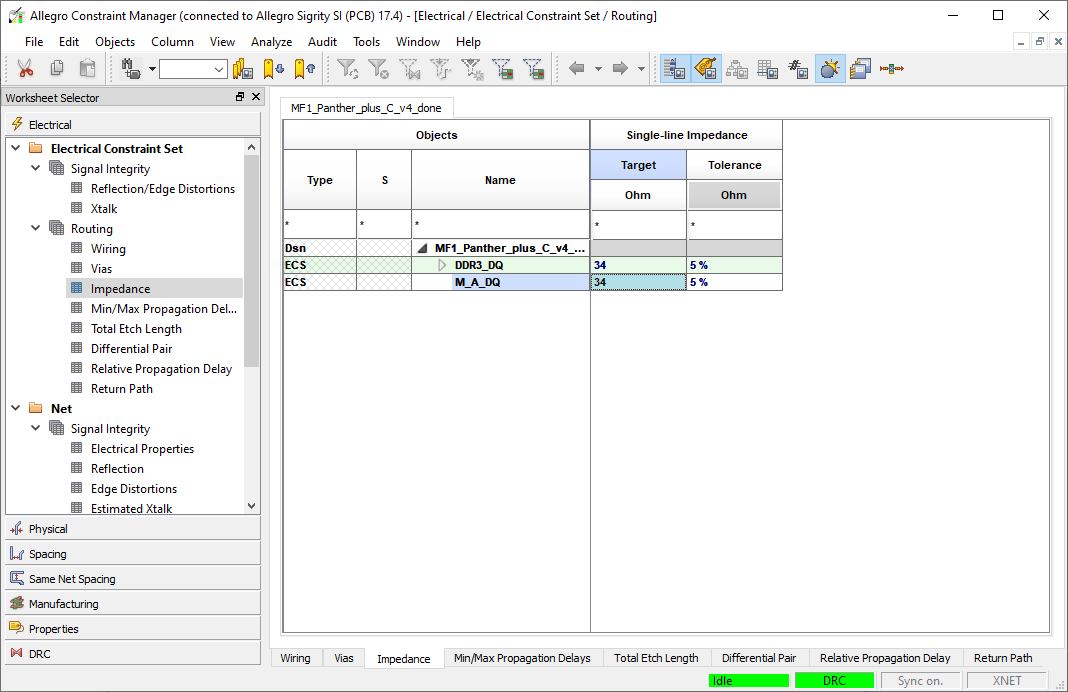

要為一個網絡組設置阻抗規則,請打開 Electrical Constraint Set 選項,然后找到 Routing → Impedance。下圖是在該電路板上定義的兩個網絡組。這兩個網絡組都是 DDR3 接口的一部分,因此該接口上的走線阻抗應該設置為 34 歐姆。阻抗容差設置為 5%。

網絡組的阻抗規則。

我們要檢查的四條走線不屬于這些網絡組,但如有需要,我們可以將這些走線分配到這些網絡組。另一種方法是在 Electrical Constraint Set 中為這些走線單獨定義阻抗規則。為此,只需在 Constraint Manager 中向下滾動到電氣工作表中的 Net 部分。打開 Routing → Impedance 部分后,就可以查看所有的網絡以及它們屬于哪個網絡組。

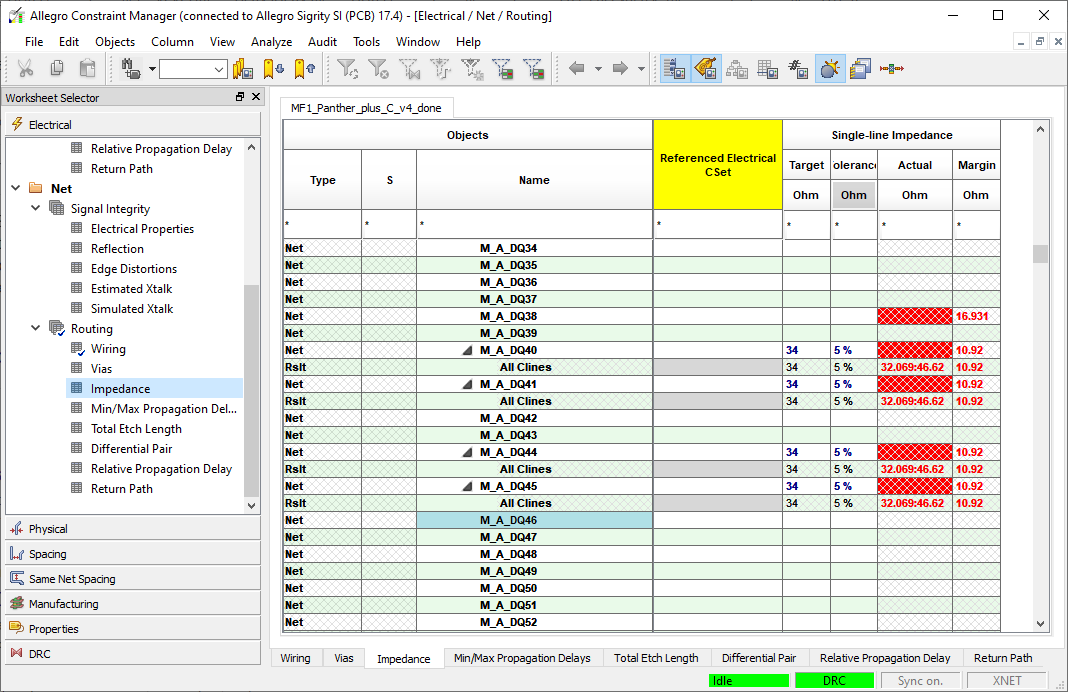

如果我們想把一個網絡分配到電氣規則集,只需在 Referenced Electrical C Set 一欄下打開下拉菜單,選擇所需的電氣規則集。現在,我們要把目標阻抗值分配到要檢查的各個網絡。從下圖中可以看到,目標阻抗設置為 34 歐姆,阻抗容差為 5%。定義目標阻抗值之后,我們就會看到相應的網絡被標記為紅色。如果該網絡沒有立即顯示標記,只需從工具欄運行設計規則檢查(在 Tools 菜單下選擇 Update DRC)。

各個網絡的阻抗規則。

在上圖中,這四個網絡被標記為了紅色,因為它們的最小阻抗和/或平均阻抗超出了 34±5% 的范圍(32.3-35.7 歐姆)。Constraint Manager 顯示,阻抗范圍為 32.069-46.62 歐姆;這些值可能出現在這些網絡的任何位置。造成這種現象的原因包括與其他導體產生意外的寄生耦合、走線寬度不一致,或在參考平面的間隙上進行布線。

請注意,Allegro Constraint Manager 還支持為 PCB 定義其他幾種物理和電氣規則。物理規則包括焊盤和走線間距,而電氣規則包括傳播延遲限制和返回路徑跟蹤。

確定違反設計規則的網絡之后,就可以進一步了解到底是設計的哪些部分導致設計規則超標。另一種查看規則超標的方法是使用工具菜單中的 DRC Browser。該工具可以顯示電路板中超出設計規則的坐標,并在不同的類別中標記出具體的規則超標項目。超標列表可能讓人有點眼花繚亂,但不必擔心,Allegro 提供了可視化工具來顯示規則超標。這涉及到使用 layout 數據進行布線后仿真。

運行阻抗和反射仿真

現在,我們已經準備好糾正電路板中的阻抗失配,要完成此操作,可以使用 Allegro 中的信號完整性分析功能來發現阻抗變化并識別存在反射的位置。

在 Allegro 中打開電路板,點擊 Analyze 菜單,并選擇 Workflow Manager 選項。隨后屏幕上會顯示幾個可供執行的分析,包括 Impedance Workflow 和 Reflection Workflow。

首先,選擇 Reflection Workflow 和要檢查的目標網絡。選擇目標網絡后,點擊 Start Analysis,開始仿真。仿真完成后,可以點擊 Reflection Vision查看熱圖,熱圖中標出了網絡上出現反射的位置。我們也可以點擊 Reflection Table 來查看具體的上沖/下沖值以及它們在電路板上的坐標。在本例中的電路板上處理的是 DDR 線路,因此可以在 Reflection Table 中將這些值與 JEDEC 規范進行比較。

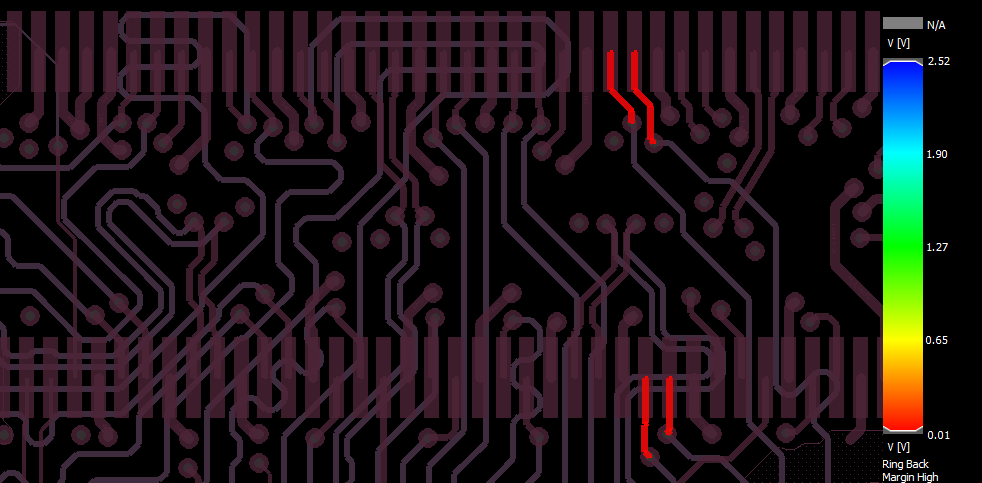

下圖是本例中四個網絡的反射結果。從圖中可以看到,反射主要發生在器件焊盤上。相應的值以紅色標記,并且只產生了約 10 mV 的振鈴現象。在互連上很早就可以看到 30 mV 的振鈴,但用 Reflection Vision 工具不容易進行可視化;需要雙擊阻抗表中的相應條目才能看到這些結果。

Reflection Workflow 結果。

沿著這些網絡出現了 30 mV 的振鈴,它們發生在靠近走線的多個點附近,相應的走線片段如之前的圖片所示。Impedance Workflow 分析有助于理解這些反射現象,它們是由沿互連線的阻抗變化而引起的,以可視化的方式查看會更為直觀。

要檢查阻抗變化,請選擇分析工具欄中的 Impedance Workflow 選項。選擇相同的網絡進行分析并運行仿真。選擇 Impedance Vision 選項,可以查看整個互連的阻抗,同時也會顯示熱圖,其中阻抗值以不同的顏色表示。

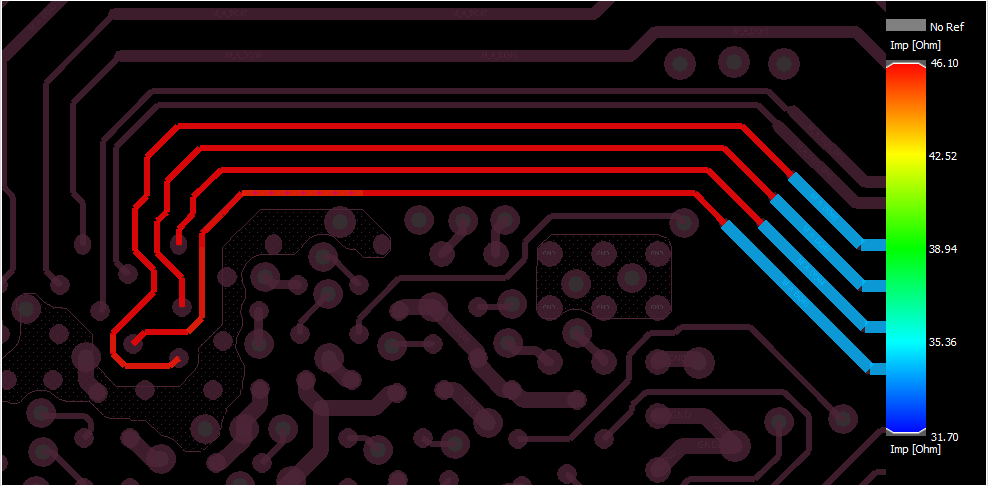

四個網絡的阻抗變化。

從圖中我們可以直接看到,阻抗從約 46 歐姆突然過渡到約 34 歐姆,和 Allegro Constraint Manager 中顯示的數據相同。從紅色部分和藍色部分之間的長度變化可以明顯看出這一點。這對應于網絡中具有較高上沖的區域。下一步是將信號上沖和阻抗變化與信號標準進行比較。這些網絡的紅色部分對應 FPGA 上的 BGA 扇出部分,所以要限制扇出部分的寬度,防止出現過度的信號反射和損失。

我們可以采用與上文相同的仿真步驟來檢查電路板中的不同網絡對。只需選擇網絡對的兩端,確保整個電路板的差分阻抗保持一致。對于差分對,還需要檢查是否符合長度匹配容差,該容差可以在 Allegro Constraint Manager 中定義。然后可以使用 DRC Browser 來確定哪里發生了長度失配的情況,布線工具可以對標準的長度匹配片段進行布線,保持差分對同步。

本文轉載自: Cadence楷登PCB及封裝資源中心微信公眾號

審核編輯 黃宇

-

pcb

+關注

關注

4318文章

23022瀏覽量

396428 -

阻抗

+關注

關注

17文章

941瀏覽量

45834 -

高速設計

+關注

關注

0文章

23瀏覽量

11418

發布評論請先 登錄

相關推薦

解決高速PCB設計EMI(電磁干擾)的九大規則

高速PCB布線技巧、EMI問題、設計規則

EMI問題可以通過高速PCB來控制解決嗎

高頻高速PCB設計中的阻抗匹配,你了解多少?

如何用S12ZVM來控制高速電機(三)

如何用S12ZVM來控制高速電機(一)

如何用S12ZVM來控制高速電機(二)

如何通過高速PCB來控制EMI問題

高速信號的走線閉環規則

如何在高速設計中通過規則管理來控制阻抗

如何在高速設計中通過規則管理來控制阻抗

評論