作者: Paul McLellan,文章來源: Cadence楷登PCB及封裝資源中心微信公眾號

在去年的IEEE 電子設計流程研討會(IEEE Electronic Design Process Symposium,即EDPS)上,Cadence 資深半導體封裝管理總監 John Park 先生進行了一場關于 3DHI(即 3D 異構集成)挑戰的演講。Cadence 大多數人的從業背景都是 IC 設計或 PCB 設計,而 John 則有著豐厚的封裝背景。在過去的幾年里,這一直是一個相對較小的領域,但卻在幾乎一夜之間成為了半導體業界最受關注的話題之一。

此次 IEEE 電子設計流程研討會持續了一周時間,期間涵蓋各項會議討論,包括 Samsung Foundry Forum、Samsung SAFE 和 PCB West 等。

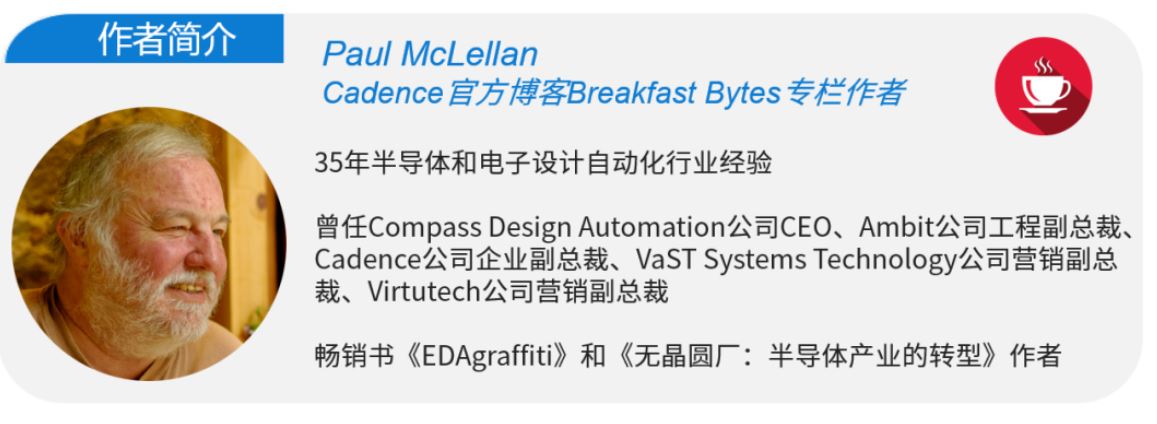

上述所有會議討論的最大驅動因素是經濟考慮,但要展開全面的分析需要大量的價格信息;這些信息并不容易獲得,而且一直在不斷變化。最明顯的是某個特定尺寸的裸片在特定工藝下的成本,還有不同的多裸片封裝技術的成本。在過去的幾年里,3D 封裝技術已經足夠普及,成本似乎已經降到足夠低,可以得到更廣泛地使用。晶圓成本隨著每個工藝節點的增加而上升,這意味著設計一個大型系統級芯片與把多個裸片放入一個封裝之間的權衡因素已經改變,并將繼續改變。

John Park 在演講一開始就總結了目前的形勢:

無論是技術上還是成本上,遵循摩爾定律已不再是最佳選擇。

成本的主要驅動因素之一是良率,而大裸片的良率要低于總面積相同的兩個(或更多)小裸片。這是因為,大裸片更難避免晶圓上的各個缺陷。另一個重要的驅動因素是通過采用不同的工藝制作不同的裸片(如模擬和射頻)來優化設計的能力,只用最先進的工藝節點制作價值最高的數字邏輯部分。還有一個挑戰則是如何將足夠多的電子元件裝入外形尺寸非常小的設備,如智能手表。舉例來說,此類設備可能在垂直方向有空間擺放元件,但在水平方向沒有足夠空間。

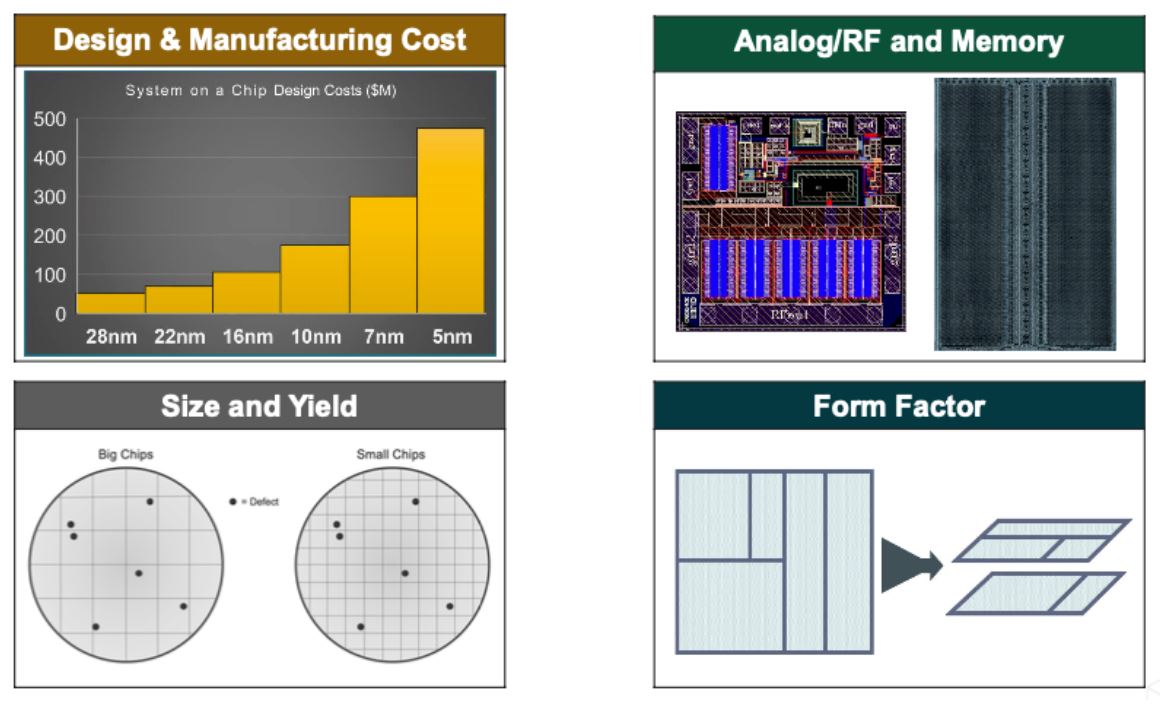

從系統級芯片到異構集成的過渡實際上是在兩個方向進行的。一個方向是避免在 PCB 上放置大量封裝,而是將這些封裝中的裸片置于一個單一的多芯粒設計中。這種方法的優點是面積尺寸更小,構造更簡單,帶寬 I/O 更高,并且功耗更低。

另一個方向是將一個大型系統級芯片分解成獨立的裸片,分別進行制造,然后再將其集成到一個單一的封裝中。這種方法的 NRE 成本較低,能夠加快產品上市,可以突破光刻極限,實現尺寸更大的設計,并且 IP 使用模式更加靈活。

當然,這并不是什么新鮮事。30 多年來,我們一直擁有各種形式的多芯片模塊 (MCM)。但它們非常昂貴,而且通常只用于搭建雷達等專門用途。現在有了更豐富的技術組合(見下圖)——

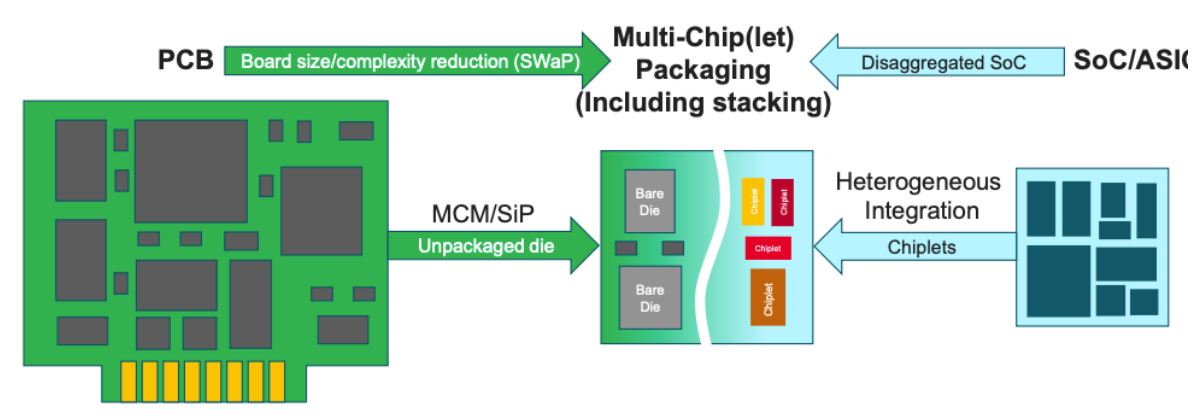

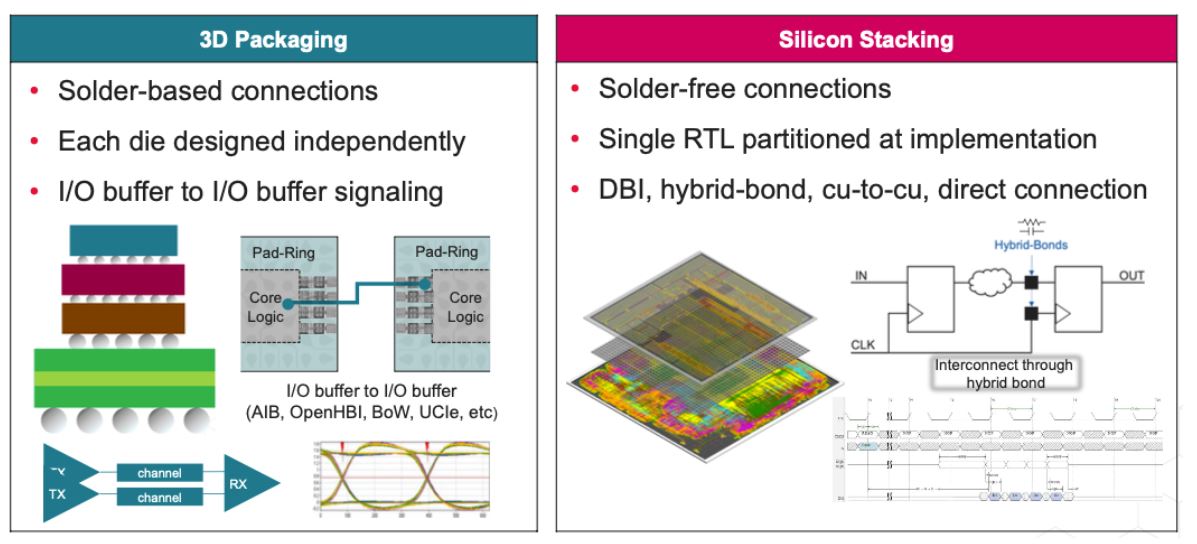

上圖左邊是可用于“常規”裸片的封裝技術,即沒有任何硅通孔 (TSV) 的裸片;右邊是硅堆疊技術,使用沒有任何 bump 的銅-銅直接鍵合;中間是在 2.5D 中介層上的裸片混合結構,或稱為扇出型晶圓級封裝 (FOWLP) 的超高密度封裝。對于左邊和右邊的技術,各自需要進行的設計有很大的不同。

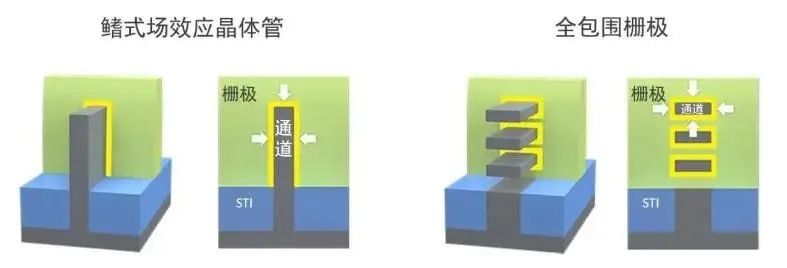

3D 封裝(與硅堆疊不同)使用基于焊點的連接 (bump),每個裸片都是獨立設計的,信號傳遞通過 I/O 緩沖器完成,與 PCB 上的封裝技術類似。而硅堆疊的連接則不通過焊點,設計是一個單一的 RTL,在物理互連過程中進行切割分劃。

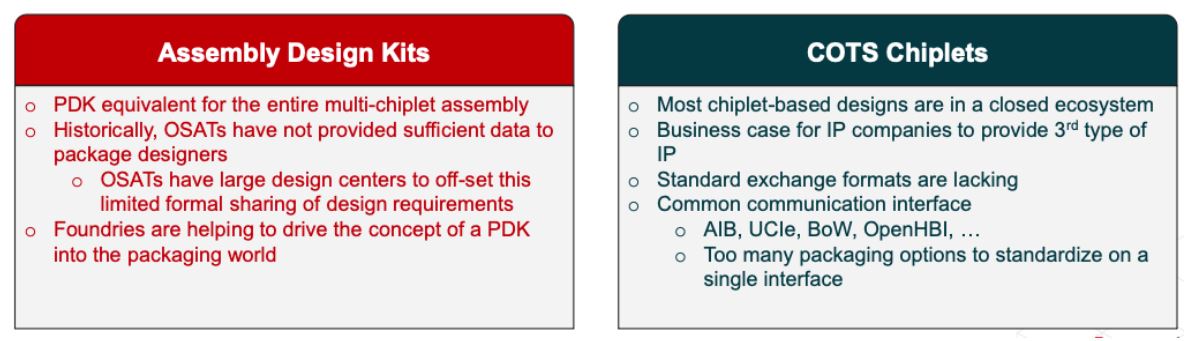

在演講中,John 一直在強調的一點是需要使用組裝設計套件 (Assembly Design Kits,即ADK)。這相當于我們所熟悉的用于集成電路設計的 PDK。一直以來,封測代工廠 (OSAT) 要么沒有,要么不愿意披露封裝設計師需要的所有數據。但是代工廠多年來一直存在這個問題——他們需要提供 PDK,但許多原始數據是保密的。

如果有一天出現了芯粒的“零售”市場,我們就需要落實更多的標準化程序(如 UCIe 或 OpenHBI)。如今,除了使用 HBM(高帶寬存儲器)外,多芯粒設計是由一家公司設計完成的,所有芯粒在同一個設計中一起工作,或者,允許芯粒在一些不同的設計中進行配置,這些設計分別具有不同的特征(如性能、價格等)。

更多ADK信息,請閱讀《封裝組裝設計套件 ADK 及其優勢》。

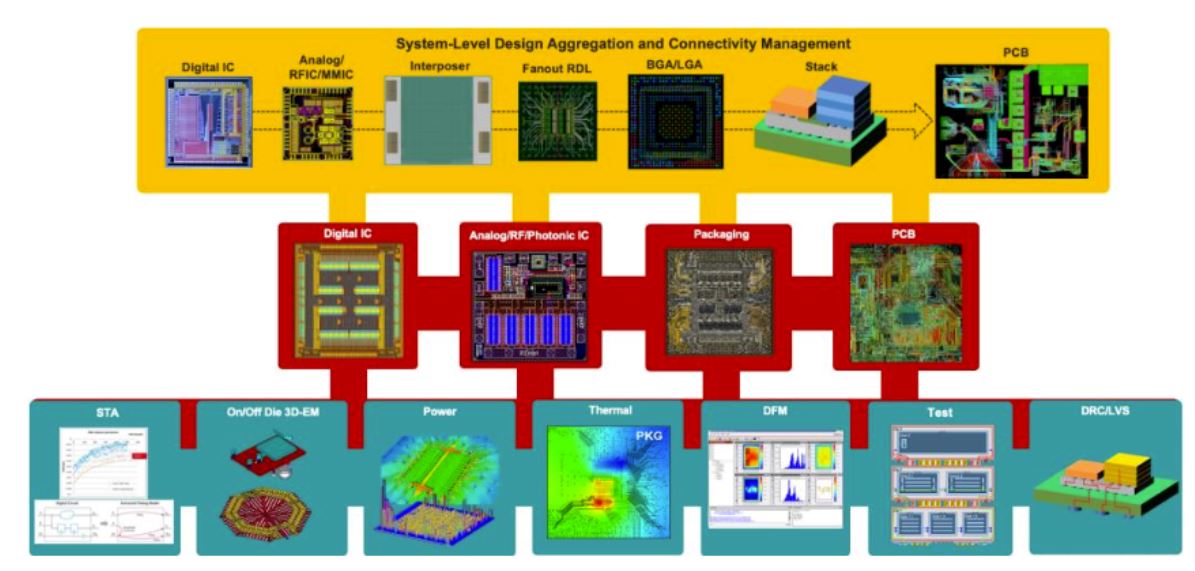

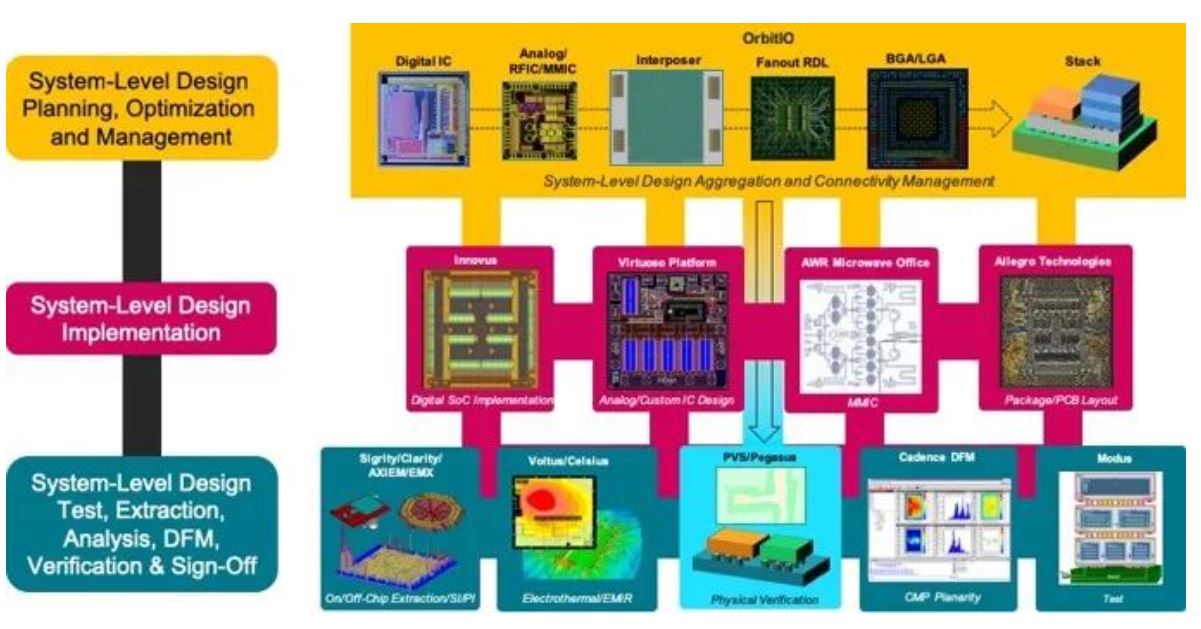

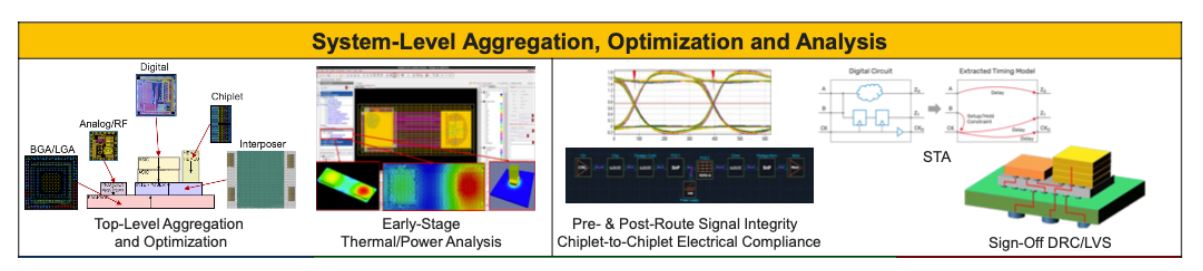

在設計方面,即使用幾個或許多裸片來設計整個系統,最大的要求是為整個 3D-IC 建立一個共同的數據庫:芯片、芯粒、tile、封裝、PCB,甚至可能還包括連接器和背板。顯而易見,這些設計的尺寸可能非常大,有數十億甚至數百億個器件(當然,更大的設計一直層出不窮)。下面的圖表介紹了在進行這些設計時可能涉及的大量工具。

對此,Cadence 有以下產品幫助設計出色完成:

在一個封裝中放置多個裸片的最后一個挑戰是“已知良好裸片(Know Good Die,即KGD)”。這意味著在組裝前需要對芯粒進行廣泛的測試(可能是在晶圓分類時),以確保它們通過測試。如果對封裝中某個裸片的測試稍有疏忽,就有可能讓某個不良裸片蒙混過關,白白浪費了封裝成本。由于芯片是壞的,與之一同付諸東流的還有芯片的生產與組裝成本。一旦把多個裸片放置在一個封裝中,就不是這么一回事了。如果有四個裸片,在最后測試時才發現了其中一個不良裸片,那么其結果不僅損失了一個裸片,還浪費了三個良好的裸片(此時假設沒有辦法打開封裝,也無法以較低的成本完好無損地取回良好的裸片;雖然有時也并非如此)。

審核編輯 黃宇

-

芯片

+關注

關注

450文章

49643瀏覽量

417250 -

3D系統

+關注

關注

0文章

5瀏覽量

5629

發布評論請先 登錄

相關推薦

3D封裝熱設計:挑戰與機遇并存

裸眼3D筆記本電腦——先進的光場裸眼3D技術

3D IC半導體設計的可靠性挑戰

電柜3D布局需要滿足哪些條件?

當芯片變身 3D系統,3D異構集成面臨哪些挑戰

當芯片變身 3D系統,3D異構集成面臨哪些挑戰

評論