本文要點

將 PDN阻抗設計為目標值有助于確保設計的電源穩定性。

PDN 目標阻抗在一定程度上會決定 PDN 上測得的任何電壓波動。

確定目標阻抗需要考慮 PDN 上允許的電壓波動、輸出信號上允許的抖動,或將兩者都考慮在內。

阻抗可能是用于普遍概括電子學所有領域信號行為的一項指標。在 PCB 設計中設計具體應用時,我們總是有一些希望實現的目標阻抗,無論是射頻走線、差分對,還是阻抗匹配網絡。要想確保電源完整性,就要按照 PDN 目標阻抗進行設計,但如何確定 PDN 目標阻抗是一項不小的挑戰。

而遺憾的是,沒有哪一項行業標準(甚至產品手冊中也沒有提供一定的規范)可以告訴我們,在 PCB 中實現電源完整性所需的目標阻抗是多少。為此,我們需要針對信號行為、允許的功率波動、甚至 PDN 的拓撲結構來確定最低要求。

1. 對于電源完整性而言,合適的目標阻抗是多少?

去耦電容有助于達到目標阻抗并保持電源完整性

不能想當然地認為任何 PDN 都需要一個特定的目標阻抗水平,因為事實并非如此簡單。我們需要選擇的阻抗值取決于幾個因素,而且根據 PDN 的結構,可能很難確定哪些因素最為重要。影響目標阻抗值的主要因素包括:

電源總線上允許的電壓波動

輸出信號上允許的時序抖動

數字 IC 中的核心和邏輯電平

流入 PDN 的電流大小和帶寬

PDN 是數字的還是模擬的

PDN 的拓撲結構

要確定電源完整性的目標阻抗,有兩種最常見的方法,即考慮上述列表中的前兩項。雖然該列表中的所有要點都是相互關聯的,但前兩項通常用于確定 PDN 目標阻抗的設計目標。

最小電壓波動的目標阻抗

需要一定的電壓波動才能讓一定量的電流流入 PDN,而產生電壓波動所需的目標阻抗可以由歐姆定律確定。如果知道了允許的電壓波動和開關期間的總電流消耗,就可以計算出與這兩個值有關的 PDN 阻抗。

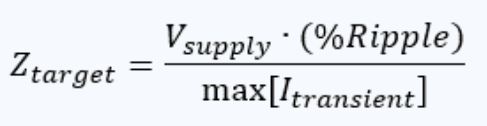

PDN 目標阻抗方程

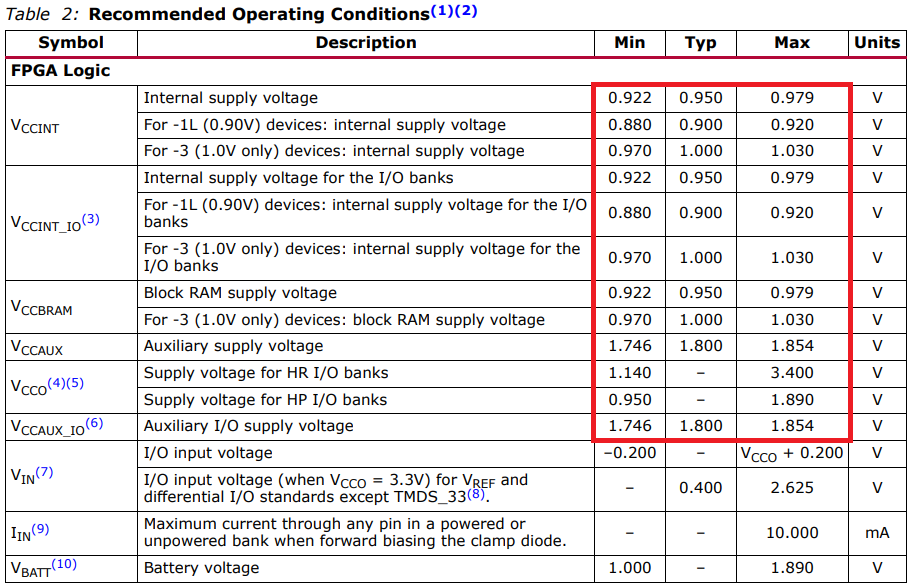

舉個例子,只要翻閱一下主處理器的數據手冊就可以確定限值。下圖所示為 Kintex UltraScale FPGA 的電源電壓數據。我們可以根據數據表中列出的電源電壓的標稱值、最小值和最大值(見下面的紅框),對電源軌電壓的波動設定一個限制。

某大型 FPGA 的電源電壓數據

例如,在第一行中,如果我們考慮到 VCCINT 內部電源電壓有 20% 的安全裕度,我們可以將允許的電源軌電壓波動設置從 0.927 V 到 0.974 V。接下來,在產品手冊中找到開關期間的電流消耗,并使用歐姆定律來確定設計中的 PDN 目標阻抗。只要該電源軌的 PDN 阻抗在整個信號帶寬內低于目標值,那么任何電壓波動都可以最小化。

最小抖動的目標阻抗

確保抖動最小化是一個重要的目標,有時也可用來確定 PDN 的目標阻抗。當一個數字器件進行開關操作并導致電源總線上的電壓波動時,器件中不斷變化的邏輯電平會導致信號中的時序和上升速率發生波動。顯然,這兩者相互依存,并創造了一個有趣的反饋系統,但要使抖動最小化,就必須使這種電源波動最小化。

抖動的典型值可以從 10ps/mV 到 100ps/mV(對于某些邏輯電路而言)不等。高精度時序和測量應用需要將抖動降低至 1 ps/mV。這方面的例子包括點云成像應用,如激光雷達、4D 雷達和其他電子光學應用。

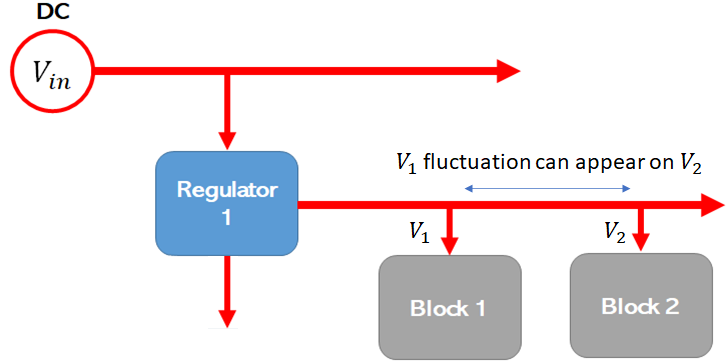

拓撲結構

PDN 的拓撲結構也會影響目標阻抗,但并不是以我們預期的方式。典型 PCB 中的 PDN 可以有一個多總線拓撲結構。在這種拓撲結構中,通常有一個初級穩壓器,將輸入電壓降至高邏輯電平 (5V),并將電源分支至總線。總線上也會放置其他穩壓器,用于繼續降低電壓。詳見下面方框圖中的示意圖。

典型的 PDN 拓撲結構,一條電源總線上有多個電路模塊

每個總線段上的不同電路模塊和器件可以相互影響,這意味著由一個器件引起的 PDN 上的干擾可以傳播到所有其他器件。這可以用 Z 參數矩陣來量化,它也稱為阻抗參數矩陣。從該矩陣可以全面了解 PDN 阻抗,以及流入 PDN 某部分的電流如何在其他部分產生紋波。3D 電磁場求解器可用于確定網絡參數矩陣,并在開始原型設計之前評估電路板的電源完整性。

2. 努力降低 PDN 阻抗

一般來說,無論 PDN 的拓撲結構如何,我們都應該努力在所需帶寬內將 PDN 阻抗降至最低。把 PDN 阻抗降到零是不可能的,但如果能把 PDN 阻抗降到毫歐級別,達到 GHz 級頻率,那么設計就會非常順利。如果使用大量具有不同 ESL 值的去耦電容和相鄰平面,將有助于降低 PDN 阻抗,從而使電源總線電壓波動和輸出信號的抖動保持在一個較低的水平。

在所有設計挑戰中,目標阻抗只是電源完整性的一個方面。Cadence Sigrity X 軟件可以幫助我們評估設計中的電源完整性,并提供了一整套時域和頻域仿真功能,以確定目標阻抗是否需要降低。Sigrity X 提供了一系列可以用于 PDN 阻抗分析的仿真功能,在全面評估系統功能并確保電源完整性上助您一臂之力。

文章來源:Cadence楷登PCB及封裝資源中心

審核編輯 黃宇

-

電源

+關注

關注

184文章

17584瀏覽量

249485 -

阻抗

+關注

關注

17文章

940瀏覽量

45819 -

PDN

+關注

關注

0文章

83瀏覽量

22685

發布評論請先 登錄

相關推薦

搞定電源完整性,不如先研究PDN

如何確定目標阻抗以實現電源完整性?

如何確定目標阻抗以實現電源完整性?

評論