隨著高性能半導(dǎo)體需求的不斷增加,半導(dǎo)體市場越來越意識到“封裝工藝”的重要性。 順應(yīng)發(fā)展潮流,SK海力士為了量產(chǎn)基于HBM(High Bandwidth Memory,高帶寬存儲器)的先進封裝產(chǎn)品和開發(fā)下一代封裝技術(shù),盡力確保生產(chǎn)線投資與資源。一些曾經(jīng)專注于半導(dǎo)體存儲器制造技術(shù)的企業(yè)也紛紛布局封裝技術(shù)領(lǐng)域,其投資力度甚至超過專攻此類技術(shù)的OSAT1(外包半導(dǎo)體組裝和測試)公司。這是因為,越來越多的企業(yè)深信封裝技術(shù)將會成為半導(dǎo)體行業(yè)及企業(yè)未來的核心競爭力。

1 OSAT(Outsourced Semiconductor Assembly and Test, 外包半導(dǎo)體組裝和測試):專門從事半導(dǎo)體封裝和測試業(yè)務(wù)的公司。

本文將以易于理解的語言來闡述封裝技術(shù),幫助公眾不再因為復(fù)雜難懂而對這項技術(shù)望而卻步。文章將探究封裝技術(shù)的意義、作用和演變過程,并探討SK海力士封裝技術(shù)的發(fā)展歷程以及由此引發(fā)的當(dāng)下對異構(gòu)集成的關(guān)注。最后,本文也將介紹SK海力士的未來技術(shù)發(fā)展方向。

封裝技術(shù)的意義和作用

首先,我們來看封裝工藝的四項主要功能。第一也是最基本的,保護半導(dǎo)體芯片免受外部沖擊或損壞。第二,將外部電源傳輸至芯片,以確保芯片的正常運行。第三,為芯片提供線路連接,以便執(zhí)行信號輸入和輸出操作。第四,合理分配芯片產(chǎn)生的熱量,以確保其穩(wěn)定運行。近來,散熱(Heat Dissipation)或熱分配功能的重要性與日俱增。

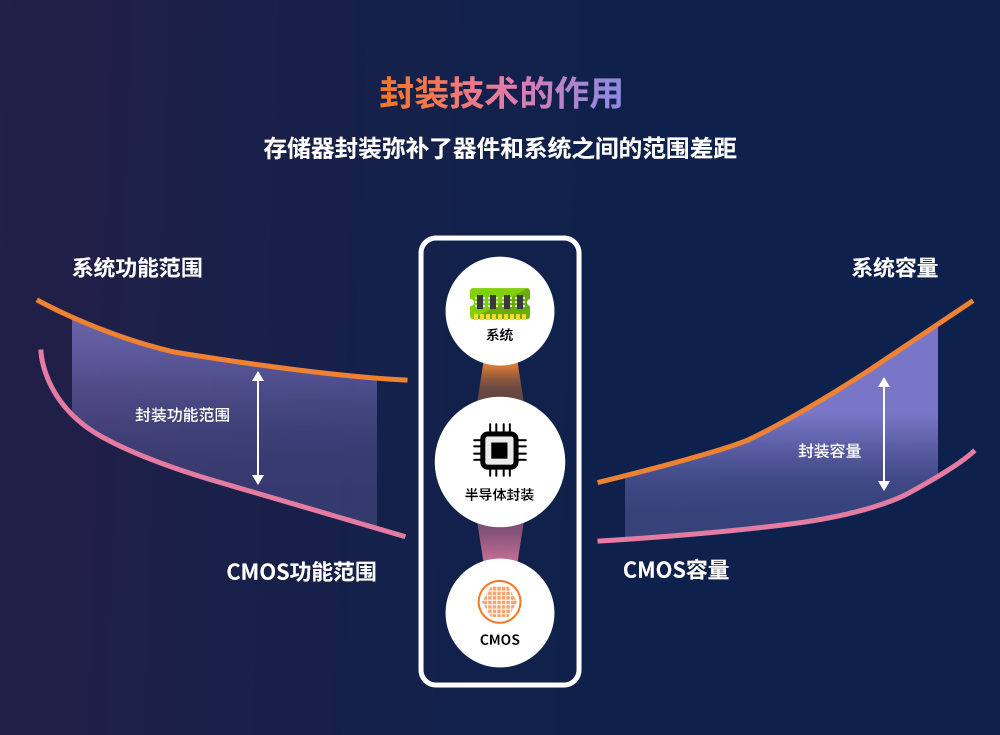

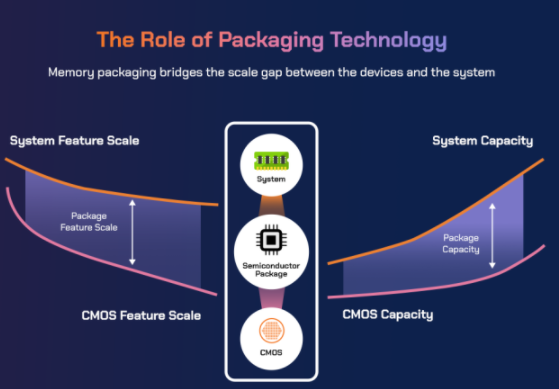

封裝的作用如圖1所示。例如,系統(tǒng)所需功能范圍與CMOS2(互補金屬氧化物半導(dǎo)體)提供的功能范圍之間存在顯著差距,但可通過封裝技術(shù)進行彌補。同樣,系統(tǒng)所需容量(Density)和CMOS提供的容量之間也存在差距,而這一問題也可借助封裝工藝加以解決,因為封裝工藝可提升密度(Density-up)從而提高CMOS的容量。換句話說,封裝技術(shù)充當(dāng)著半導(dǎo)體器件(device)與系統(tǒng)之間的橋梁。因此,這種連接方法變得越來越重要。

2 CMOS(Complementary Metal Oxide Semiconductor, 互補金屬氧化物半導(dǎo)體):一種集成電路設(shè)計,應(yīng)用于使用半導(dǎo)體技術(shù)的印刷電路板(PCB)。

圖1. 存儲器封裝彌補了器件和系統(tǒng)之間的范圍差距

封裝技術(shù)發(fā)展的三個階段:堆疊競爭、性能競爭、整合

封裝技術(shù)的發(fā)展歷程可以劃分為三個主要時期。過去,一個封裝中只包含一個裸片。因此,封裝操作比較簡單,也沒有任何差異化因素,封裝技術(shù)的附加價值較低。然而,到了20世紀(jì)初,隨著向FBGA3(細(xì)間距球柵陣列)的轉(zhuǎn)變,多芯片堆疊封裝技術(shù)開始盛行。這一時期可以被稱為“堆疊競爭時期”。由于可以將芯片相互堆疊,因此封裝形式變得更加多樣化,還根據(jù)存儲器芯片的不同組合開發(fā)了各類衍生產(chǎn)品。MCP4(多芯片封裝)也出現(xiàn)在這一時期,該技術(shù)可以將DRAM和NAND集成在同一封裝中。

3 FBGA(Fine-pitch Ball Grid Array, 細(xì)間距球柵陣列):一種基于球柵陣列技術(shù)的集成電路表面貼裝型封裝(芯片載體)形式。其觸點更薄,主要用于系統(tǒng)級芯片設(shè)計。

4 MCP(Multi Chip Package, 多芯片封裝):通過在一個封裝外殼內(nèi)垂直堆疊兩種或兩種以上不同類型存儲器半導(dǎo)體形成的產(chǎn)品。

第二個時期始于2010年之后,當(dāng)時出現(xiàn)了一種利用芯片凸塊(Bump)的互連(Interconnection)方法。因此,運行速度和器件屬性裕度(Margin)發(fā)生了變化。這一時期可以稱為“性能競爭時期”,因為在2010年之前,封裝技術(shù)通常涉及金屬線連接,而凸塊的引入縮短了信號路徑(Signal Path),提高了速度。同時,采用TSV5(硅通孔)技術(shù)的堆疊方法大幅增加了I/O(輸入/輸出)數(shù)量,可連接10246 個wide I/O,即使在低電壓狀態(tài)下也可實現(xiàn)高速運行。在性能競爭時期,芯片性能依據(jù)封裝技術(shù)而異,這成為滿足客戶要求的重要因素。由于封裝技術(shù)可能影響企業(yè)的成敗,因此封裝技術(shù)的價值持續(xù)增長。

第三也是最后一個時期始于2020年,是在先前所有封裝技術(shù)的基礎(chǔ)上發(fā)展起來的。這一時期可以被稱為“整合時期”,需要借助技術(shù)將各類芯片集成到同一封裝內(nèi),還需要在整合系統(tǒng)時將多個部分連接至同一模塊。在這一時期,封裝技術(shù)本身已成為一種系統(tǒng)解決方案,可為客戶提供定制化的封裝解決方案,來實現(xiàn)小批量生產(chǎn)。從這一點來說,封裝技術(shù)將成為決定企業(yè)成敗的關(guān)鍵因素。

5 TSV(Through-Silicon Via, 硅通孔):一種在DRAM芯片內(nèi)鉆數(shù)千個細(xì)孔并通過垂直貫通的電極將上下兩層的通孔連接在一起的互聯(lián)技術(shù)。

6 1,024:標(biāo)準(zhǔn)DRAM最多包含64個I/O,而HBM3最多包含1024個wide I/O。

圖2. 封裝技術(shù)發(fā)展帶來的變化

SK海力士封裝技術(shù)的發(fā)展歷程

直到堆疊競爭時期,SK海力士的封裝技術(shù)并未表現(xiàn)出顯著優(yōu)勢;而隨著性能競爭時期的到來,SK海力士的封裝技術(shù)開始在市場中嶄露頭角。CoC(芯片內(nèi)建芯片)7技術(shù)表現(xiàn)尤為突出,這項技術(shù)將凸塊互聯(lián) (Bump Interconnection)與引線鍵合(Wire Bonding)相結(jié)合,在提高運行速度和降低成本方面實現(xiàn)了突破。如今,該技術(shù)已專門應(yīng)用于SK海力士高密度模塊的生產(chǎn)和量產(chǎn)。SK海力士還開發(fā)了MR-MUF(批量回流模制底部填充)8技術(shù)并將其應(yīng)用于HBM產(chǎn)品中。通過這項技術(shù)確保了HBM 10萬多個微凸塊互連的優(yōu)良質(zhì)量。此外,該封裝技術(shù)還增加了散熱凸塊的數(shù)量,同時由于其采用具有高導(dǎo)熱性的模制底部填充材料,與競爭產(chǎn)品相比具有更加出色的散熱性能。這項技術(shù)的應(yīng)用鞏固了SK海力士在HBM市場的地位,并使SK海力士在HBM3市場占據(jù)領(lǐng)先地位。

7 CoC(Chip-on-Chip, 芯片內(nèi)建芯片):是指在不使用TSV(硅通孔)技術(shù)的情況下,以電氣方式連接兩個(或以上)die的封裝技術(shù)。

8 MR-MUF(Mass Reflow Molded Underfill, 批量回流模制底部填充):將半導(dǎo)體芯片貼附在電路上,并在堆疊芯片時使用“EMC (Epoxy Molding Compound, 液態(tài)環(huán)氧樹脂模塑料”填充芯片之間或芯片與凸塊之間間隙的工藝。截至目前,NCF技術(shù)已經(jīng)用于該工藝。NCF是一種在芯片之間使用薄膜進行堆疊的方法。MR-MUF與NCF相比,導(dǎo)熱率高出兩倍左右,對工藝速度和良率都有很大影響。

在如今的融合時期,SK海力士正積極發(fā)展混合鍵合(Hybrid Bonding)技術(shù),這種技術(shù)采用Cu-to-Cu(銅-銅)鍵合9替代焊接。此外,SK海力士也在研究采用Fan-out RDL(扇出型重新分配層)技術(shù)10等各種封裝技術(shù)的方案。混合鍵合技術(shù)可以進一步縮小間距11,同時作為一種無間隙鍵合(Gapless Bonding)技術(shù),在芯片堆疊時不使用焊接凸塊(Solder Bump),因此在封裝高度上更具優(yōu)勢。此外,扇出型RDL技術(shù)適用于多個平臺,SK海力士計劃將該技術(shù)用于芯粒(Chiplet)12技術(shù)為基礎(chǔ)的集成封裝。線間距(Line Pitch)和多層(Multi-Layer)是扇出型技術(shù)的關(guān)鍵組成部分,SK海力士計劃到2025年將確保1微米以下或亞微米(Sub-micron)級水平的RDL技術(shù)。

9 Cu-to-Cu(Copper-to-Copper, 銅-銅)鍵合:封裝工藝的一種混合鍵合方法,可在完全不使用凸塊的情況下將間距縮小至10微米及以下。當(dāng)需要將封裝內(nèi)的die相互連接時,可在此工藝中采用銅-銅直接連接的方法。

10 RDL(Redistribution Layer, 重新分配層):集成電路上形成的額外金屬布線層,旨在重新排列I/O焊盤,將焊盤重塑到所需位置,以便于在必要時操作焊盤。例如,芯片中心的凸塊陣列可重新分配到靠近芯片邊緣的位置。重新分配焊盤有助提高接觸密度,并實現(xiàn)后續(xù)封裝步驟。

11 間距:互連線之間中心到中心的最小距離

12 芯粒:該技術(shù)使用控制器或高速存儲器等將芯片分開,并將它們作為單獨晶圓進行制造,最后在封裝工藝中對它們進行重新連接

圖3. SK海力士最新封裝技術(shù)

封裝技術(shù)將成為提供整體系統(tǒng)解決方案的重要手段,其功能不再局限于原始的芯片保護和電源供應(yīng)等功能。在不久的將來,各公司將依賴封裝技術(shù)助力其成為半導(dǎo)體行業(yè)的領(lǐng)軍者。幾年前,東亞地區(qū)一家大型晶圓代工企業(yè)使用集成式扇出型(Integrated fan-out, InFO)封裝技術(shù)建立起全新的系統(tǒng)級封裝(System-in-Package, SiP)業(yè)務(wù),同時擴大了晶圓代工銷售業(yè)務(wù)范圍。就像這家晶圓代工企業(yè)以生產(chǎn)控制器而聞名,SK海力士以生產(chǎn)HBM等高性能半導(dǎo)體存儲器著稱。SK海力士在整合時期進一步加強異構(gòu)集成和扇出型RDL技術(shù)等先進封裝技術(shù)。不僅作為存儲器IDM(Integrated Device Manufacturer, 垂直集成制造)公司引領(lǐng)業(yè)界,進一步成為引領(lǐng)未來半導(dǎo)體儲存器行業(yè)的“解決方案提供者(Solution Provider)”。

文章來源:SK海力士

審核編輯 黃宇

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

26023瀏覽量

208551 -

封裝

+關(guān)注

關(guān)注

124文章

7529瀏覽量

141935 -

異構(gòu)

+關(guān)注

關(guān)注

0文章

37瀏覽量

12969

發(fā)布評論請先 登錄

相關(guān)推薦

喜訊 | MDD辰達(dá)半導(dǎo)體榮獲藍(lán)點獎“最具投資價值獎”

半導(dǎo)體封裝技術(shù)的可靠性挑戰(zhàn)與解決方案

半導(dǎo)體發(fā)展的四個時代

半導(dǎo)體發(fā)展的四個時代

一文解析異構(gòu)集成技術(shù)中的封裝天線

半導(dǎo)體先進封裝技術(shù)

揭秘DIP:半導(dǎo)體封裝技術(shù)的璀璨明珠

半導(dǎo)體封裝的分類和應(yīng)用案例

先進封裝實現(xiàn)不同技術(shù)和組件的異構(gòu)集成

什么是異構(gòu)集成?什么是異構(gòu)計算?異構(gòu)集成、異構(gòu)計算的關(guān)系?

異質(zhì)集成時代半導(dǎo)體封裝技術(shù)的價值

混合鍵合推動異構(gòu)集成發(fā)展

半導(dǎo)體封裝工藝的四個等級

異構(gòu)集成時代半導(dǎo)體封裝技術(shù)的價值

異構(gòu)集成時代半導(dǎo)體封裝技術(shù)的價值

評論