作者:廣元兄,文章來源:信號完整性學習之路

寫這篇文章的初衷是緣于和做一位多年做SSD產品的人技術交流,對SSD產品PCIe信號走表層這一情況,很是疑惑。

這種疑惑是緣于我之前產品經驗,不管是消費類產品,還是高速產品,在這些產品領域,走線初期規劃,都是默認選擇:高速信號走內層。

這里面有損耗問題,還有表層阻抗問題,還有綠油的問題,這些不穩定因素,是選擇高速信號走內層的原因。

這個多年做存儲產品的人,給的回答竟然是:三星很多大廠都是這樣做的,我們照著做的。一時間無言以對。

那就自己想辦法找找原因。

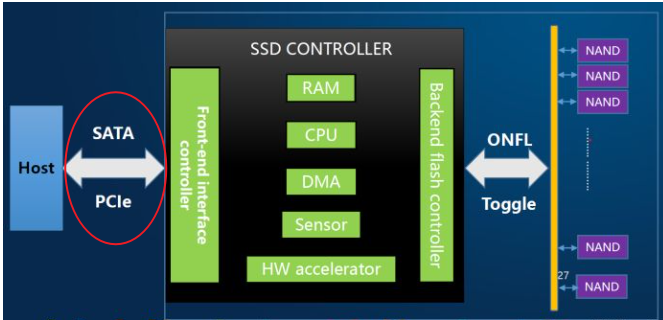

下圖為SSD內部的一個組成框架,三個組件:NAND閃存,控制器及固件。本文不過多地講解這類產品的工作原理,關注的是主控和接口的連接及版圖走線問題。

圖片來源網絡,侵刪

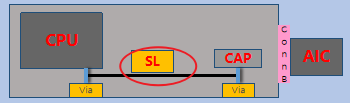

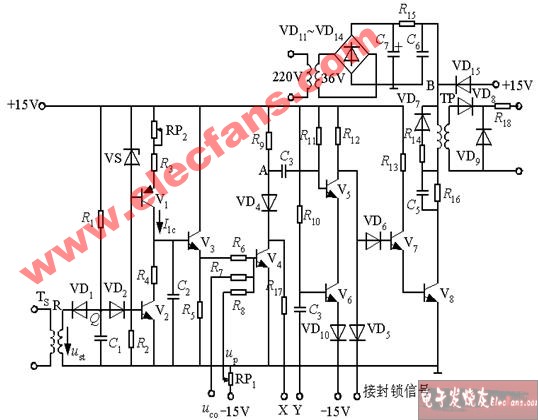

下圖為常見存儲產品表貼情況,也會發現主控和接口的走線連接在表層,這里面看到不僅僅是TX部分因為耦合電容問題,走線走表層,其實接收端RX也在表層。

圖片來源網絡,侵刪

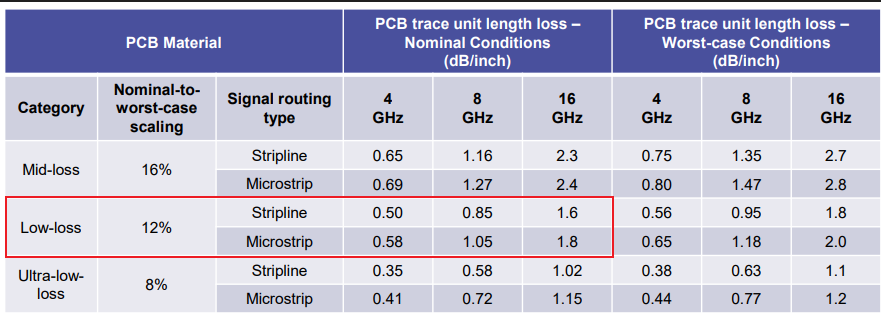

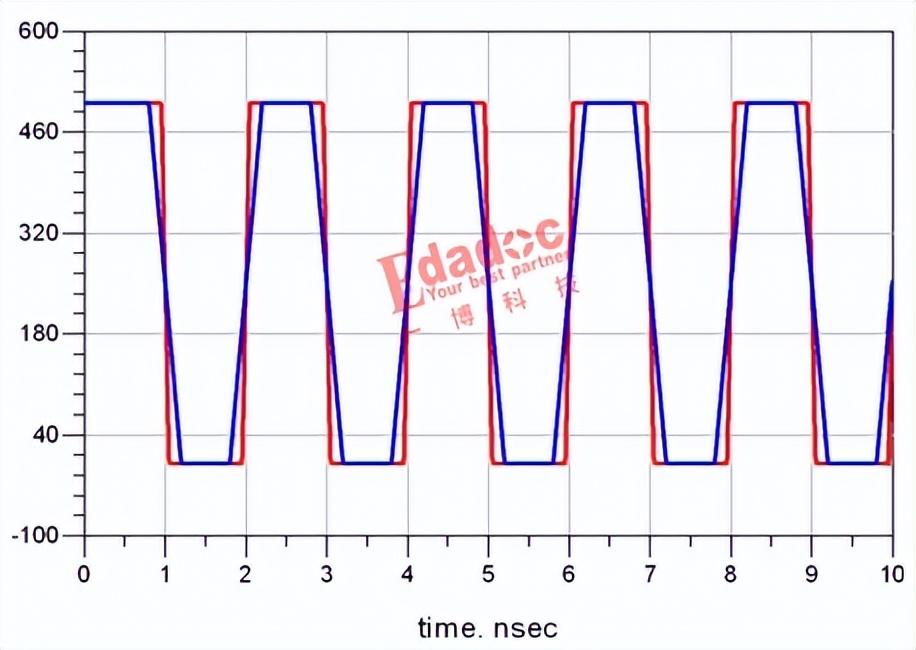

在正常的情況下,Low-loss級別的板材,PCIe Gen4 走線,在表層走線的損耗大于內層的,量化指標值為0.2dB/in,這個值只是用于探討本文的問題,具體的差值需要PCB實測數值來比較,而且每家板廠的工藝和能力是不同的。

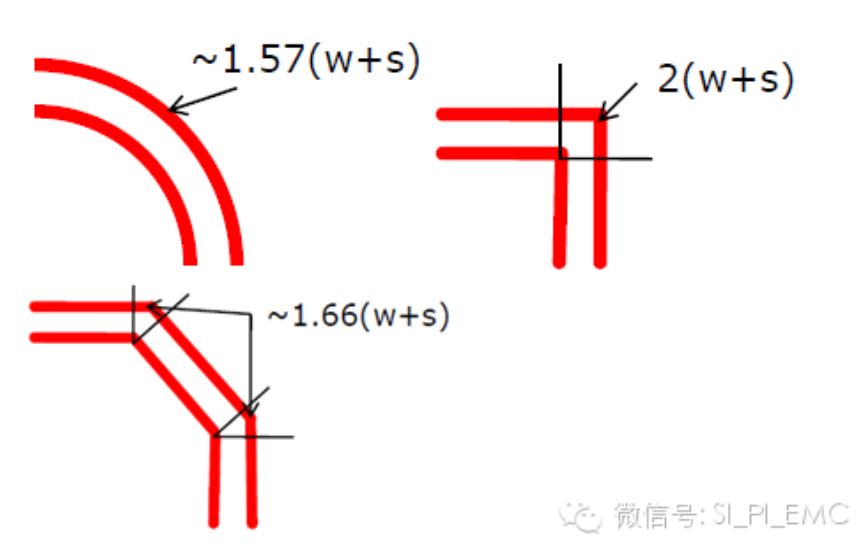

現在的問題就是,走表層和內層的差別是什么?見下圖鏈路結構情況,最直接的差別就是多了兩個過孔:

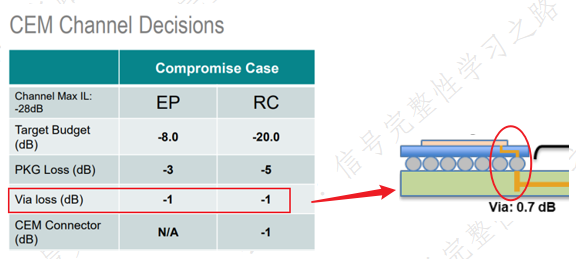

根據相關過孔指標,過孔0.7dB的標準,如果通過殘樁、反焊盤等優化處理,這個數值還可以更小一點,兩個過孔取值為1 dB。

量化為過孔指標,那么兩種走線模式的差別就變成了走線長度的問題,即表層走線(MicroStrip)和內層走線(StripLine)長度差問題。

考慮到表層走線和內層走線的損耗插值是0.2dB/in,兩個過孔的損耗是1dB。這里面可以簡單認為5 inches 是一個標準值。

考慮到存儲產品布線空間,以及相關產品尺寸的限制,一般主控離接口的距離控制在1inch 左右。

圖片來源網絡,侵刪

未來不排除存儲產品的更新換代,性能和尺寸的變更,這個5 inches是一個基準值,這里面還沒有考慮表層走線反射的問題,還有綠油帶來的損耗問題,這些不可量化的因素才是信號完整性解決的關鍵。

兩害取其輕,就目前的情況,選擇走表層也是一個折中優化的選擇。

未來隨著未來存儲產品速率的提升以及產品尺寸的變化,這個值可能是4 inches,也可能是3 inches ,當然不管怎么變,基本的原理不會變,知其然,知其所以然,這才是追求技術的本質。

?免責聲明:本文轉載于網絡,轉載此文目的在于傳播相關技術知識,版權歸原作者所有,如涉及侵權,請聯系小編刪除。

審核編輯 黃宇

-

存儲

+關注

關注

13文章

4266瀏覽量

85687 -

SSD

+關注

關注

20文章

2851瀏覽量

117252 -

高速信號

+關注

關注

1文章

223瀏覽量

17677

發布評論請先 登錄

相關推薦

高速信號為啥要走表層?

高速信號為啥要走表層?

評論